5 MSP430单片机的定时器/计数器

在学习MSP430F249的定时器之前,我们先回顾一下MSP430F249的时钟系统。MSP430F249的基础时钟模块具有3个振荡器,这3个振荡器分别是LFXT1低频振荡器(32768 Hz)、XT2高频振荡器(400 k Hz~16 MHz)和DCO内部数字控制振荡器(约1.1 MHz)。这3个振荡器都可以通过软件设定进行1/2/4/8分频,产生单片机工作需要的3个时钟信号:主时钟MCLK、子系统时钟SMCLK和辅助时钟ACLK。MCLK可以通过编程选择3个振荡器(LFXT1、XT2、DCO)之一,或它们1/2/4/8分频后作为其信号源;SMCLK可以选择2个振荡器(XT2、DCO),或它们1/2/4/8分频后作为其信号源;ACLK只能由LFXT1时钟信号或1/2/4/8分频后作为其信号源。在MSP430F249单片机的大部分内部设备中,都能选择上述3种时钟信号MCLK、SMCLK和ACLK作为时钟源并对上述时钟信号再进行1/2/4/8分频,应用极其灵活。

低频振荡器主要用来降低能量消耗(如使用电池供电的系统),高频振荡器用来对事件做出快速反应或者供CPU进行大量运算。我们可以根据需要选择合适的振荡器,也可以在不需要时关闭一些振荡器,节省功耗。

5.1 看门狗定时器

看门狗定时器WDT实际上是一个特殊的定时器,其主要功能是当单片机软件出现故障(例如外部干扰引起单片机程序跑飞或陷入死循环)时,能使系统重新启动。看门狗定时器的工作原理就是发生故障的时间满足规定的时间后,产生一个非屏蔽中断,使系统复位。当不使用看门狗功能时,看门狗定时器可以作为内部定时器使用。

1)看门狗模式

单片机系统通电后,WDT模块默认为看门狗模式,默认使用内部时钟源DCOCLK,经过32768个时钟周期后(若DCOCLK为1 MHz,则看门狗时间间隔约为32 ms)系统复位。因此,用户使用时,一般在程序中先停止看门狗功能,然后根据要求配置好,再作为看门狗模式或者定时器模式使用。

作为看门狗模式使用时,通过编写程序使WDT的定时时间略大于程序循环执行一次的时间,并且程序执行过程中有对看门狗计数器清零的指令,使计数器重新计数,因此程序正常运行时,就会在WDT定时时间到来之前对WDT清零(俗称定时喂狗),不会产生WDT溢出。如果由于干扰等原因使得程序跑飞,就不会在WDT定时时间到来之前执行WDT清零指令,则WDT就会产生溢出,从而产生系统复位,CPU重新从头开始执行用户程序,这样程序就可以回到正常运行状态。

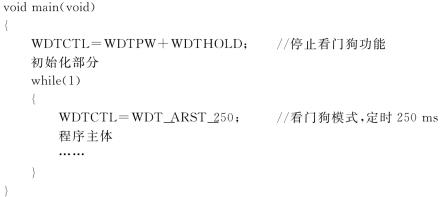

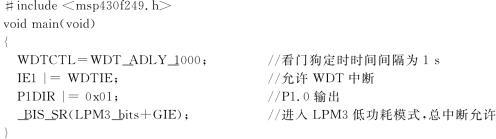

为了说明看门狗模式的工作原理,来分析下列程序片段:

程序说明:在while循环中,设置看门狗时间间隔为250 ms(时钟源为ACLK),同时计数器清零,然后执行程序主体,如此反复执行。如果程序主体执行时间加上所有中断程序执行时间之和小于设定的看门狗时间间隔250 ms,那么程序总是正常进行的;如果系统受到干扰,程序跑飞或陷入死循环,这时在250 ms时间内执行不到WDTCTL=WDT_ARST_250指令,从而看门狗计数器没有被清零,看门狗计数器溢出WDTIFG标志置位,产生PUC复位信号,系统重新启动,这样系统就脱离了死循环状态。

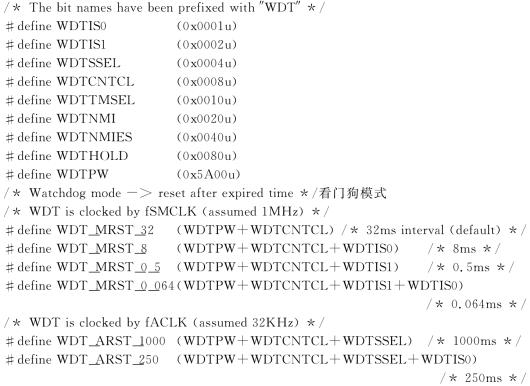

WDTCTL为看门狗控制寄存器,参见看门狗定时器相关寄存器和msp430f249.h头文件。

msp430f249.h头文件放在MSP430集成开发环境IAR软件安装目录下:D:\Program Files\IAR Systems\Embedded Workbench 6.0 Evaluation\430\inc

2)定时器模式

将WDTCTL寄存器的WDTTMSEL置位时,WDT处于定时器模式。当设定的时间间隔一到,中断标志寄存器IFG1中的WDTIFG就会置位,系统复位PUC信号不会产生。如果中断允许寄存器IE1中的WDTIE位和状态寄存器SR中的GIE位都置位,则WDTIFG向CPU请求中断,进入中断服务程序后WDTIFG自动复位。如果未使用中断服务,WDTIFG也可以用软件复位。内部定时器模式与看门狗模式的中断矢量地址是不同的。改变定时器时间间隔时,应该用一条指令同时将WDTCNTCL置位,从而避免发生不期望的PUC复位。

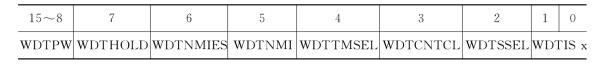

3)看门狗定时器相关寄存器

定时器的控制寄存器如表5-1所示。

表5-1 控制寄存器WDTCTL

PUC 复位后WDTCTL=0x6900。

WDTPW 看门狗定时器访问安全口令,读取时总为0x69,写入时必须为0x5A,否则产生一个PUC信号。

WDTHOLD 看门狗暂停位,置0时看门狗定时器正常工作;置1时看门狗定时器停止工作。

WDTNMIES NMI边沿选择位,置0时上升沿触发NMI中断;置1时下降沿触发NMI中断。

WDTNMI 复位引脚和NMI选择位,置0时RST/NMI引脚为复位端;置1时RST/NMI引脚为边沿触发的非屏蔽中断输入。

WDTTMSEL 看门狗定时器模式选择位,置0时为看门狗模式;置1时为定时器模式。

WDTCNTCL 计数器清零控制位,置0时无作用;置1时计数器清零,即WDTCNT =0。

WDTSSEL 时钟源选择位,置0时为SMCLK;置1时为ACLK。

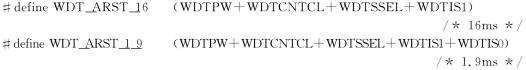

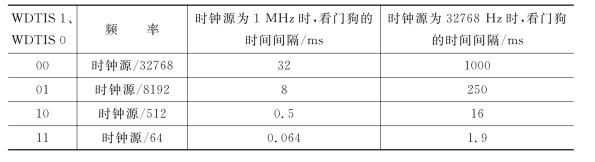

WDTIS x 时间间隔选择位,x=0、1,如表5-2所示。

表5-2 时间间隔选择位

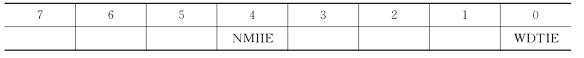

定时器的中断允许寄存器IE1如表5-3所示。

表5-3 中断允许寄存器IE1(与看门狗有关的部分)

NMIIE NMI中断允许位,置0时中断禁止;置1时中断允许。

WDTIE 看门狗定时器中断允许位,置0时中断禁止;置1时中断允许,用于定时器模式,看门狗模式不需要中断允许。

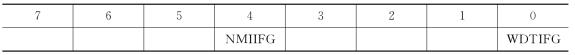

定时器的中断标志寄存器IFG1如表5-4所示。

表5-4 中断标志寄存器IFG1(与看门狗有关的部分)

NMIIFG NMI中断标志位,置0时没有中断;置1时中断标志建立。

WDTIFG 看门狗定时器中断标志位,置0时没有中断;置1时中断标志建立。

实例5.1 看门狗定时器的应用

任务要求:利用看门狗定时器产生设定的时间间隔中断,在中断服务程序中切换LED灯,亮1 s灭1 s。

分析说明:看门狗定时器的时钟源只有SMCLK和ACLK两种;4种分频值,只能实现几种简单的定时间隔中断。

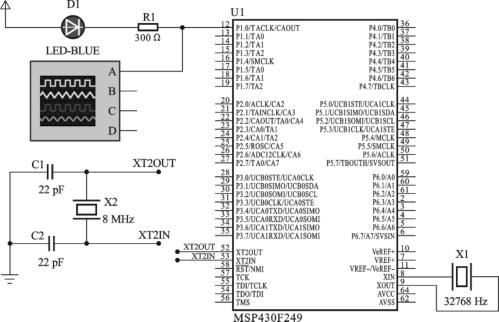

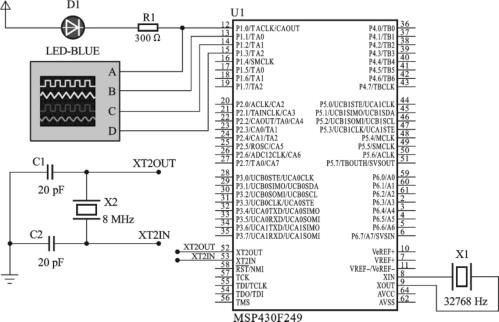

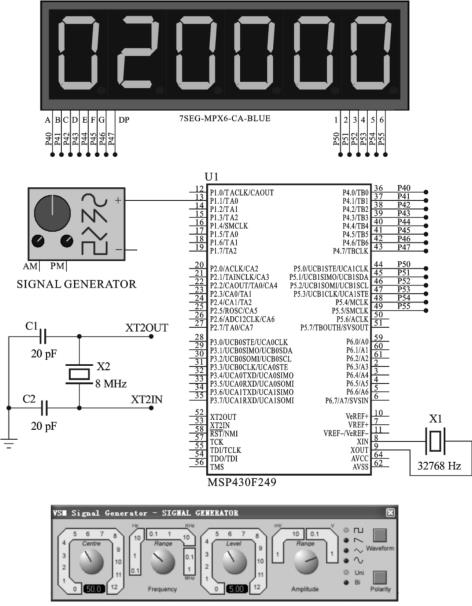

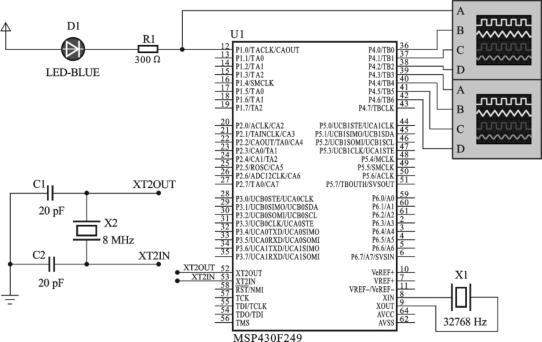

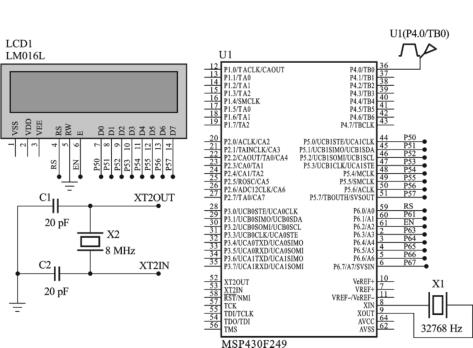

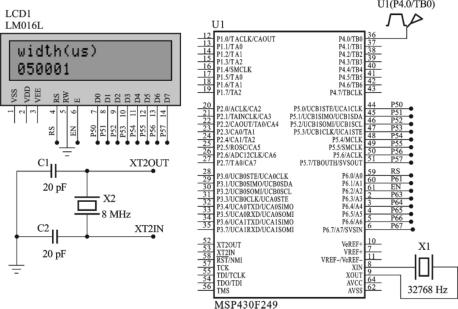

图5.1 实例5.1硬件电路图

1)硬件电路设计

P1.0引脚接LED发光二极管,同时用虚拟示波器观察P1.0引脚的电平变化。低频晶振LFXT1采用32768 Hz的晶振,获得稳定的ACLK时钟源。硬件电路图如图5.1所示,XT2接8MHz晶振(XT2频率范围为400 k Hz~16 MHz),两个22 p F匹配电容,供MCLK、SMCLK选用。一般发光二极管LED管压降约1.8~2.2 V,电流5~10 m A,因此限流电阻R1取300Ω。

2)程序设计

看门狗定时器时钟源选用ACLK(32768 Hz),分频系数为32768,得到1 s定时时间间隔。P1.0引脚设置为输出方式,进入LPM3低功耗模式。

3)仿真结果与分析

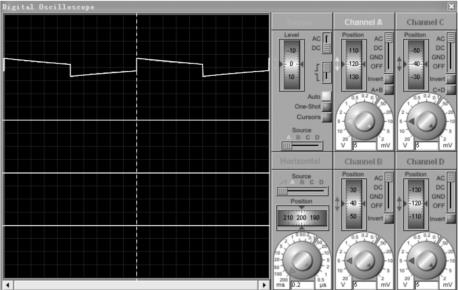

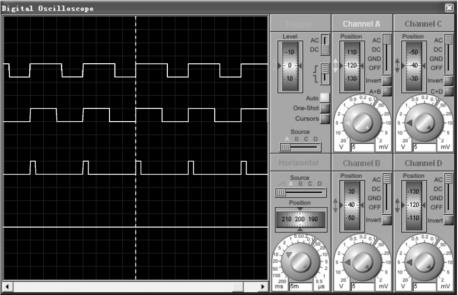

双击MSP430F249单片机,装载可执行文件Debug\Exe\WDT.hex,设置仿真参数MCLK=(Default),ACLK=32768 Hz。运行后可以观察到LED灯亮1 s灭1 s;同时在示波器上观察到高电平1 s、低电平1 s的周期信号,如图5.2所示。

图5.2 实例5.1仿真结果图

5.2 定时器A

1.定时器A的功能

MSP430F249单片机的定时器A是具有3个捕获/比较寄存器的16位定时器/计数器。定时器A可以用来实现计数、延时、信号频率测量、信号触发检测、脉冲脉宽信号测量。定时器A还可以实现下列功能。

(1)PWM信号输出功能:通过设置TA的工作模式,结合CCR0、CCR1或CCR2计数,直接从CCR0、CCR1或CCR2中子模块的OUTx端输出。

(2)Slope AD转换功能:利用定时器A与比较器A结合设计成斜边数模转换器。

(3)实现软USART功能:利用CCR0子模块中的捕获输入功能,结合TAR实现通用串行异步通讯功能(USART)。

(4)ADC12模块的采样信号:利用定时器的TAR或CCR0实现OUTx输出得到ADC12模块所需要的采样触发信号。

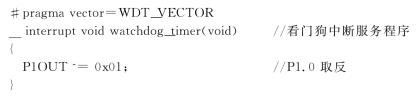

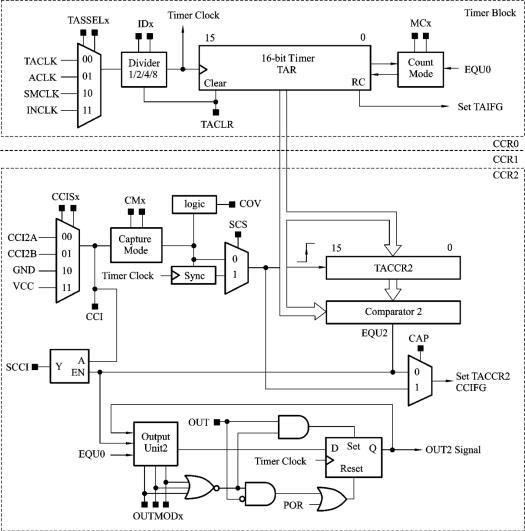

2.定时器A的结构

定时器A的基本结构如图5.3所示。

图5.3 定时器A的基本结构图

在详细讲述定时器A的工作原理之前,我们先了解一下与定时器A有关的9个寄存器。定时器A主要资源有1个16位的定时计数器、1个控制寄存器、1个中断向量寄存器、3个可配置的捕获/比较控制寄存器和3个捕获/比较寄存器。以上定时器资源可作多种组合使用,以实现强大的功能。

3.定时器A的寄存器

定时器A的相关寄存器如表5-5所示。

表5-5 定时器A的相关寄存器

(1)定时器A的控制寄存器如表5-6所示。

表5-6 定时器A的控制寄存器TACTL

TASSELx 定时器时钟源选择(x=0、1)如表5-7所示。

表5-7 定时器时钟源选择

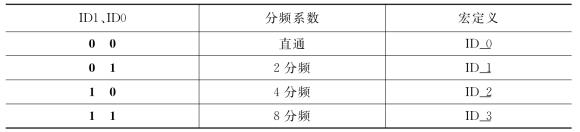

IDx 分频系数(x=0、1)选择如表5-8所示。

表5-8 分频系数选择

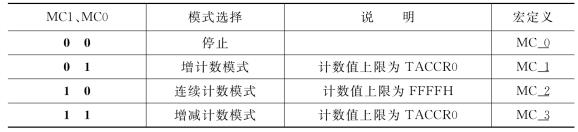

MCx 定时器模式选择(x=0、1)如表5-9所示。

表5-9 定时器模式选择

TACLR 定时器A清除位,该位置位将计数器TAR清零、分频系数清零、计数模式置为增计数模式。TACLR由硬件自动复位,其读出始终为0。定时器在下一个有效输入沿开始工作。

TAIE 定时器A中断允许位,置0时中断禁止;置1时中断允许。

TAIFG 定时器A中断标志位,置0时没有中断;置1时中断标志建立。增计数模式:当定时器由CCR0计数到0时,TAIFG置位。连续计数模式:当定时器由0FFFFH计数到0时,TAIFG置位。增/减计数模式:当定时器由CCR0减计数到0时,TAIFG置位。

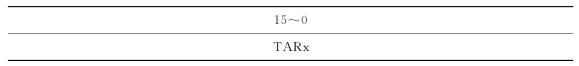

(2)定时器A的16位计数器TAR,如表5-10所示。

表5-10 定时器A的16位计数器

这是计数器的主体,内部可读写。如果要写入TAR计数值或用TACLK控制寄存器中的控制位来改变定时器工作(特别是修改输入选择位、输入分频器和定时器清除位时),修改时应先停止定时器,否则输入时钟和软件所用的系统时钟异步可能引起时间竞争,使定时器响应出错。

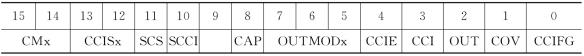

(3)定时器A有3个捕获/比较模块,每个模块都有自己的控制寄存器TACCTL0~TACCTL2。

捕获/比较控制寄存器TACCTLx(x=0、1、2)如表5-11所示。

表5-11 捕获/比较控制寄存器

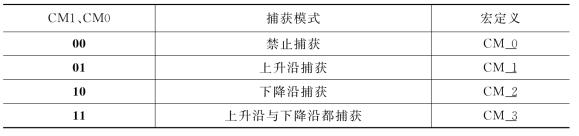

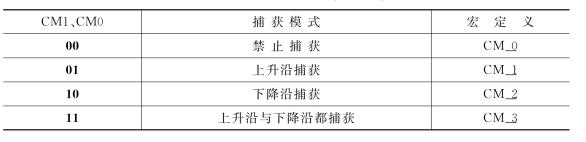

CMx捕获模式(x=0、1)的选择如表5-12所示。

表5-12 CMx捕获模式(x=0、1)

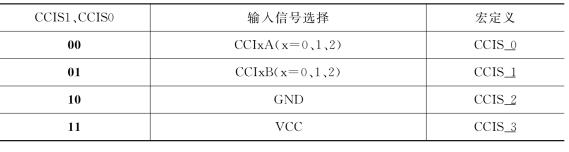

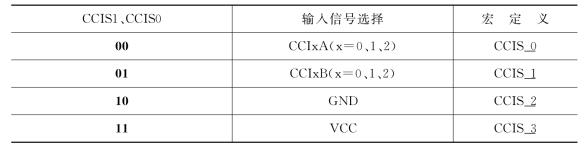

CCISx捕获/比较输入信号选择如表5-13所示。

表5-13 CCISx捕获/比较输入信号选择(x=0、1)

SCS 同步捕获源选择,置0时为异步捕获;置1时为同步捕获。异步捕获模式允许在请求时立即将CCIFG置位和捕获定时器值,适用于捕获信号的周期远大于定时器时钟周期的情况。但是,如果定时器时钟和捕获信号发生时间竞争,则捕获寄存器的值可能出错。在实际中经常使用同步捕获模式,捕获事件发生时,CCIFG置位和捕获定时器值将与定时器时钟信号同步。

SCCI 同步捕获/比较输入位,仅用于比较模式。比较相等信号EQUx将选中的捕获、比较输入信号CCIx(CCIx A,CCIxB,VCC和GND)进行锁存,这样当计数器的值继续变化时,锁存器中的值仍然保持不变,然后可以通过SCCI位读出。

CAP 模式选择位,置0时为比较模式;置1时为捕获模式。

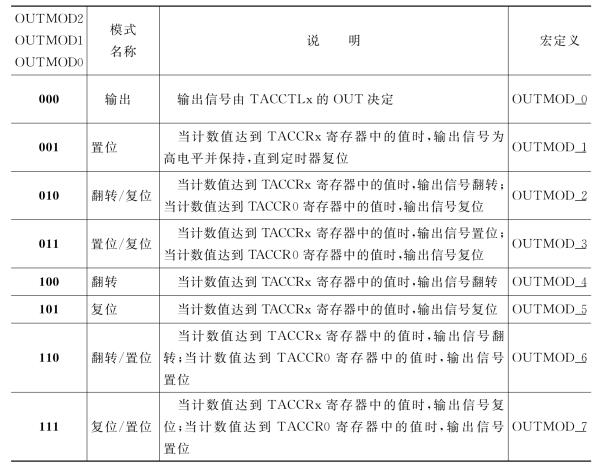

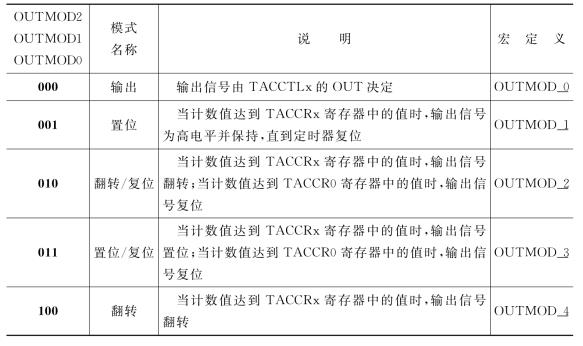

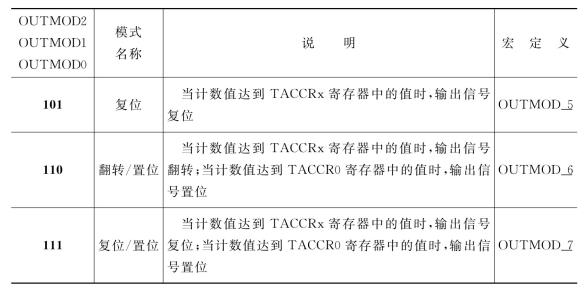

OUTMODx 输出模式(x=0、1、2),如表5-14所示。

表5-14 输出模式

CCIE 捕获/比较中断使能位,置0时中断禁止;置1时中断允许。

CCI 捕获/比较输入位,用来读取选择的输入信号。

OUT 输出位,如果OUTMODx设为000时,那么由该位决定输出到OUTx中的信号。置0时输出低电平;置1时输出高电平。

COV 捕获溢出标志位。当CAP=1时,选择捕获模式,如果捕获寄存器的值被读出前再次发生捕获事件,则COV置位。读捕获寄存器时不会使溢出标志复位,须用软件复位。

CCIFG 捕获/比较中断标志位。捕获模式:寄存器CCR0捕获了定时器TAR值时置位。比较模式:定时器TAR值等于寄存器CCR0值时置位。

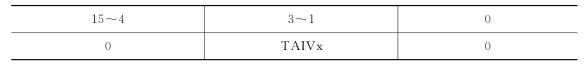

(4)定时器A的中断矢量寄存器TAIV如表5-15所示。

表5-15 定时器A的中断矢量寄存器TAIV

中断矢量值确定申请TAIVx中断的中断源,具体含义如表5-16所示。

表5-16 中断源的含义

4.定时器工作原理

1)定时器的4种工作模式

(1)停止模式:定时器停止工作。

(2)增计数模式:如果定时器原来处于停止模式,设置增计数模式会同时启动计数器TAR开始计数。当计数值达到TACCR0寄存器的值时,中断标志TACCR0_CCIFG置位。当下一个计数时钟到来时,计数器TAR的值变为0,重新开始新一轮计数。因此定时器的计数周期由TACCR0的值决定。由于必须用TACCR0寄存器存放计数的最大值,所以增计数模式比连续计数模式多占用了TACCR0寄存器空间。在增计数期间还可以设置CCR1、CCR2来产生中断标记,产生PWM等信号。

(3)连续计数模式:连续计数模式与增计数模式的区别是连续计数模式不占用TACCR0寄存器。当CCRx(x=0、1、2)寄存器的值与TAR的值相等时,若此时CCRx处于中断允许,则产生相应的中断标志CCIFGx。而TAR的中断标志TAIFG位则在TAR计数值从FFFFH转为0时产生中断标志TAIFG。定时器A连续计数模式启动后,TAR的值开始从0~FFFFH不断重复计数,直至软件控制其停止计数为止。

(4)增减计数模式:增减计数模式也要用到TACCR0寄存器,定时器启动后,计数值先从0增加到TACCR0寄存器中的值,然后计数器又开始减少,减少到0后,计数器又递增,如此周而复始。在增减计数模式一个周期中,中断标志TAIFG和TACCR0_CCIFG各置位一次。当计数值达到最大值即TACCR0的值时,中断标志TACCR0_CCIFG置位;当计数值递减到0时,中断标志TAIFG置位。增减计数模式在定时器周期不是0FFFFH且需要产生对称的脉冲时使用。例如,两个输出驱动一个H桥时不能同时为高,增减计数模式支持在输出信号之间有死区时间的应用。

2)定时器工作原理说明

(1)比较模式:这是定时器的默认模式。如果事先设置好定时器的比较值TAC-CRx(x=0、1、2),并开启定时器中断,当TAR的值增加到TACCRx的时候,中断标志位CCIFGx(x=0、1、2)置1,进入相应的中断服务程序。比较模式常用于产生PWM信号或设置给定时间间隔中断。

(2)捕获模式:当TACCTLx(x=0、1、2)控制寄存器中的CAP置位时,则相应的TACCRx处于捕获模式。捕获源可以由CCISx选择CCIx A,CCIxB,GND,VCC,可以利用外部信号的上升沿、下降沿或上升/下降沿触发,完成捕获后相应的捕获标志位CCIFGx置1。当捕获事件发生时,硬件自动将计数器TAR的值拷贝到TACCRx寄存器中,同时中断标志CCIFGx置位。捕获模式主要用于测量脉冲周期、频率、速度等。

(3)输出模式:输出模式由OUTMODx位来确定,如表5-14所示。模式0用于电平输出,由OUT位来控制TAx(x=0、1、2)管脚的高低电平输出;模式1和模式5为单脉冲输出,可以用来代替单稳态电路产生单脉冲波形;模式3和模式7用来产生脉宽调制信号(PWM信号);模式4为可变频率或移相输出;模式2和模式6为带死区的PWM模式,广泛用于逆变器、开关电源、变频调速和斩波器等高效率的功率变换应用场合。

3)定时器工作模式说明

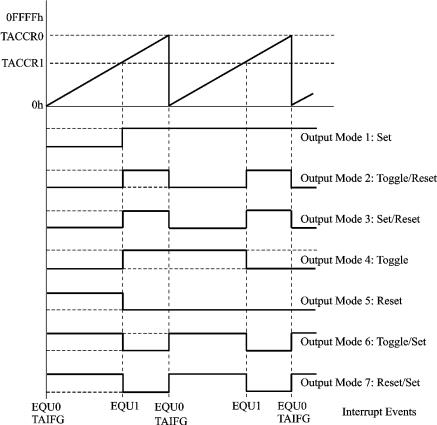

(1)定时器A工作在增计数模式下,TACCR0作为周期寄存器,TACC1作为比较寄存器,不同的输出模式产生的输出波形如图5.4所示。

图5.4 定时器A处于增计数模式

(2)定时器A工作在连续计数模式下,TACCR0、TACCR1作为比较寄存器,不同的输出模式产生的输出波形如图5.5所示。

图5.5 定时器A处于连续计数模式

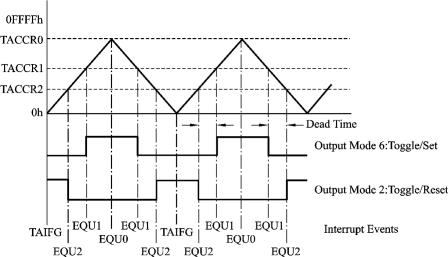

(3)定时器A工作在增/减计数模式下,TACCR0作为周期寄存器,TACC1和TACC2作为比较寄存器,不同的输出模式产生的输出波形如图5.6所示。

图5.6 定时器A处于增/减计数模式

4)定时器A的中断说明

定时器A有两个中断向量,一个单独分配给捕获比较寄存器CCR0,另一个作为共用的中断向量用于定时器溢出和其他的捕获比较寄存器(CCR1和CCR2)。

CCR0中断向量具有最高的优先级,CCR0用于定义增计数和增/减计数模式的周期。CCR0的中断标志TACCR0_CCIFG在执行中断服务程序时能自动复位。CCR1、CCR2和定时器溢出共用另一个中断向量,属于多源中断,对应的中断标志为TACCR1_CCIFG、TACCR2_CCIFG和TAIFG1,在读中断向量字TAIV后自动复位。如果不访问TAIV寄存器,则不能自动复位,须用软件清除;如果相应的中断允许位为零(不允许中断),则将不会产生中断请求,但中断标志仍存在,这时须用软件清除。

实例5.2 定时器A定时1 s

任务要求:利用定时器A产生设定的时间间隔中断,在中断服务程序中切换LED灯的亮灭,亮1 s灭1 s。

分析说明:定时器A的时钟源可以选择为SMCLK、ACLK和外部引脚输入(TACLK、INCLK),一般选择为SMCLK和ACLK。ACLK为低频晶振32768 Hz及1/2/4/8分频,定时器A可以再次对ACLK进行1/2/4/8分频,定时器A的时基最小为1/32768 s(约30μs),最大为64分频后即1.95 ms,因此定时器A的定时范围为2 s(对应时基30μs)和128 s(对应时基1.95 ms)。SMCLK可选择XT2和内部DCO作为时钟源,若SMCLK选择XT2(例如8 MHz),则定时器A的时基最小为0.125μs,最大为64分频后即8μs,因此定时器A的定时范围为8.19 ms(对应时基0.125μs)和524 ms(对应时基8μs)。

总而言之,要求定时器时间间隔小于几百毫秒时,定时器A的时钟源采用SMCLK,SMCLK一般选取XT2作为时钟源;定时时间间隔几百毫秒至几十秒应采用ACLK(或者适当分频)作为定时器A的时钟源。

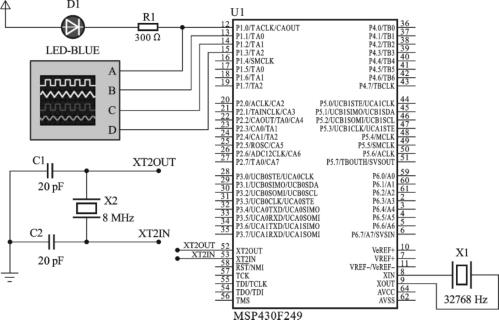

图5.7 实例5.2硬件电路图

1)硬件电路设计

P1.0引脚接LED发光二极管,同时用虚拟示波器观察P1.0引脚的电平变化。低频晶振采用32768 Hz的晶振,获得稳定的ACLK时钟源。硬件电路如图5.7所示,XT2接8 MHz晶振(XT2频率范围为400 k Hz~16 MHz),两个22 p F匹配电容,供MCLK、SMCLK选用。一般LED发光二极管的管压降1.8~2.2 V,电流5~10 m A,因此限流电阻取300Ω。

2)程序设计

MSP430F249单片机的程序运行主时钟MCLK=DCO=1.1 MHz。定时器A采用增计数模式,定时器A的时钟源为ACLK=32768 Hz。时基单位为1/32768 s,设置CCR0=32768,则定时时间间隔1 s。

3)仿真结果与分析

程序虽然很短,但是它包含了定时器的基本使用方法。使用定时器前,先设置好控制寄存器TACTL,时钟源选择、计数模式选择、中断允许和定时时间间隔CCR0的值。增计数模式,定时器A的计数值达到CCR0,TACCR0_CCIFG中断标志建立,CCR0中断为单源中断,CPU响应中断,进入定时器A0中断服务程序后,自动清除中断标志TACCR 0_CCIFG。在中断服务程序中,对P1.0取反,得到周期2 s的信号,其中高电平1 s,低电平1 s,如图5.8所示。仿真时设置参数MCLK=(Default),ACLK=32768 Hz。

图5.8 实例5.2仿真结果图

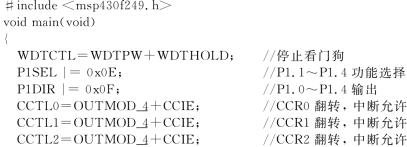

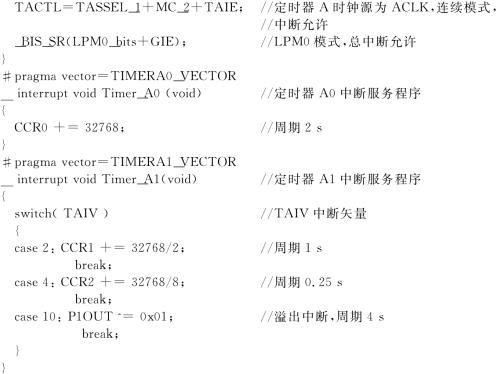

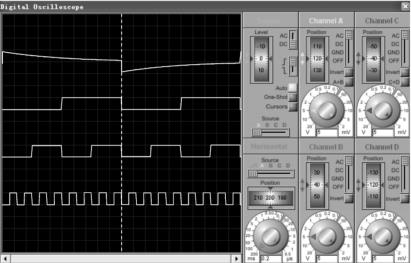

实例5.3 定时器A产生4路周期信号

任务要求:利用定时器A产生4路周期信号,周期分别为4 s、2 s、1 s和0.25 s,四路周期信号分别从P1.0和P1.1~P1.4的A0~A3输出。

分析说明:定时器A有3个捕获/比较寄存器CCR0、CCR1和CCR2。若设置定时器A工作在连续模式,利用3个比较器可以获得3路不同的周期信号,再利用定时器溢出中断可以再输出1路周期信号。因此,定时器A可以很方便地产生4路时间间隔不同的周期信号。

1)硬件电路设计

硬件电路如图5.9所示,用虚拟示波器观察P1.0~P1.3这4路引脚电平的变化。

图5.9 实例5.3硬件电路图

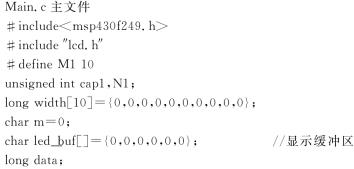

2)程序设计

MSP430F249单片机的程序运行主时钟MCLK=DCO=1.1 MHz。定时器A采用连续模式,定时器A的时钟源为ACLK=32768 Hz。时基单位为1/32768 s,设置CCR0=32768,则定时时间间隔1 s(周期2 s);CCR1=32768/2,则定时时间间隔0.5 s(周期1 s);CCR2=32768/8,则定时时间间隔0.125 s(周期0.25 s);定时器A溢出中断,定时时间间隔2 s(周期4 s)。

3)仿真结果与分析

仿真结果如图5.10所示,第1路信号周期为4 s,定时器A溢出时间间隔为2 s,在中断程序中对P1.0取反;第2路信号周期为2 s,比较寄存器CCR0设置值为32768,1 s对TA0(P1.1)取反一次;第3路信号周期为1 s,比较寄存器CCR1设置值为32768/2,0.5 s对TA1(P1.2)取反一次;第4路信号周期为0.25 s,比较寄存器CCR2设置值为32768/8,0.125 s对TA2(P1.3)取反一次。(https://www.xing528.com)

图5.10 实例5.3仿真结果图

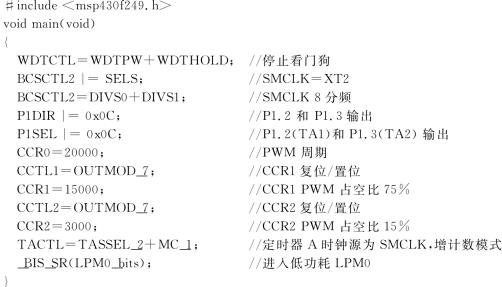

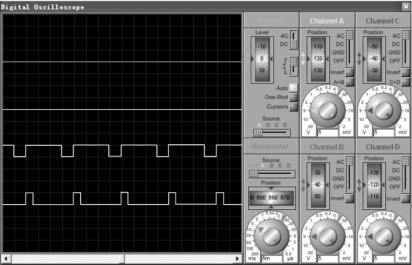

实例5.4 定时器A产生两路PWM信号

任务要求:利用定时器A产生占空比75%和15%的两路PWM信号,周期均为20 ms。

分析说明:定时器A有多种信号输出模式,其中输出模式3和模式7用来产生脉宽调制信号(PWM信号),在定时器A的增计数模式,用CCR0控制PWM信号的周期,CCR1、CCR2控制占空比,可以得到两路不同占空比的PWM信号。

1)硬件电路设计

硬件电路如图5.11所示。

图5.11 实例5.4电路图

2)程序设计

MSP430F249单片机的程序运行主时钟MCLK=DCO=1.1 MHz。SMCLK=XT2=8 MHz,定时器A时钟源为SMCLK的8分频(即1 MHz),增计数模式。时基单位1μs,CCR0=20000,则定时时间间隔20 ms(即PWM周期=20 ms)。两路PWM信号从P1.2(TA1)和P1.3(TA2)输出,设置CCR1=20000*75%=15000,则TA1的PWM信号占空比为75%,设置CCR2=20000*15%=3000,则TA2的PWM信号占空比为15%。

3)仿真结果与分析

仿真结果如图5.12所示,第3路信号为TA1输出的PWM信号,周期为20 ms,占空比75%;第4路信号为TA2输出的PWM信号,周期为20 ms,占空比15%。

图5.12 实例5.4仿真结果图

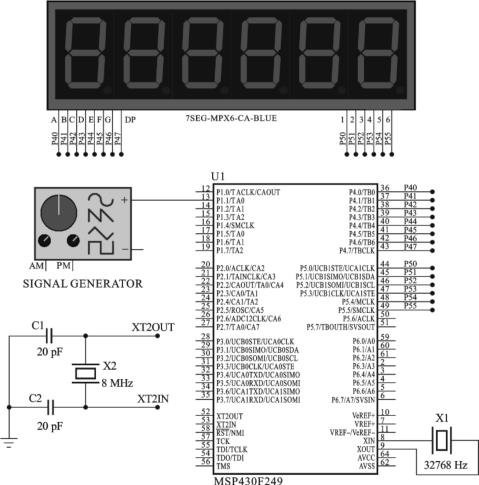

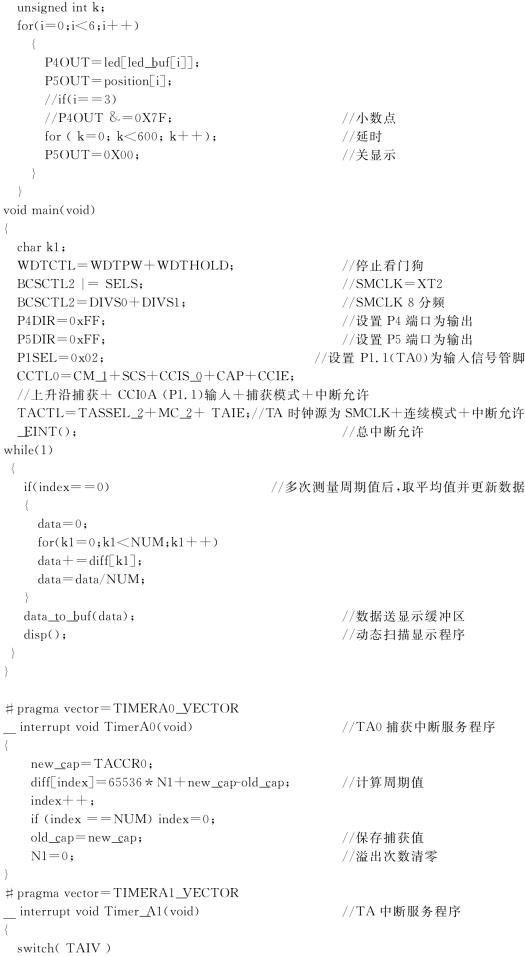

实例5.5 定时器A精确测量输入信号的周期

任务要求:利用定时器A精确测量某输入信号的周期,周期范围0~999999μs。

分析说明:利用定时器A的脉冲捕获功能可以精确地测量外部输入信号的脉宽和周期。捕获模式测量输入信号的周期时,一般设置定时器A为连续模式,如果选定的引脚上出现设定的跳变沿(上升沿或者下降沿),那么定时器A的计数值被复制到TACCRx中,并且中断标志TACCIFGx置位。在捕获中断程序中读取捕获值,相邻两次捕获值之差就是信号周期。由于事件(上升沿或者下降沿)发生的随机性,注意在需要时使能溢出中断,在溢出中断中记录溢出发生次数,周期=65536x溢出次数+两次捕获值之差。

1)硬件电路设计

低频晶振采用32768 Hz的晶振,XT2接8MHz晶振(XT2频率范围为400 k Hz~16 MHz),两个22 p F匹配电容,供SMCLK选用。显示使用6位LED共阳极模块,单片机P4端口输出每位数码管的段码,P5端口的P5.0~P5.5输出位码。输入信号源采用虚拟仪器中的信号发生器。硬件电路如图5.13所示。

2)程序设计

MSP430F249单片机的程序运行主时钟MCLK=DCO=1.1 MHz。SMCLK=XT2=8 MHz,定时器A时钟源为SMCLK的8分频(即1 MHz),连续计数模式。定时器A使用捕获模式测量信号周期时,可以让主计数器TAR工作在连续计数模式。捕获模块设置TAx(x=0~2)管脚上升沿触发,每次捕获事件发生后,在捕获中断程序中读取捕获值,相邻两次捕获值之差就是信号周期。对于计数值溢出的情况,可以在溢出中断程序中记录溢出次数,扩展周期信号的测量范围。

![]()

图5.13 实例5.5的硬件电路图

3)仿真结果与分析

输入信号50 Hz,测量的周期信号显示为20000μs;调整输入信号为5 Hz,显示为200000μs;多调整几次输入信号周期,可以看出测试结果正确。如图5.14所示。

图5.14 实例5.5仿真结果图

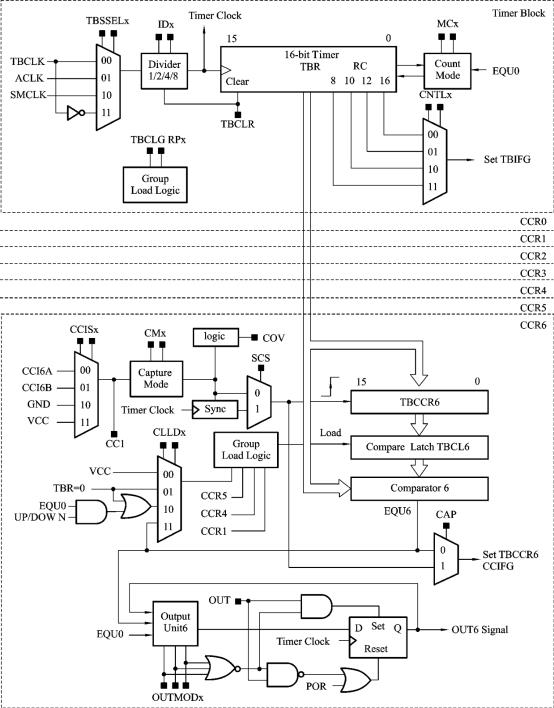

5.3 定时器B

1.定时器B的功能

MSP430F249单片机的定时器B是具有7个捕获/比较寄存器的16位定时器/计数器。TB可以支持捕获/比较功能、PWM输出和定时器功能,TB的捕获比较寄存器是双缓冲结构,定时器B比定时器A使用更为灵活。

定时器B与定时器A的大多数功能相同,它们的主要区别如下:定时器B的长度是可编程的,可编程为8、10、12、16位;定时器B的TBCCRx(x=0~6)寄存器是双缓冲的,并可以成组工作;所有定时器B的输出可以为高阻抗状态;SCCI位功能在定时器B中不存在。定时器B的结构如图5.15所示。

图5.15 定时器B的结构示意图

定时器B可以通过CNTL0、CNTL1位将它配置为8、10、12或16位定时器,相应的最大计数数值分别为0FFh、03FFh、0FFFh和0FFFFh。在8、10和12位模式下,对TBR写入数据时,数据的高4位必须为0。

时钟源的选择和分频:定时器的时钟源可以是内部时钟源ACLK、SMCLK,或外部源TBCLK和INCLK。时钟源由TBSSEL0、TBSSEL1位来选择,所选择的时钟可以通过ID0、ID1位进行2、4、8分频,当TBCLR置位时,分频器复位。

定时器可以通过以下两种方式启动或重新启动。

(1)当定时器B的TBCTL寄存器中的MCx>0并且时钟源处于活动状态时。

(2)当定时器模式为up或up/down模式时(即单调增和增/减模式),定时器可以通过写0到TBCLR来停止计数。定时器可以通过写一个非0的数值来重新开始计数。在这种情况下,定时器从0开始增计数。

捕获比较寄存器TBCCRx(x=1~6)中的CCIFG和TBIFG标志共用一个中断向量(不包括TBCCR0_CCIFG)。中断向量寄存器TBIV用于确定它们中的哪个中断要求得到响应。最高优先级的中断(不包括TBCCR0_CCIFG,TBCCR0单独使用一个中断向量)在TBIV寄存器中产生一个数字(见寄存器说明),这个数字是规定的数字,可以在程序中识别并自动进入相应的子程序。禁止定时器B中断不会影响TBIV的值。

2.定时器B的寄存器

定时器B的相关寄存器如表5-17所示。

表5-17 定时器B的相关寄存器

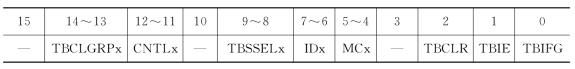

(1)定时器B的控制寄存器TBCTL如表5-18所示。

表5-18 定时器B控制寄存器TBCTL

定时器B的比较寄存器成组控制,如表5-19所示。

表5-19 TBCLGRPx比较寄存器成组控制

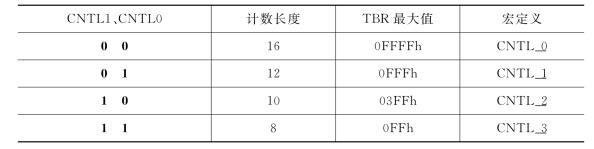

定时器B的CNTLx计数长度选择如表5-20所示。

表5-20 CNTLx计数长度选择

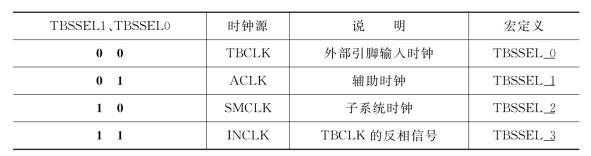

定时器B的TASSELx定时器时钟源选择如表5-21所示。

表5-21 TASSELx定时器时钟源选择

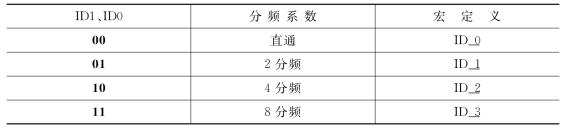

定时器B的IDx分频系数选择如表5-22所示。

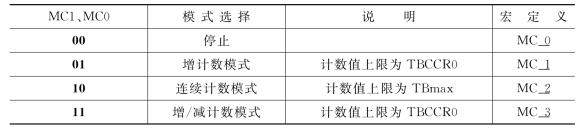

定时器B的模式选择如表5-23所示。

TBCLR 定时器B清除位,若该位置位将计数器TBR清零、分频系数清零、计数模式置为增计数模式。TBCLR由硬件自动复位,其读出始终为0。定时器在下一个有效输入沿开始工作。

表5-22 IDx分频系数

表5-23 MCx定时器模式选择

TBIE 定时器B中断允许位,置0时中断禁止;置1时中断允许。

TBIFG 定时器B中断标志位,置0时没有中断;置1时中断标志建立。增计数模式:当定时器由CCR0计数到0时,TBIFG置位。连续计数模式:当定时器由0FFFFH计数到0时,TBIFG置位。增/减计数模式:当定时器由CCR0减计数到0时,TBIFG置位。

(2)定时器B的16位计数器TBR如表5-24所示。

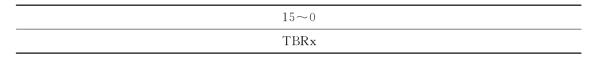

表5-24 定时器B的16位计数器TBR

这是计数器的主体,内部可读写。如果要写入TBR计数值或用TBCLK控制寄存器中的控制位来改变定时器工作(特别是修改输入选择位、输入分频器和定时器清除位时),修改时应先停止定时器,否则输入时钟和软件所用的系统时钟异步可能引起时间竞争,使定时器响应出错。

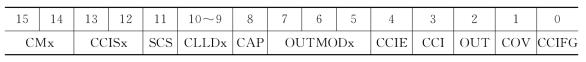

(3)定时器B有7个捕获/比较模块,每个模块都有自己的控制寄存器TBCCTL0~TBCCTL6,如表5-25所示。

表5-25 捕获/比较控制寄存器TBCCTLx(x=0~6)

定时器B的CMx捕获模式选择如表5-26所示。

表5-26 CMx捕获模式(x=0、1)

定时器B的CCIS捕获/比较输入信号选择如表5-27所示。

表5-27 CCIS捕获/比较输入信号选择

SCS 同步捕获源选择,置0时异步捕获;置1时同步捕获。

异步捕获模式允许在请求时立即将CCIFG置位和捕获定时器值,适用于捕获信号的周期远大于定时器时钟周期的情况。但是,如果定时器时钟和捕获信号发生时间竞争,则捕获寄存器的值可能出错。在实际中经常使用同步捕获模式,捕获事件发生时,CCIFG置位和捕获定时器值将与定时器时钟信号同步。

CLLDx 比较锁存加载,该位选择比较锁存加载事件,如表5-28所示。

表5-28 CLLDx比较锁存加载选择

CAP 模式选择位,置0时为比较模式;置1时为捕获模式。

OUTMODx 输出模式(x=0、1、2),输出模式的选择如表5-29所示。

表5-29 输出模式选择

续表

CCIE 捕获/比较中断使能位,置0时中断禁止;置1时中断允许。

CCI 捕获/比较输入位,用来读取选择的输入信号。

OUT 输出位,如果OUTMODx设为000时,那么由该位决定输出到OUTx的信号。置0时输出低电平;置1时输出高电平。

COV 捕获溢出标志。当CAP=1时,选择捕获模式,如果捕获寄存器的值被读出前再次发生捕获事件,则COV置位。读捕获寄存器时不会使溢出标志复位,须用软件复位。

CCIFG 捕获/比较中断标志位。捕获模式:寄存器CCRx捕获了定时器TAR值时置位。比较模式:定时器TAR值等于寄存器CCRx值时置位。

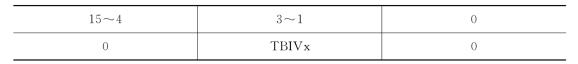

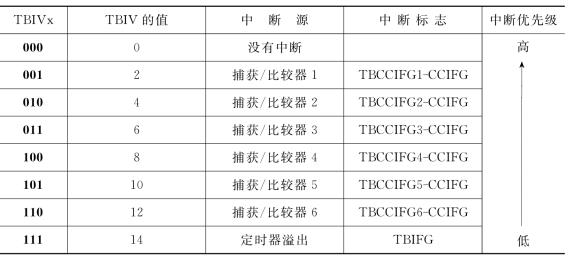

(4)定时器B的中断矢量寄存器TBIV如表5-30所示。

表5-30 定时器B中断矢量寄存器TBIV

中断矢量值确定申请TBIV中断的中断源,具体含义如表5-31所示。

表5-31 中断源的具体含义

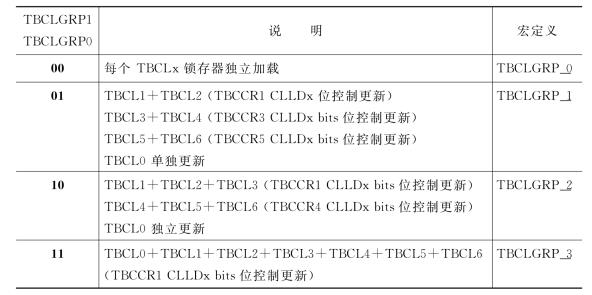

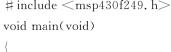

实例5.6 定时器B产生8路周期信号

任务要求:利用定时器B产生8路周期信号,周期分别为4 s、2 s、1 s、0.5 s、0.25 s、0.125 s、0.0625 s和0.03125 s,8路周期信号分别从P1.0和P2.0~P2.6的TB0~TB6输出。

分析说明:定时器B有7个捕获/比较寄存器TBCCR0~TBCCR6。若设置定时器B工作在连续模式,利用7个比较器可以获得7路不同的周期信号,再利用定时器溢出中断可以再输出1路周期信号。因此,定时器B可以很方便地产生8路时间间隔不同的周期信号。

1)硬件电路设计

MSP430F249的低频晶振为32768 Hz,为ACLK提供精确时钟,定时器B采用ACLK作为时钟源,最大定时时间间隔2s(时钟不分频)和128s(时钟64分频)。8路周期信号分别从P1.0和P2.0~P2.6的TB0~TB6输出,采用两个虚拟示波器观察,硬件电路如图5.16所示。

图5.16 实例5.6硬件电路图

2)程序设计

MSP430F249单片机的程序运行主时钟MCLK=DCO=1.1 MHz。定时器B采用连续模式,定时器B的时钟源为ACLK=32768 Hz。时基单位为1/32768 s,设置TBCCR0~TBCCR6为适当的初始值,可以得到要求的周期信号输出。利于定时器B的溢出中断,可以得到周期4 s的信号输出。

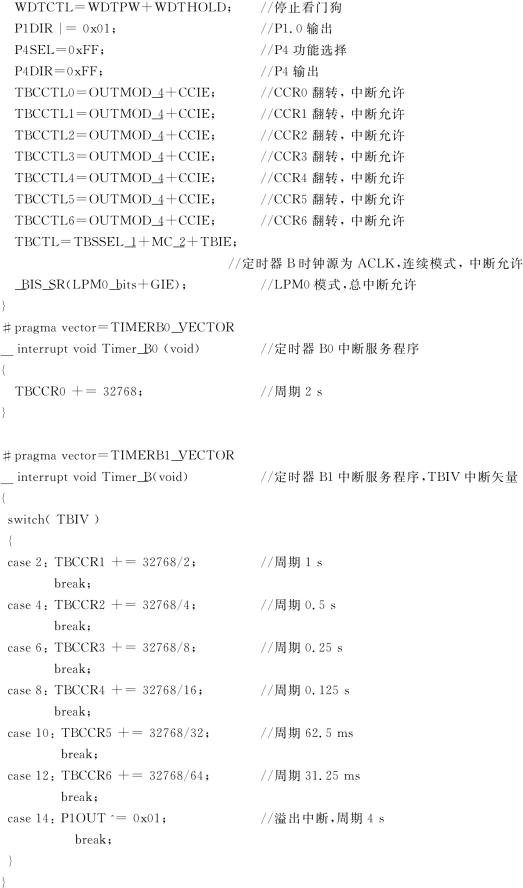

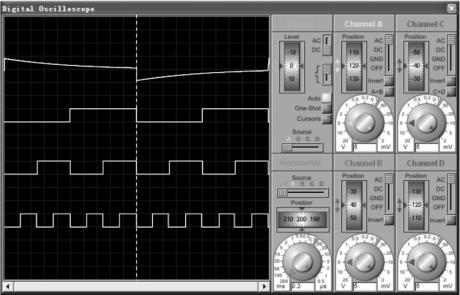

3)仿真结果与分析

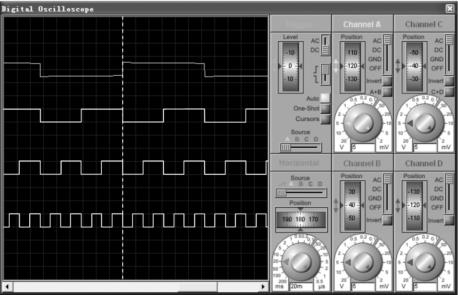

实例5.6的仿真结果如图5.17、图5.18所示。

图5.17 实例5.6仿真结果(一)

图5.18 实例5.6仿真结果(二)

实例5.7 定时器B产生6路PWM信号

任务要求:利用定时器B产生6路PWM信号,周期为20 ms,占空比分别为90%、80%、70%、60%、50%和10%。

分析说明:定时器B有多种信号输出模式,其中输出模式3和模式7用来产生脉宽调制信号(PWM信号),在定时器B的增计数模式,用TBCCR0控制PWM信号的周期,TBCCR1~TBCCR6控制占空比,可以得到6路不同占空比的PWM信号。

1)硬件电路设计

硬件电路如图5.19所示,采用两个虚拟示波器观察6路PWM信号。

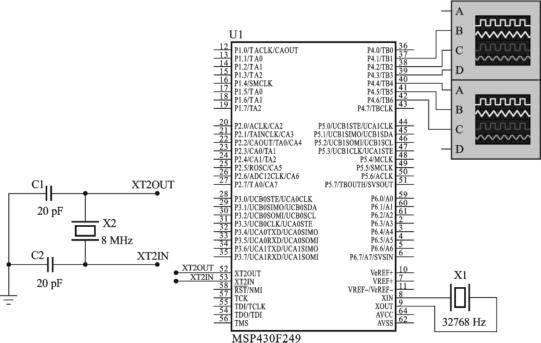

图5.19 实例5.7硬件电路图

2)程序设计

3)仿真结果与分析

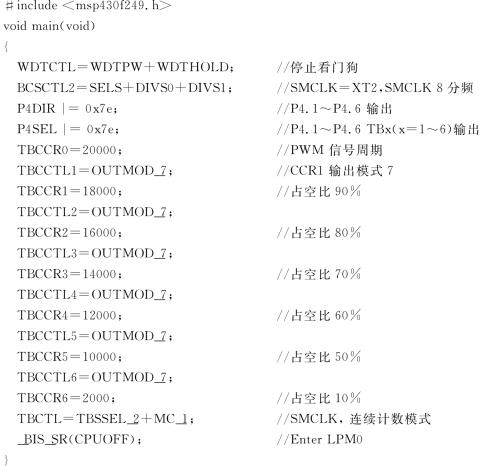

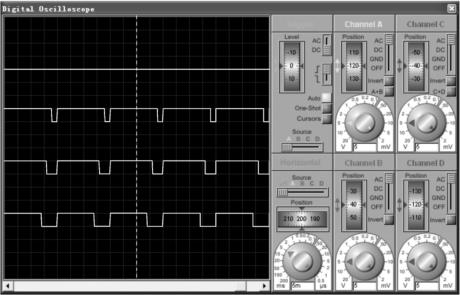

实例5.7的仿真结果如图5.20、图5.21所示。

图5.20 实例5.7仿真结果(一)

图5.21 实例5.7仿真结果(二)

实例5.8 定时器B精确测量某输入信号的脉冲宽度

任务要求:利用定时器B精确测量某输入信号的脉冲宽度,脉冲宽度范围0~999999μs。

分析说明:利用定时器B的脉冲捕获功能可以精确地测量外部输入信号的脉冲宽度。捕获模式测量输入信号的脉宽时,一般设置定时器B为连续模式,可以先设置捕获模式为上升沿触发,在捕获到的上升沿中断程序里记下TBCCRx(x=0~6)的值;再将捕获模式设置为下降沿触发,在捕获到的下降沿中断程序里记下TBCCRx(x =0~6)的值,两者之差就是输入信号高电平的脉冲宽度。由于事件(上升沿或者下降沿)发生的随机性,注意使能溢出中断,在溢出中断中记录溢出发生次数,脉冲宽度=65536x溢出次数+两次捕获值之差。

1)硬件电路设计

硬件电路参见图5.22所示。

图5.22 实例5.8的硬件电路图

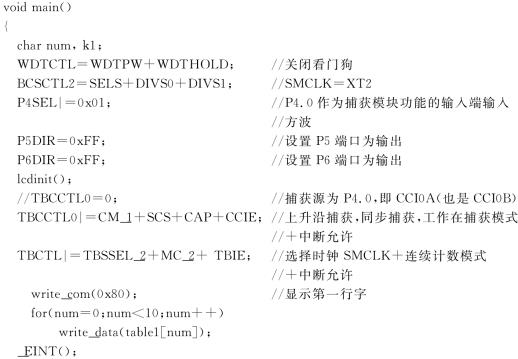

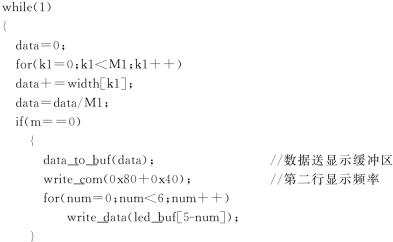

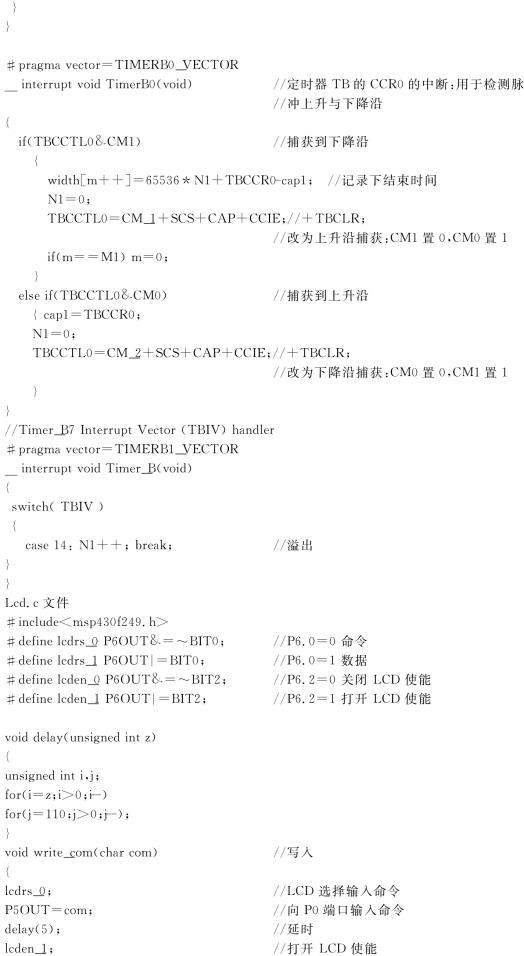

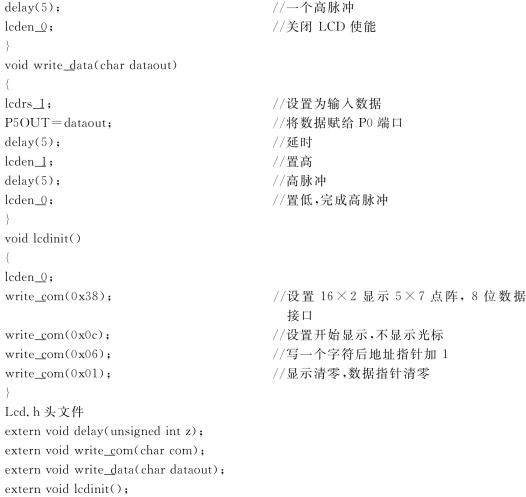

2)程序设计

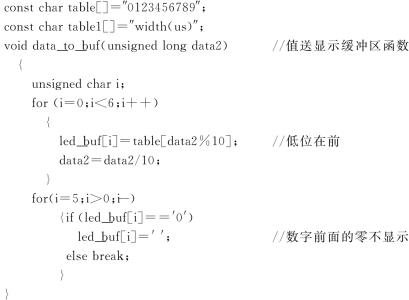

受到简短的C语言入门程序范例的影响,初学者往往将所有的代码都写在一个C文件中。这是一种非常坏的习惯。当程序逐渐变长,只要超过几个屏幕长度,就会发现编辑、查找和调试都将变得非常困难。而且这种代码很难用在别的项目中,除非仔细地理顺函数关系,然后寻找并复制每一段函数。

合理的方法是将一个大程序划分为若干小的C文件。在单片机程序中,最常用的划分方法是按硬件功能划分,将每个功能模块做成独立的C文件。例如一个项目中会用到定时器B、16位AD转换器、LCD显示、键盘,可以划分为4个文件:TB.C、ADC16.C、LCD.C、Key.C。属于每个功能模块的函数写在相应的文件中,然后在相应头文件中声明对外引申的函数与全局变量。

做好文件划分和管理之后,每个文件都不会很长,如果需要修改或调试某个函数,打开相应模块的C文件,很容易找到。打开相应的头文件还可查看函数列表。这些代码还能被重复使用。假设另一项目也用到LCD显示器,只要把LCD.C和LCD.h文件复制并添加到新工程内即可调用各种LCD显示函数,避免了重复劳动。

3)仿真结果与分析

输入信号的参数设置如图5.23所示。仿真结果如图5.24所示。

图5.23 输入信号参数设置

图5.24 实例5.5仿真结果图

思考与练习

1.MSP430F249定时/计数器的时钟源有哪些?预分频器的作用是什么?

2.MSP430F249定时/计数器的定时范围是多少?

3.在MSP430F249单片机中,假设SMCLK=8 MHz,ACLK=32768 Hz。要求编程实现为定时器A配置时钟源和工作模式,从P1.0输出周期1s的方波信号,无需CPU干预。

4.使用MSP430F249的定时/计数器编程实现产生周期50 ms、占空比30%的PWM信号,并在Proteus上完成仿真。

5.使用定时器A对外部输入的脉冲信号进行计数,当计满100次时,定时器A暂停计数且蜂鸣器响1 s,然后定时器A又从0开始计数,两位LED数码管能够实时显示当前计数值。

6.设计一个30 s倒计时器,用两位数码管显示,要求使用定时器B作为秒计时器。

7.使用定时器B设计一个分频器,用两位数码管显示分频系数,按K1键分频系数递增,按K2键分频系数递减,分频值1~10。

8.使用定时器B设计一个占空比可调的PWM信号发生器,按K1键占空比以10%递增,按K2键占空比以10%递减。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。