第六章 高档嵌入式处理器

本章主要介绍嵌入式系统中常见的高档处理器的关键技术和主流产品。主流的高档32位嵌入式处理器有以下几个系列:首先,市场占有率最高当属ARM内核系列的微处理器,目前ARM处理器的应用已经覆盖了从超低功耗、超小体积的低端产品到多核架构的高端产品的整个嵌入式应用领域;其次,一个很重要的系列就是MIPS系列微处理器,由于其独特的设计思想,使得一些低功耗高性能产品都采用了其设计思想;最后,将介绍由国际商业机器公司(IBM)、摩托罗拉和苹果(Apple)三家跨国公司联合开发的PowerPC系列嵌入式微处理器,由于这三家公司在应用领域的独特优势,使得该系列的处理器得到较广泛应用。

6.1 高档嵌入式处理器的关键技术

6.1.1 精简指令集技术(Reduced Instruction Set Computer,RISC)

1975年,IBM工程师约翰·科克(John Coke)研究IBM370系统后发现,20%的简单指令占到80%的在程序使用时间,而占指令总数80%的复杂指令却只有20%的机会被用到。由此,他提出了精简指令集计算机的RISC概念,其基本思想主要有以下几点。

(1)指令数量少,指令格式规范。性能的提高依靠更加合理地硬件电路设计和更好地工艺,而复杂指令集(CISC)技术则主要通过增加功能更强大的指令,这些指令利用硬件部件得以高速执行,从而提高系统的运行效率。

(2)利用流水线和超标量技术让处理器在一个时钟周期内可处理多条指令。

(3)寻址方式简化,几乎都使用寄存器寻址,提高寻址效率。

(4)大量利用寄存器间操作,只用Load、Store操作访问内存,从而减少指令执行时访存的次数,提高运行效率。

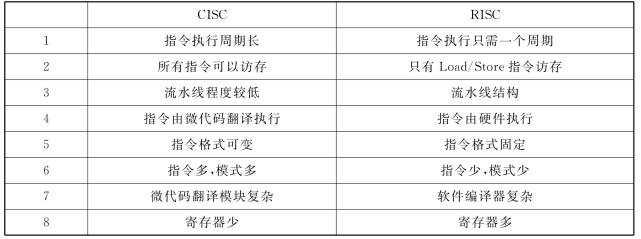

CISC与RISC的技术对照详见表6-1。

表6-1 CISC与RISC技术对照表

采用RISC技术的微处理器主要优点有以下几点。

(1)对外部中断响应速度的更快。由于每条指令执行时间缩短,使得对中断响应的速度比CISC指令更快。

(2)代码执行效率更高。由于指令结构简单,且大量使用寄存器访问方式,使得其执行速度较CISC系统大为提高。

(3)系统功耗更低。由于结构的减化和外部访存操作的减少,其功耗相对CISC系统有明显减少。

(4)CPU集成度更高,指令数量较少。指令结构简单,使得芯片上可被用于其他功能的空间有所增加,从而提高系统的总体集成度。

(5)研发时间更短。由于减少了复杂指令部件,使得总体时间得以缩短。

6.1.2 哈佛体系结构

哈佛体系结构是对冯·诺依曼体系结构的一种改进。在冯·诺依曼体系结构中,所有的数据和程序都存储在一个主存储器中,通过不同的地址指针进行来指示为数据还是程序。这使得数据和程序不可能同时被访问,只能分时操作。

在哈佛体系结构中,计算机的存储器被分为两个部分,一部分做为指令存储器,用于存放待执行的程序;另一部分作为数据存储器,用于存放待处理的数据。这两个存储器通过各自的总线与CPU相连,从而大大提高处理器的数据吞吐率。

哈佛结构的基本特点包括两方面。

一方面,程序指令存储和数据存储分开的存储器结构,指令和数据可以有不同的数据宽度。如微芯科技公司的PIC16芯片的程序指令是14位宽度,而数据是8位宽度,从而提高了执行效率和数据吞吐率。

另一方面,为了满足哈佛结构中数据存储空间与程序存储空间分离的结构要求,在CPU内部将片内Cache也分为两类,一种用于存放数据,另一种用于存储程序,以达到分别实现高速缓冲的目的。

6.1.3 桶型移位器

移位操作是计算机中的一个重要运算之一,一般通过硬件实现,由连接在算术逻辑部件内部或外部的移位器执行。传统计算机的ALU输出端附加移位控制逻辑的结构属于ALU内部移位器结构,这种移位器只能完成直送、左移1位和右移1位的操作。也就是说,当需要进行多位移位操作时,需要由多个时钟来驱动才能完成。

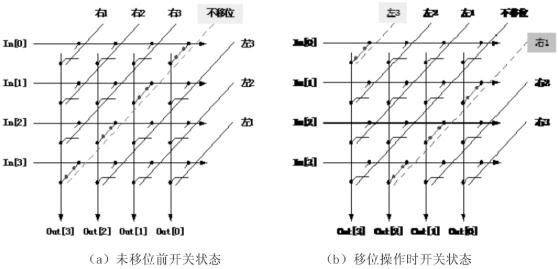

桶型移位器是具有n位数据输入、n位数据输出和1组指令输入的组合逻辑电路,一般位于ALU的前面。涉及桶型移位器操作的机器指令需要指出移动方向和位数(1 ~n)。桶型移位器通过多路开关方式,可以在一个时钟周期内完成任意位数(1~n)的移动。如图6-1所示,向左移3位(或向右移1位),只需要将多路开关切换一次就可以完成。

图6-1 桶型移位器功能示意图

6.1.4 正交指令集技术

所谓正交指令集,是描述特定处理器指令系统的操作码或者地址码的长度特征,以及操作码与各地址码的取值关联度特征。

一个微处理器的指令是否正交指令集,要看它是否满足以下几个特征:

(1)指令集中绝大多数指令的长度应相同;

(2)指令的操作码和操作数寻址字段的长度相对固定;

(3)在寻址字段中,所有寄存器的寻址可以替换;

(4)在正交指令集中,一条机器指令的操作码、寻址方式、第1操作数地址和第2操作数地址4个字段的取值相互独立。

一些微处理器虽然号称具有正交指令集特性,但并非所有指令都能满足该特性。

6.1.5 双密度指令集技术

所谓指令密集,是指在执行同一机器指令操作步骤的前提下,单位内存空间所容纳的机器指令数。也就是说,为了完成一个特定运算,需要多大内存空间存储其指令。指令密度是衡量一个指令系统的设计是否精巧、是否合理的重要标志。在嵌入式系统中,由于体积、功耗、成本等因素的限制,指令集密度越高,在相同内存中可容量的指令就越多,功能也就可以越多。为了兼顾指令集密度和执行效率,一些微处理器将指令系统设计成双密度的指令集,以满足不同条件下的应用需要。

ARM微处理器采用的是32位系统设计,配有定长32位的指令集。但ARM微处理器也配备16位指令集,称为Thumb指令集。它允许软件编码为更短的16位机器指令。早期16位Thumb指令集称为Thumb-1指令集,其指令密度远高于32位指令集。2003年6月,安谋国际科技公司推出了Thumb-2核心指令集技术。利用Thumb-2的16位指令系统在功能相同的情况下,以74%的指令体积达到32位系统98%的性能。这对于嵌入式系统而言是一件非常有意义的工作。

6.1.6 地址对准技术

边界地址对准是一个十分重要的存储管理方式。一个数据如果采用与数据宽度和寻址相一致的边界地址对准方式来存储数字,则其数据的读取效率要比非边界地址对准方式高出很多。最典型的就是在X86的16位系统下,如果数据的存储是从0号单元开始,按照2字节方式进行数据存储,那么在对内存访问时,就只需要进行一次总线操作就可以将16位数据读出;而如果未按照2字节方式存储,读取16位数据时,就需要进行两次总线操作才能将16位数据读出,其总线访问效率降低了一半。在32位系统中则需要按照4字节地址方式进行数据对准存放,也就是所有数据的存放地址都是4的整数倍开始。这样在进行数据访问时,读取一个32位的数据只需要一次总线操作就可以完成,否则需要两个总线周期。

对于要求地址对准的嵌入式微处理器,如果在运行时发生了指令地址没有对准的情况,或者数据地址没有对准的异常情况,则处理器会采取一些预定的强制性措施执行。例如以忽视末位地址值和强制置位地址为零等方式访问主存。

6.1.7 地址重映射技术

一般而言,计算机的存储单元与分配给它的地址之间具有一一对应的映射关系,而且在系统工作时是固定不变的。如果计算机在运行过程中改变了这种映射关系,就叫做地址重映射。嵌入式系统中常会用到这种技术。

在嵌入式系统中,通常用于存放程序的存储器是Flash存储器,系统运行可以从Flash存储器上开始运行。系统上电时,处理器将存有引导代码的Nor Flash存储器映射到0x00000000地址,并开始从0号地址引导运行系统。但是在很多情况下,嵌入式系统的中断向量和异常向量表往往会存放在以0号地址为起点的存储空间中,这时一方面无法对Nor Flash进行相应的中断向量填写工作;另一方面,一旦修改了Nor Flash中的内容,可能会对系统程序造成严重的破坏。而且由于Flash的读取速度要远远比SRAM的读取速度低,这对于系统中断响应是一个极为不利的因素,为提高系统响应速度,需要将系统中断向量表存放在RAM中。因此需要在系统运行过程中,改变Flash的地址空间、SRAM或SDRAM的地址空间分配。其主要目的是将SRAM或SDRAM的地址空间迁移到由地址0开始的位置,而把Flash的地址迁移到相对高端的地址上去。

在32位系统中,地址重映射机制可以有两种不同的实现方式。

(1)微处理器内部专门设计重映射寄存器。通过机器指令将重映射寄存器的特定位进行修改,就可以由硬件逻辑来完成地址重映射操作。

(2)微处理器不设专用的重映射寄存器,采用重新改写处理器内部控制内存起止地址的Bank寄存器来实现重映射过程。

在地址重映射的过程中,程序员需要仔细考虑程序执行流程,绝对不可以在重映射时被这种变化所打断。

6.2 ARM体系微处理器

ARM(Advance Risc Machines)是一个公司的名称,同时也是一种处理器架构的名称,该公司1990年11月由英国剑桥的Acorn公司改组成立,投资方包括苹果公司、VLSI公司以及原Acorn公司的知识产权和12名工程师。该公司主要研发32位RISC处理器芯片,但是他们既不生产也不销售芯片,只将研发的芯片设计出售给生产企业,由生产企业进行二次开发和包装,形成各公司自己的芯片产品,再投入市场。可以说,他们是所有生产企业的研发中心,而所有生产企业都是他们的生产厂房。正是这种营销模式,使得ARM不但得以生存,而且得以快速发展。正是借助了生产企业的强大市场影响力,ARM已经成为一种标准,并得到人们的广泛认可和使用。目前,在移动设备上,ARM已经占到市场份额的90%。同时,一些软件系统的合作方使得ARM技术在第三方工具、软件开发、制造等方面也得到了很好的支持,使得整个系统成本得到很好的控制,这也是得到市场认可的一个重要原因。微软都不得在2011年提出,将要在下一版的Windows系统上支持ARM处理器。估计在不久的将来,ARM处理器将不单单出现在我们的手机上,还有可能出现在其他的个人电脑产品中。

6.2.1 ARM体系结构及发展

与X86体系结构使用CISC(Complex Instruction Set Computer)技术不同,ARM使用的是RISC(Reduced Instruction Set Computer)技术,RISC技术与CISC技术的关键不同体现在对芯片设计理念的差异上。计算机是定义在一定指令集(ISA)基础上的一个高速逻辑处理设备,其所有的运算过程都会映射到该指令集的一个指令序列上,并通过这个指令序列形成对运算的分析和执行,从而解决一个计算问题。

ARM处理器在设计上吸取了RISC处理器和CISC处理器的长处,在指令格式、访存方式、多寄存器、流水线等结构上采用了RISC结构,同时又增加了一定数量的指令,用于提高数据处理效率。因此,我们可以认为ARM处理器以RISC为主,兼有CISC处理器的优点。同时,ARM处理器的指令系统还增加了以下特点:

(1)所有指令可根据前面指令的执行结果决定是否执行,以提高编程效率;

(2)用加载/存储指令批量在寄存器和内存间传送数据,提高效率;

(3)在指令中可同时完成逻辑和移位操作;

(4)循环处理中可自动进行相关参数的递增或递减操作。

ARM处理器支持的指令有三类,一类是32位的ARM指令,该指令提供最高性能的处理;第二类是16位的Thumb指令,该指令用于减小代码长度,可以实现用ARM指令65%左右的体积完成相同的工作,但性能只达到ARM指令方式的60%;第三类是Jazelle指令,该指令是Java的字节码指令,通过对这种指令的支持,提高Java虚拟机的执行效率和运行速度。

ARM处理器的指令集体系结构一共发行过7个版本(V1~V7),目前,V1~V3基本已经废弃,主要使用的是V4~V7版。

1.版本4(V4结构)

不再强制要求与以前的26位体系结构版本兼容,它清楚地指明了哪个指令会引起未定义指令异常发生。版本4在版本3的基础上增加了如下内容:

(1)半字加载/存储指令;

(2)字节和半字的加载及符号扩展(Sign-Extend)指令;

(3)在T变量中,转换到Thumb状态的指令;

(4)使用用户(User)模式寄存器的新的特权处理器模式。

属于V4T(支持Thumb指令)体系结构的处理器(核)有ARM7TDMI、ARM7TDMI-S (ARM7TDMI可综合版本)、ARM710T(ARM7TDMI核的处理器)、ARM720T (ARM7TDMI核的处理器)、ARM740T(ARM7TDMI核的处理器)、ARM9TDMI、ARM910T(ARM9TDMI核的处理器)、ARM920T(ARM9TDMI核的处理器)、ARM940T (ARM9TDMI核的处理器)和Strong ARM(英特尔公司的产品)。

2.版本5(V5结构)

在版本4的基础上,对现在指令的定义进行了必要的修正,对版本4体系结构进行了扩展,并增加了指令,具体如下:

(1)改进在T变量中ARM/Thumb状态之间的切换效率;

(2)允许非T变量和T变量一样,使用相同的代码生成技术;

(3)增加计数前导零(Count Leading Zeros)指令,允许更有效的整数除法和中断优先程序;

(4)对乘法指令如何设置标志进行了严格的定义。

V5结构的ARM处理器提升了ARM和Thumb两种指令的交互工作能力,同时有了DSP指令-V5E结构、Java指令-V5J结构的支持。

属于V5T(支持Thumb指令)体系结构的处理器(核)有ARM10TDMI和ARM1020T(ARM10TDMI核的处理器)。

属于V5TE(支持Thumb、DSP指令)体系结构的处理器(核)有ARM9E、ARM9E-S (ARM9E可综合版本)、ARM946(ARM9E核的处理器)、ARM966(ARM9E核的处理器)、ARM10E、ARM1020E(ARM10E核的处理器)、ARM1022E(ARM10E核的处理器)和Xscale(英特尔公司的产品)。

属于V5TEJ(支持Thumb、DSP、Java指令)体系结构的处理器(核)有ARM9EJ、ARM9EJ-S(ARM9EJ可综合版本)、ARM926EJ(ARM9EJ核的处理器)和ARM10EJ。

3.版本6(V6结构)

ARM体系结构版本6是2001年发布的,该版本增加了媒体指令。属于V6体系结构的处理器核有ARM11(2002年发布)。V6体系结构包含ARM体系结构中所有的4种特殊指令集,即Thumb指令(T)、DSP指令(E)、Java指令(J)和Media指令。

4.版本7(V7结构)

ARM体系结构版本7是在版本6的基础上诞生的。V7结构采用了Thumb-2技术,它是在ARM的Thumb代码压缩技术的基础上发展起来的,并且保持了对现存ARM解决方案的完整的代码兼容性。Thumb-2技术比纯32位代码少使用31%的内存,减少了系统开销,同时能够提供比已有的基于Thumb技术的解决方案高出38%的性能。V7结构还采用了NEON技术,将DSP和媒体处理能力提高了近4倍,并支持改良的浮点运算,满足下一代3D图形、游戏以及传统嵌入式控制应用的需求。

Cortex系列处理器是基于ARM V7架构的,分为Cortex-M3、Cortex-R和Cortex-A3。

6.2.2 ARM处理器系列简介

ARM处理器的产品系列非常广,包括ARM7、ARM9、ARM9E、ARM10E、ARM11 和SecurCore、Cortex等。SecurCore是单独的一个产品系列,是专门为安全设备而设计的。其他厂商基于ARM体系结构的处理器,除了具有ARM体系结构的共同特点以外,每一个系列的ARM微处理器都有各自的特点和应用领域。

1.ARM7处理器系列

ARM7系列包括ARM7TDMI、ARM7TDMI-S、ARM720T和ARM7EJ-S,其最高主频可以到达130MIPS。该系列处理器提供Thumb16位压缩指令集和Embedded ICE JTAG软件调试方式,适合应用于更大规模的SoC设计中。其中,ARM720T高速缓存处理宏单元还提供8KB缓存、读缓冲和具有内存管理功能的高性能处理器,支持Linux、Symbian OS和Windows CE等操作系统。

ARM7系列处理器主要应用于对功耗和成本要求比较苛刻的消费类产品,主要有:

(1)个人音频设备(MP3播放器、WMA播放器、AAC播放器);

(2)接入级的无线设备;

(3)喷墨式打印机;

(4)数码照相机;

(5)PDA。

2.ARM9处理器系列

ARM9系列于1997年问世。由于采用了5级指令流水线,ARM9处理器能够运行在比ARM7更高的时钟频率上,改善了处理器的整体性能。存储器系统根据哈佛体系结构(程序和数据空间独立的体系结构)重新设计,区分了数据总线和指令总线。

ARM9系列有ARM9TDMI、ARM920T和带有高速缓存处理器宏单元的ARM940T。所有的ARM9系列处理器都具有Thumb压缩指令集和基于Embedded ICE JTAG的软件调试方式。ARM9系列兼容ARM7系列,而且能够比ARM7进行更加灵活的设计。

ARM9系列处理器主要应用于下面一些场合:

(1)下一代无线设备,包括视频电话和PDA(个人数字助理)等;

(2)数字消费品,包括机顶盒、家庭网关、MP3播放器和MPEG-4播放器等;

(3)成像设备,包括打印机、数码照相机和数码摄像机等;

(4)汽车、通信和信息系统。

3.ARM9E处理器系列

ARM9E系列为综合处理器,包括ARM926EJ-S、带有高速缓存处理器宏单元的ARM966E-S与ARM946E-S。该系列强化了数字信号处理功能,可应用于需要DSP与微控制器结合使用的情况;将Thumb技术和DSP都扩展到ARM指令集中,并具有Embedded ICE-RT逻辑(ARM的基于Embedded ICE JTAG软件调式的增强版本),更好地适应了实时系统的开发需要。同时,其内核在ARM9处理器内核的基础上使用了Jazelle增强技术,该技术支持一种新的Java操作状态,允许在硬件中执行Java字节码。

ARM9E系列处理器主要应用于下面一些场合:

(1)下一代无线设备,包括视频电话和PDA等;

(2)数字消费品,包括机顶盒、家庭网关、MP3播放器和MPEG-4播放器等;

(3)成像设备,包括打印机、数码照相机和数码摄像机等;

(4)存储设备,包括DVD(多用途数字光盘,又称数字影碟)或HDD(硬盘驱动器)等;

(5)工业控制,包括电机控制等;

(6)汽车、通信和信息系统的ABS(防抱死刹车系统)和车体控制;

(7)网络设备,包括VoIP(Voice over Internet Protocol)、WirelessLAN(无线局域网)和x DSL(Digital Subscriber Line,数字用户线路。“x”代表不同种类的数字用户线路技术)等。

4.ARM10E处理器系列

ARM10发布于1999年,具有高性能、低功耗的特点。ARM10E系列处理器采用了新的节能模式,提供了64位的Load/Store体系,支持包括向量操作的满足IEEE二进制浮点数算术标准(IEEE 754)的浮点运算协处理器,系统集成更加方便,拥有完整的硬件和软件开发工具。ARM10E系列包括ARM1020E、ARM1022E和ARM1026EJ-S这3种类型。

ARM10E系列处理器具体应用于下面一些场合:

(1)下一代无线设备,包括视频电话和PDA、笔记本式计算机和互联网设备等;

(2)数字消费品,包括机顶盒、家庭网关、MP3播放器和MPEG-4播放器等;

(3)成像设备,包括打印机、数字照相机和数字摄像机等;

(4)汽车、通信和信息系统等;

(5)工业控制,包括马达控制等。

5.ARM11处理器系列

ARM1136J-S发布于2003年,是针对高性能和高效能的应用而设计的。ARM1136J-S是第一个执行ARM V6架构指令的处理器,它集成了具有独立的loadstore和算术流水线的8级流水线。ARM V6指令包含了针对媒体处理的单指令多数据流(SIMD)扩展,采用特殊的设计以改善视频处理性能。

ARM1136JF-S为了进行快速浮点运算,在ARM1136J-S增加了向量浮点单元。

6.SecurCore处理器系列

SecurCore系列涵盖了SC100、SC110、SC200和SC210处理器核。该系列处理器主要针对新兴的安全市场,以一种全新的安全处理器设计,为智能卡和其他安全IC(智能)开发提供独特的32位系统设计,并具有特定的反伪造方法,有助于防止对硬件和软件的盗版。

SecureCore系列处理器主要应用于一些安全产品及应用系统,包括电子商务、电子银行业务、网络、移动媒体和认证系统等。

7.Strong ARM和Xscale处理器系列

Strong ARM处理器最初是安谋国际科技公司与Digital Semiconductor公司合作开发的,现在由英特尔公司单独许可,在低功耗、高性能的产品中应用很广泛。Strong-ARM采用哈佛架构,具有独立的数据和指令Cache,有MMU。Strong ARM是第一个包含5级流水线的高性能ARM处理器,但它不支持Thumb指令集。

英特尔公司的Xscale是Strong ARM的后续产品,在性能上有显著改善。Xscale执行V5TE架构指令,也采用哈佛结构,类似于Strong ARM,也包含一个MMU。Xscale已经被英特尔公司卖给了美满(Marvell)公司。(https://www.xing528.com)

8.Cortex处理器系列

基于ARM V7版本的ARM Cortex(醋睿)系列产品由A(应用处理)、R(实时控制)、M(微控制)3个系列组成,具体分类延续了一直以来ARM面向具体应用设计CPU的思路。

Cortex-M3处理器是基于ARM V7-M架构的处理器,采用了纯Thumb2指令的执行方式,具有极高的运算能力和中断响应能力。主要应用于汽车车身系统、工业控制系统和无线网络等对功耗和成本敏感的嵌入式应用领域。目前最便宜的基于该内核的ARM单片机售价为1美元。

Cortex-R4处理器是首款基于ARM V7架构的高级嵌入式处理器,其主要目标为产量巨大的高级嵌入式应用系统,如硬盘、喷墨式打印机以及汽车安全系统等。

Cortex-A8处理器是安谋国际科技公司所开发的基于ARM V7架构的首款应用级处理器,其特色是运用了可增加代码密度和加强性能的技术、可支持多媒体以及信号处理能力的NEON技术以及能够支持Java和其他文字代码语言的提前和即时编译的Jazelle RTC技术。众多先进的技术使Cortex-A8适用于家电以及电子行业等各种高端的应用领域。

6.2.3 ARM处理器工作状态

ARM处理器内核支持32位ARM指令集和16位Thumb指令集两种工作状态。这两种工作状态可以在程序中十分方便地进行切换。也就是说,程序可以一部分由32位指令编写,而另一部分采用16位指令编写。

这两种状态之间的切换只需要在跳转指令中用目标地址的最低来描述即可。无论是16指令字还是32位指令字,由于边界对准的原因,跳转的目标地址都应该是一个偶数,也就是说其最低位为0。如果要从ARM状态切换到Thumb状态,只要使跳转地址的最低位置为1,就可以使处理器切换到16位Thumb状态。跳回去时只需要用一个跳转指令加上一个目标地址就可以了,该过程描述如例6-1所示。

【例6-1】 ARM状态和Thumb状态切换示例

程序清单如下:

;从ARM状态转变为Thumb状态

LDRRO,=Lable+l//将目标地址最低位设为1

BXRO//跳转到目标地址,跳转后自动进入Thumb状态

;从Thumb状态转变为ARM状态

LDRRO,=Lable//将目标地址送到R0寄存器

BXRO//跳到目标地址,跳转后自动进入ARM状态。

所有的异常处理都在ARM状态中执行。如果异常发生在Thumb状态中,处理器会切换到ARM状态。在异常处理返回时,自动切换回到Thumb状态。

6.2.4 RM处理器工作模式

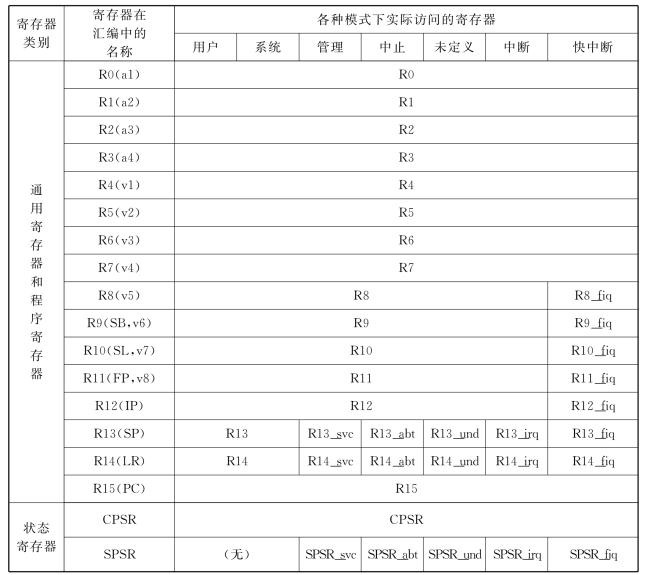

ARM体系结构的微处理器支持7种处理器模式,即用户模式、快中断模式、中断模式、管理模式、中止模式、未定义模式和系统模式。这7种模式中除用户模式外,其他模式均为特权模式。ARM内部寄存器和一些片内外设在硬件设计上只允许(或可选为只允许)在特权模式下访问。此外,特权模式下可以自由地切换处理器模式,而用户模式不能直接切换到别的模式。ARM处理器工作模式详见表6-2。

表6-2 ARM处理器工作模式

其中,快中断模式、中断模式、管理模式、中止模式和未定义模式被称为异常模式。这些异常模式除了可以通过程序切换进入外,也可以由特定的异常进入。当特定的异常出现时,处理器进入相应的模式。每种模式都有某些附加的寄存器,以避免异常退出时,用户模式的状态不可靠。

至于系统模式,它与用户模式一样,不能由异常进入,且使用与用户模式完全相同的寄存器。然而系统模式是特权模式,不受用户模式的限制。有系统模式,操作系统要访问用户模式的寄存器就比较方便。同时,操作系统的一些特权任务可以使用系统模式,以访问一些受控的资源,而不必担心异常出现时的任务状态变得不可靠。

6.2.5 ARM内部寄存器

在ARM处理器内部有37个用户可见的32位寄存器,其中31个通用寄存器、6个状态寄存器。这些寄存器并不是全都可以在同一时间被访问的,处理器状态和操作模式决定了程序员可以访问哪些寄存器。但在任何时候,通用寄存器RO~R14、程序计数器(PC)、一个或两个状态寄存器都是可访问的。

ARM状态下的寄存器包括通用寄存器和程序状态寄存器。表6-3所列为每种模式所能访问的寄存器。

表6-3 ARM状态各种模式下的寄存器

表6-3中,括号内为ATPCS中寄存器的命名,可以使用RN汇编伪指令将寄存器定义多个名字。其中,ADSl.2的汇编程序直接支持这些名称,但注意al~a4、vl~v4必须用小写字母。

1.通用寄存器

通用寄存器包括R0~R15,可以分为以下3类。

(1)未分组寄存器R0~R7

在所有运行模式下,未分组寄存器都指向同一个物理寄存器。这些未分组寄存器未被系统用作特殊的用途,因此,在中断或异常处理进行运行模式转换时,由于不同的处理器运行模式均使用相同的物理寄存器,可能会造成寄存器中数据的破坏,这一点在进行程序设计时应引起注意。

(2)分组寄存器R8~R14

R8~R14所对应的物理寄存器取决于当前的处理器模式。几乎所有允许使用通用寄存器的指令都允许使用分组寄存器。寄存器R8~R12有两个分组的物理寄存器,一个用于除FIQ模式之外的所有寄存器模式(R8~R12),另一个用于FIQ模式(R8_fiq~R12_fiq)。

寄存器R13和R14分别有6个分组的物理寄存器,其中1个用于用户和系统模式,其余5个分别用于5种异常模式。寄存器R13通常作为堆栈指针SP。在ARM指令集中,由于没有以特殊方式使用R13的指令或其他功能,只是习惯上都这样使用。

寄存器R14(也称为链接寄存器或LR)在结构上有两个特殊功能。

首先,在每种模式下,模式自身的R14版本用于保存子程序返回地址。当使用BL 或BLX指令(注意:ARM7TDMI没有BLX指令)调用子程序时,R14设置为子程序返回地址。子程序返回通过将R14复制到PC来实现。通常有两种方式。

一是执行下列指令之一:

MOV PC,LR

BX LR

二是在子程序入口,使用下列形式的指令将R14存入堆栈:

STMFD SP!,{<registers>,LR}

并使用匹配的指令返回,即

LDMFD SP!,{<registers>,PC}

其次,当发生异常时,将寄存器R14对应的异常模式版本设置为异常返回地址(有些异常有一个小常量的偏移)。异常返回的执行类似于子程序返回,只是使用稍微不同的指令来确保被异常中断的程序状态能够恢复。

寄存器R14在其他任何时刻都可作为一个通用寄存器。

(3)程序计数器R15

寄存器R15用作程序计数器PC。在ARM状态下,位[1:O]为0,位[31:2]用于保存PC;

在Thumb状态下,位[0]为O,位[31:1]用于保存PC。虽然可以用作通用寄存器,但是某些指令在使用R15时有一些特殊限制,若不注意,执行的结果将是不可预测的。

对R15的使用有一些特殊的限制,当违反了这些限制时,程序的执行结果将是未知的。

这些限制包括两方面的内容。

一方面,读程序计数器的限制。当使用STR或STM指令保存R15时,读取的值是指令的地址加上8B或12B。偏移量是8或12与芯片有关,故最好避免使用STR或STM指令保存R15。

另一方面,写程序计数器的限制。当执行一条写R15的指令没有超出任何对它使用的限制时,写入R15的正常结果值被当成一个指令地址,程序从这个地址处继续执行(相当于执行一次无条件跳转)。

由于ARM指令以字为边界,因此写入R15值的bit[l:0]通常为00。具体的规则取决于所使用结构的版本。

6.2.6 ARM处理器产品

许多半导体公司持有ARM授权,如爱特梅尔、博通(Broadcom)、思睿逻辑(Cirrus Logic)、飞思卡尔(于2004年从摩托罗拉公司独立出来)、美国高通(Qualcomm)、富士通、英特尔(借由和Digital的控诉调停)、IBM,英飞凌科技,任天堂,恩智浦半导体(于2006年从飞利浦独立出来)、OKI电气工业、三星电子、夏普(Sharp)、意法半导体(STMicroelectronics)、德州仪器和VLSI等公司,这些公司均拥有各个不同形式的ARM授权。

各个公司的产品都有自己的特点和应用领域,但是基本上都遵循以ARM内核来区别其市场定位和应用领域。不同ARM内核的产品,其主要市场定位和应用方向描述如下。

1.ARM Cortex系列

该系列包括Cortex TM-A系列,开放式操作系统的高性能处理器;Cortex-R系列,面向实时应用的卓越性能;Cortex-M系列,面向具有确定性的微控制器应用的成本敏感型解决这三种方案。

Cortex TM-A应用程序处理器在高级工艺节点中可实现高达2GHz+标准频率的卓越性能,从而可支持下一代的移动Internet设备。这些处理器具有单核和多核种类,最多提供4个具有可选NEONTM多媒体处理模块和高级浮点执行单元的处理单元。应用包括智能手机、平板电脑、上网本、电子书阅读器、数字电视、家用网关和各种其他产品。

Cortex-M系列处理器主要是针对微控制器领域开发的,在该领域中,既需进行快速且具有高确定性的中断管理,又需将门数和可能功耗控制在最低。应用包括信号设备智能传感器汽车电子和气囊。

而Cortex-R系列处理器的开发则面向深层嵌入式实时应用,对低功耗、良好的中断行为、卓越性能以及与现有平台的高兼容性这些需求进行了平衡考虑。应用包括汽车制动系统动力传动解决方案、大容量存储、控制器联网和打印等。

2.经典的ARM处理器系列

该系列包括ARM11TM系列,基于ARMv6架构的高性能处理器;ARM9TM系列,基于ARMv5架构的常用处理器;ARM7系列,面向普通应用的经典处理器。

ARM经典处理器适用于那些希望在新应用中使用经过市场验证技术的组织。这些处理器提供了许多的特性、卓越的功效和范围广泛的操作能力,适用于成本敏感型解决方案。这些处理器每年都有数十亿的发货量,因此可确保设计者获得最广泛的体系和资源,从而最大限度地减少集成过程中出现的问题并缩短上市时间。

3.ARM专家型处理器系列

该系列包括SecurCoreTM,面向高安全性应用的处理器;FPGA Cores,面向FPGA的处理器。ARM专家型处理器旨在满足特定市场的苛刻需求。

SecurCore处理器在安全市场中用于手机SIM卡和识别应用,集成了多种既可为用户提供卓越性能,又能检测和避免安全攻击的技术。

FPGA构造的处理器,在保持与传统ARM设备兼容的同时又方便用户,产品快速上市。此外,这些处理器具有独立于构造的特性,因此开发人员可以根据应用选择相应的目标设备,而不会受制于特定供应商。

6.3 MIPS体系微处理器

6.3.1 MIPS微处理器简介

美普思科技公司(MIPS)设计RISC处理器始于1980年代初,由斯坦福大学轩尼诗(Hennessy)教授领导的研究小组研制出来。1984年成立美普思技术公司,1992年美普思公司被美国硅图公司(SGI)收购,1998年,美普思公司脱离了硅图公司,成为美普思技术公司。该公司是一家设计和制造高性能、高档嵌入式32位和64位处理器的厂家,在高档嵌入式微处理器领域占有重要地位。

MIPS为“Micro computer without interlocked pipeline stages”(“无互锁流水线微型计算机”)的缩写,其最大特点在于通过结构设计上的优化实现无互锁的流水线结构。MIPS的系统结构及设计理念比较先进。在设计理念上,MIPS强调软硬件协同提高性能,同时简化硬件设计。其指令系统包括两种类型:一种是通用处理器指令体系MIPS I、MIPS II、MIPS III、MIPS IV到MIPS V;另一种是嵌入式指令体系结构MIPS16、MIPS32到MIPS64。经过几十年的发展,其体系结构均已经十分成熟。

美普思公司于1986年推出R2000处理器,1988年推R3000处理器,1991年推出第一款64位商用微处器R4000。之后又陆续推出R8000(于1994年)、R10000(于1996年)和R12000(于1997年)等型号。

随后,美普思公司的战略发生变化,把重点放在嵌入式系统。1999年,美普思公司发布MIPS32和MIPS64架构标准,为未来MIPS处理器的开发奠定了基础。新的架构集成了所有原来NIPS指令集,并且增加了许多更强大的功能。美普思公司陆续开发了高性能、低功耗的32位处理器内核(core)MIPS3 24Kc与高性能64位处理器内核MIPS64 20Kc。2000年,美普思公司发布了针对MIPS32 24Kc的版本以及64位MIPS 64 20Kc架构的处理器内核。MIPS32 24Kc架构处理器是采用MIPS技术特定为片上系统SOC(System-On-a-Chip)而设计的高性能、低电压32位MIPS RISC内核,采用MIPS32TM体系结构,并且具有R4000存储器管理单元(MMU)以及扩展的优先级模式,使得这个处理器与目前嵌入式领域广泛应用的R3000和R4000系列(32位)微处理器完全兼容。新的64位MIPS处理器是RM9000x2,从“x2”这个标记判断,它包含了不是一个而是两个均具有集成二级高速缓存的64位处理器。RM9000x2主要针对网络基础设施市场,具有集成的DDR内存控制器和超高速的Hyper Transport I/O链接。64位处理器MIPS 64 20Kc的浮点能力强,可以组成不同的系统,从一个处理器的Octane工作站到64个处理器的Origin 2000服务器。这种CPU更适合图形工作站使用。MIPS最新的R12000芯片已经在SGI的服务器中得到应用,其主频最大可达400MHz。

目前,MIPS处理器已经完全退出了桌面市场,全面转入嵌入式领域,其产品在大数据吞吐量的嵌入式应用中占有重要地位。我国自主研发的龙芯2号微处理器和其前代龙芯1号,都是采用的64位MIPS指令架构。

6.3.2 MIPS架构性能特点

从高端多核解决方案到紧凑型内核,所有MIPS处理器内核均基于相同的高性能MIPS32基础架构进行设计。

MIPS内核的主要性能改进来自于内核执行单元的功能增强,通过实现较长的流水线级数、超标量和多线程微架构来提高处理器的最大工作时钟频率,通过在标准架构中加入高速存储器接口、高效缓存控制器、存储器管理单元、大量寄存器组以及浮点加速器等设计功能来获得附加性能。

MIPS32架构标配32个通用寄存器(General Purpose Register,GPR),其中每个寄存器的位宽为32位。在芯片设计阶段可以对MIPS配置更多的通用寄存器组(每组32个),以用作附加数据存储或者分配给专用向量中断控制器逻辑的“影子寄存器”,在传统软硬件方法的基础上可显著减少中断延时和现场切换时间。

利用硬件乘除单元(Multiply Divide Unit,MDU)以及多个带符号/无符号乘法、除法和乘加(MAC)指令的软件支持,可有效提高MIPS32架构的信号处理性能。MIPS架构对MDU采用独立的流水线,使其可以与整数流水线并行工作。

与ARM处理器相比较,MIPS具有以下特点。

(1)以RISC技术为基础,并与可扩展的硬件和软件设计相结合,MIPS架构比ARM架构提供了更高性能、更低功耗和更为紧凑的设计。MIPS起源于高性能工作站和服务器的设计,而ARM的初衷是针对低端移动系统开发的基本内核。MIPS以其高性能产品的开发经验和设计优势进入主流嵌入式系统市场,而ARM传统架构中延续的种种方面限制其所能达到的性能等级,这使其与MIPS相比处于不利地位。

(2)MIPS32 4K?处理器内核(包括MIPS32 M4K?内核)比同级的ARM Cortex-M系列内核的性能更加优良,应用程序的运行速度更快。一部分原因是其采用了更高效的MIPS ISA和经过优化的软件工具,但主要原因是MIPS架构优越的设计功能可实现更高的性能和执行效率,包括对单片机设计中实现的典型功能进行加速。

(3)MIPS内核包含32个GPR,而ARM内核只包含16个GPR。这减少了寄存器溢出,从而实现更高的性能。

(4)MIPS架构主要执行单操作指令,而ARM指令在写入GPR之前要执行多次操作(例如移位操作数、运算、检查条件位以及其他操作)。这使得MIPS可以更容易地达到较高的时钟频率。

(5)与ARM相比,MIPS架构工作时采用的存储器寻址模式更简单,从而更容易达到较高的时钟工作频率。

(6)MIPS架构的预测执行较少,这最大程度地降低了逻辑复杂性,并使MIPS内核可达到较高的频率。M4K和M14K无需分支预测,而ARM内核采用了复杂的分支预测逻辑。

(7)MIPS架构实现了带延迟的分支,而ARM架构未实现,因此在短流水线设计时,MIPS可实现更高的效率。

(8)MIPS同时提供32位和64位架构,均可向下兼容并且更高性能的MIPS64也提供向下兼容。而ARM只提供32位架构,并且不是所有版本都支持向下兼容。

6.4 PowerPC体系微处理器

6.4.1 PowerPC微处理器简介

Power PC(Performance Optimization With Enhanced RISC-Performance Computing,有时简称PPC)是一种精简指令集(RISC)架构的中央处理器(CPU),其基本的设计源自IBM公司的POWER(Performance Optimized With Enhanced RISC,《IBM Connect电子报》2007年8月号译为“增强RISC性能优化”)架构。POWER是苹果公司、IBM公司、摩托罗拉公司于1991年组成的AIM联盟所发展出的微处理器架构。PowerPC是整个AIM联盟平台的一部分,并且是到目前为止唯一的一部分。但自2005年起,苹果电脑已将旗下电脑产品转用Intel CPU。

Power PC的历史可以追溯到在1990年随RISC System/6000一起被介绍的IBM POWER架构。该设计是从早期的RISC架构(比如IBM 801)与MIPS架构的处理器得到灵感的。1990年代,IBM、Apple和摩托罗拉开发PowerPC芯片成功,并制造出基于PowerPC的多处理器计算机。Power PC架构的特点是可伸缩性好、方便灵活。第一代PowerPC采用0.6微米的生产工艺,晶体管的集成度达到单芯片300万个。1998年,铜芯片问世,开创了一个新的历史纪元。2000年,IBM开始大批推出采用铜芯片的产品,如RS/6000的X80系列产品。铜技术取代了沿用了30年的铝技术,使硅芯片多CPU的生产工艺达到了0.20微米的水平,单芯片集成2亿个晶体管,大大提高了运算性能;而1.8V的低电压操作(原为2.5V)大大降低了芯片的功耗,容易散热,从而大大提高了系统的稳定性。

Power PC处理器的发展可以分为两个阶段,即AIM(Apple-IBM-Motorola)联盟阶段和Power.org阶段,而其指令集直到2004年才形成第一个版本Power ISA 2.01,如今已更新到Power ISA2.06,加入了虚拟化、多核等功能,并分化出嵌入式(Book-E)和服务器两个分支。Power PC处理器因此也可分为经典PowePC处理器和Book-E处理器。

经典PowerPC处理器和Book-E处理器的主要区别在于MMU、启动模式和异常向量地址。

首先,前者支持实地址模式、块模式和页模式三种地址翻译模式,而后者则仅支持增强的可变长度的页地址模式。

其次,前者启动后会立即跳转到复位异常向量(0x100或者0xfff00100)执行并进入实地址模式,而后者则直接跳到有效地址空间的最后4个字节(0x FFFFFFFC)处执行,并且在处理器默认映射的有效地址最后4K地址空间中完成相应的MMU配置工作后才能跳出这段地址空间执行。

最后,前者的异常向量地址是固定的,后者则可以通过IVPR和IVORn寄存器来配置每一个异常向量的地址。

6.4.2 PowerPC体系结构特点

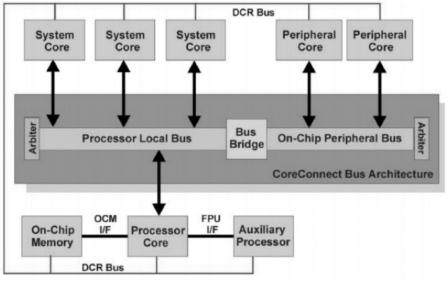

Power PC内核采用RISC体系结构,它由一个五级流水线、指令和数据分离的高速缓冲器、存储器管理单元(MMU)、调试和其他功能的接口组成。PowerPC内核与内核外的各种主从设备通过片上总线连接,详见图6-2所示。

Power PC采用的双处理器结构既提供了程序运行的通用处理器,又提供了用于通信用处的特殊通信处理器(CPM)。

32位PowerPC的结构特点如下:

(1)32个32位通用寄存器(GPRs);

(2)寄存器支持用户级指令集(不包括浮点指令),包括integer exception register (XER)、condition register(CR)、link register(LR)、counter register(CTR);

(3)时间加减及寄存器;

(4)管理级寄存器,与PowerPC定义兼容

(5)Configuration——Machine Status Register(MSR);

(6)Exception model——Save/restore registers 0 and 1(SRR0 and SRR1),DSI status register(DSISR),data address register(DAR);

(7)PowerPC减量器;

(8)PowerPC时基和实时时钟(RTC)。

PowerPC处理器寄存器分为两大类:专用寄存器和非专用寄存器。其中,非专用寄存器包括32个通用目的寄存器(GPR)、32个浮点寄存器(FPR)、条件寄存器(CR)、浮点状态和控制寄存器(FPSCR);专用寄存器主要包括连接寄存器(LR)、计数寄存器(CTR)、机器状态寄存器(MSR)以及时间基准寄存器(TBL/TBU)等。专用寄存器组可控制调试工具、定时器、中断、存储控制属性、其他结构处理器资源。PPC4xx系列处理器和DCR寄存器还需要用专门的指令访问。除此以外,该处理器还有另外两个特点。

第一,Power PC处理器可以运行于两个级别,即用户模式和特权模式。用户模式下,仅有GPR、FPR、CR、FPSCR、LR、CTR、XER以及TBL/TBU可以访问。从Power ISA 2.05开始,DCR寄存器也可以在通过用户模式DCR访问指令进行访问。

第二,PowerPC处理器没有专用的栈指针寄存器和PC指针寄存器,也就是说,硬件不负责维护调用栈。

图6-2 PowerPC的片上总线示意图

6.4.3 常用PowerPC处理器

经典PowerPC的代表是IBM和Motorola/Freescale的60x系列处理器,包括Motorola/Freescale的MPC8XX/MPC82XX/MPC83XX/MPC86XX/MPC5XXX系列和Motorola/Freescale/IBM的74xx/750系列。Book-E处理器则包括了IBM/AMCC (APM)的PPC4XX、Motorola/Freescale的PPC85XX系列和Qor IQ系列。尽管它们的产品不一样,但都采用了PowerPC的内核。这些产品大都用在嵌入式系统中。

Power PC处理器家族包括的一些极为经典的通信处理器。

1.MPC860

MPC860 Power QUICC内部集成了微处理器和一些控制领域的常用外围组件,特别适用于通信产品。Power QUICC可以被称为MC68360在网络和数据通信领域的新一代产品,它提高了器件运行的各方面性能,包括器件的适应性、扩展能力和集成度等。类似于MC68360 QUICC,MPC860 Power QUICC集成了两个处理块,一个处理块是嵌入的PowerPC核,另一个是通信处理模块(CPM),与MC68360的CPM基本类似。由于CPM分担了嵌入式PowerPC核的外围工作任务,这种双处理器体系结构的功耗要低于传统体系结构的处理器。

2.MPC8245

MPC8245集成PowerPC处理器适用于那些对成本、空间、功耗和性能都有很高要求的应用领域。该器件有较高的集成度,它集5个芯片于一体,从而降低了系统的组成开销。高集成度的结果是简化了电路板的设计,降低了功耗和加快了开发调试时间。这种低成本多用途的集成处理器的设计目标是使用PCI接口的网络基础结构、电讯和其他嵌入式应用。它可用于路由器、接线器、网络存储应用和图像显示系统。

3.MPC8260

MPC8260 Power QUICC II是目前最先进的为电信和网络市场设计的集成通信微处理器。高速的嵌入式PowerPC内核,连同极高的网络和通信外围设备集成度,摩托罗拉公司为用户提供了一个全新的整个系统解决方案来建立高端通信系统。MPC8260 Power QUICC II可以称作是MPC860 Power QUICC的下一代产品,它在各方面提供更高的性能,包括更大的灵活性、扩展能力和更高的集成度。与MPC860相似,MPC8260也有两个主要的组成部分,即嵌入的PowerPC内核和通信处理模块(CPM)。由于CPM分担了嵌入式Power PC核的外围工作任务,这种双处理器体系结构功耗要低于传统体系结构的处理器。CPM同时支持3个快速的串行通信控制器(FCC)、两个多通道控制器(MCC)、4个串行通信控制器(SCC)、两个串行管理控制器(SMC)、1个串行外围接口(SPI)和1个I2C接口。PowerPC内核和CPM的组合,加之MPC8260的多功能和高性能,为用户在网络和通信产品的开发方面提供了巨大的潜力并缩短了开发周期,加速了产品的上市。

Power PC处理器有非常强的嵌入式表现,因为它具有优异的性能、较低的能量损耗以及较低的散热量。除了像串行和以太网控制器那样的集成I/O,该嵌入式处理器与“台式机”CPU存在非常显著的区别。例如,4xx系列PowerPC处理器缺乏浮点运算,并且还使用一个受软件控制的TLB进行内存管理,而不是像台式机芯片中那样采用反转页表。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。