7.1 集成电路的设计流程[11]

集成电路的设计是指根据集成电路应用环境对芯片电路功能和性能的要求,在正确芯片应用配置、芯片电路形式、器件结构、工艺方案和封装形式的情况下,尽量减小芯片面积、降低集成电路设计制造成本,并保证实现规定的功能和要求的设计过程。

基于目前集成电路设计业与代工制造业的分离模式,在集成电路设计前,设计人员首先要根据设计芯片的基本要求,例如电源电压、电路速度要求等,选择合适的代工厂的某个工艺制程。而代工厂设计服务部门将经过前期工艺开发调试后确定好的一套工艺设计文件(Process Design Kits,PDK)交给集成电路设计单位。PDK文件包括芯片电路设计中仿真所用的该工艺线上的器件参数模型文件、版图设计层次定义、设计规则,以及晶体管、电阻、电容等元件和通孔(Via)、焊点(Pad)的基本版图结构,与设计工具相关联的设计规则检查(Design Rule Check,DRC)、版图电路与寄生参数提取(EXTraction,EXT )和电路对照(Layout-Versus-Schematic,LVS)用的技术文件。如果是设计逻辑电路,代工厂还要提供给设计单位带有基本技术参数的各种基本门电路、IP模块等。

集成电路设计单位根据集成电路的功能及技术指标要求,在选择合适的工艺制程和封装形式后,根据所设计芯片功能确定芯片电路的系统架构,然后利用PDK提供的工艺参数和电子设计自动化(Electronic Design Automation,EDA)工具,进行具体电路的设计,包括电路结构和电路中元器件的参数设计。如果是数字逻辑电路,则需要采用System-C 、Verilog HDL等设计硬件电路。通过电路仿真实现电路优化,接着完成版图设计及其DRC 、EXT 、LVS的检查验证,最后生成GDS-Ⅱ(Graphic Design SystemⅡ)的版图文件,交给代工厂。

代工厂根据设计单位提供的芯片GDS-Ⅱ格式的版图数据,制作芯片制造过程中需要的掩模(Mask),将版图数据定义的图形固化到一套掩模上。一张掩模对应于版图设计中的一层图形,也对应于芯片制造中的一道或几道工序。上述掩模被用于平面光刻工艺,这样将GDS-Ⅱ定义的图形有序地固化到芯片上,最终完成芯片的加工制造。掩模数、工艺线的特征尺寸、芯片面积以及封装的形式与测试决定了集成电路的制造成本,而掩模数、工艺线的自动化程度决定了芯片流片的周期,通常一次芯片加工流片的周期为2~3个月。代工厂完成芯片加工后,将裸片寄给集成电路设计单位。

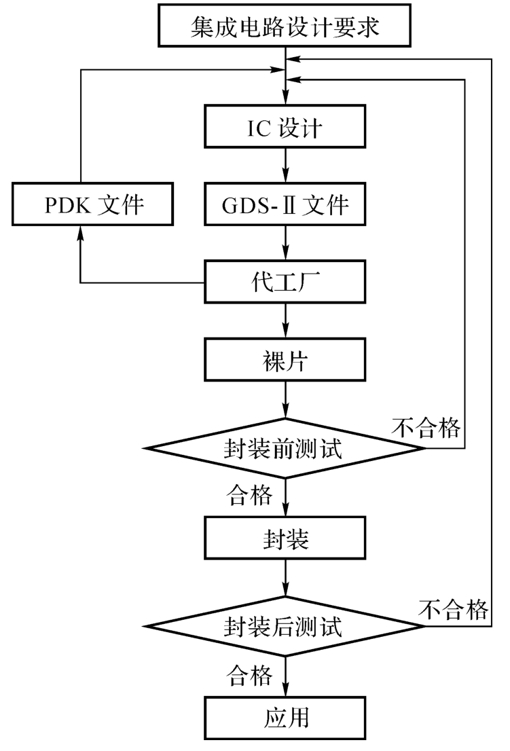

设计单位收到裸片后,可以委托测试公司也可以自行对其进行参数测试与性能测量,符合要求的进行封装,封装完成后还要进行测试、老化等,合格的进入出货,交到应用厂商,从而完成一次集成电路的设计、制造、测试、封装直至应用的全过程。整个集成电路的设计流程如图0-1所示。(https://www.xing528.com)

图0-1 集成电路的设计流程

集成电路在具体的设计过程中,首先要根据客户要求或项目研究目标确定所要设计的电路的详细功能、性能指标,即对所设计电路进行规格描述(Specification);然后选择合适的EDA工具进行集成电路设计(IC Design)。

从规格说明到GDS-Ⅱ件的产生,对于模拟集成电路和数字集成电路而言,其产生方法和过程有所不同。数字集成电路的设计过程通常包括功能级设计、行为级设计、逻辑综合、门级验证、布局布线等步骤,而模拟集成电路的设计过程一般包括电路设计、电路仿真性能优化、版图设计与验证等步骤。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。