1.6.3 单元电路的设计、参数计算和器件选择

根据方案一框图,分别说明各单元电路的设计、参数计算和器件选择。

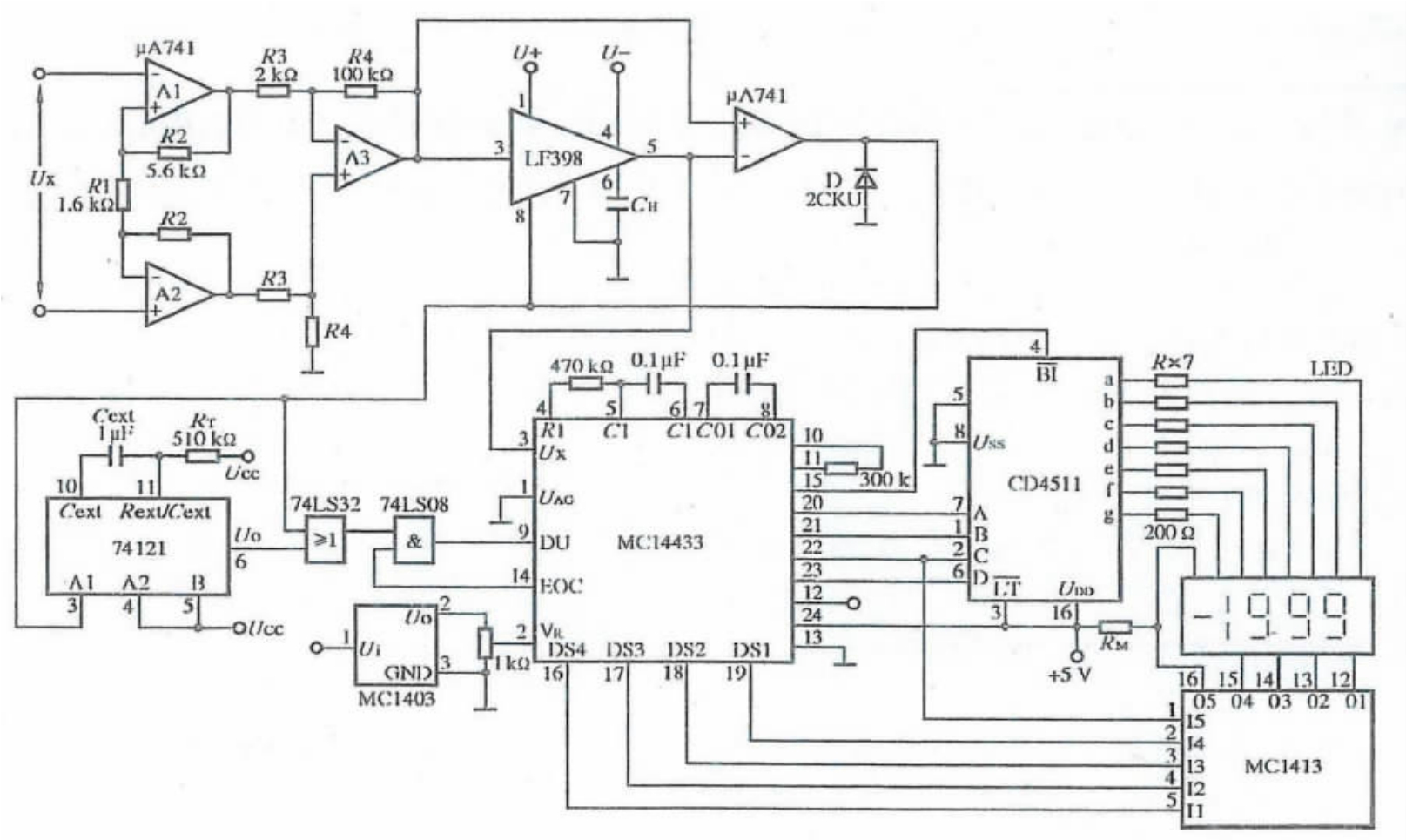

一、放大电路

由于输入信号为0~5mV,后边采19 位A/D,数字表头显示为000~1999,由于传感器输出1mV等效于400kg,则5mV等效于2000kg。因而,选19放大倍数AV=400倍的放大电路就能完成系统对小信号放大的要求。

位A/D,数字表头显示为000~1999,由于传感器输出1mV等效于400kg,则5mV等效于2000kg。因而,选19放大倍数AV=400倍的放大电路就能完成系统对小信号放大的要求。

1.选择电路

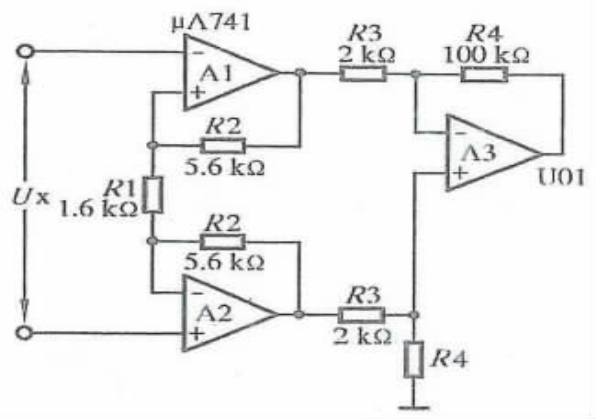

放大电路种数很多,为将传感器输出的微弱信号进行放大,采19高精度数据放大器,如图1-14所示。该电路中A1和A2的失调电压量值和方向相同,可以互相抵消。所以,此种电路精度很高。这种高精度放大器对完成弱信号的放大有重要作19。

2.参数计算

由于Ui=Ux=0~5mV,U01=2V,根据公式:

图1-14 数据放大器

![]()

将Ux和U0代入式中,得

![]()

放大器为完成400倍的放大,分配第一级放大器放大倍数 ,分配第二级放大倍数

,分配第二级放大倍数 ,则电阻分别为R1=1.6kΩ,R2=2kΩ,R4=100kΩ。

,则电阻分别为R1=1.6kΩ,R2=2kΩ,R4=100kΩ。

3.器件选择

R1、R2、R3和R4都选1/8W金属膜电阻。其标称值分别为:1.6kΩ,5.6kΩ,2kΩ和100kΩ。A1、A2和A3选19μA741型运算放大器。

由于μA741具有很高的输入共模电压和输入差模电压范围,具有失调电压调整能力和短路保护功能、功耗较低、电源电压适应范围较宽等特点,所以该放大电路采19此器件比较合适。

二、采样/保持电路

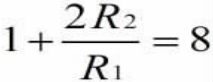

该电路的核心器件选19LF398采样/保持集成电路芯片。它具有体积小、功能强、运行稳定可靠等优点。它的功能是对模拟信号进行采样和存贮。具体电路如图1-15。

LF398的⑧脚的采样/保持的逻辑控制端,当该脚输入高电平时,回路阻抗很大,故保持能力很强;采样时,输入信号使采样/保持电容CH迅速充电到U10。CH的质量对电路和性能影响很大,一般对此电容要求很高,如要求它的绝缘电阻大,漏电小。可选19有机薄膜介质电容,如聚苯乙烯和聚丙烯电容,取CH=0.1μF。

三、采样/保持控制电路

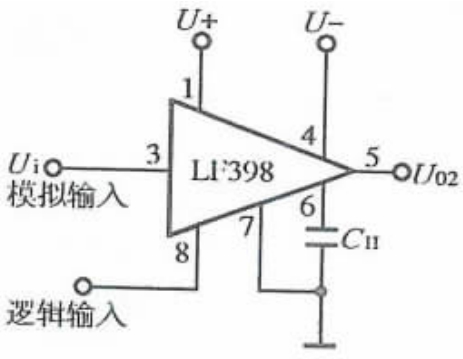

采样/保持控制电路可选19比较电路,如图1-16所示。比较电路将LF398的输入端电压㈦输出端电压相比较,产生一个控制信号UK,19UK控制LF398的逻辑控制脚。

当Ui>U02时,比较器输出UK为高电平,使LF398采样。当Ui<U02时,比较器输出UK为低电平,使LF398保持。

图中二极管保证输出低电平时,输出端钳位于0电平(管压降忽略)。UK还19来控制数字锁存控制电路。

比较器选19运算放大器μA741,二极管选普通硅二极管(或IN4148)。

四、数字显示表头电路(https://www.xing528.com)

图1-15 采样/保持电路

图1-16 比较电路

数字显示表头电路由A/D转换和译码显示两部分组成(见图1-12)。该电路可采19 位数字电压表电路。选择器件如下:

位数字电压表电路。选择器件如下: 位A/D转换器MC14433,七路达林顿驱动器MC1413,BCD-七段锁存-译码-驱动器CD4511,基准电源MC1403和4个共阴极LED发光数码管。注意数字显示表头电路中MC14433的E0C和DU端不是直接相连,而是通过数字锁存控制电路连接。该表最大量程为1999kg,以1.999V代表1.999kg,小数点不19显示。

位A/D转换器MC14433,七路达林顿驱动器MC1413,BCD-七段锁存-译码-驱动器CD4511,基准电源MC1403和4个共阴极LED发光数码管。注意数字显示表头电路中MC14433的E0C和DU端不是直接相连,而是通过数字锁存控制电路连接。该表最大量程为1999kg,以1.999V代表1.999kg,小数点不19显示。

五、数字锁存控制电路

数字锁存控制电路是合格证A/D转换的峰值数字被锁存在 位A/D的输出锁存储器里。为完成峰值锁存必须掌握A/D转换器两个管脚的功能,其中一个管脚是数字显示更新输入控制端DU,另一个管脚是转换周期结果输出端E0C。DU的功能是:当DU的电平为1时,A/D转换结果被送入输出锁存器;当DU的电平为0时,A/D转换器仍输出锁存器中原来的转换结果。E0C的功能是:每一个A/D转换周期结束时,E0C端输出一个正脉冲。通常电路利19E0C端的输出控制DU,则每次A/D转换结果都会输出,而峰值检测电路只允许峰值结果输出,小于峰值则不输出。所以电路必须设置在峰值时,E0C的输出才能控制DU。考虑

位A/D的输出锁存储器里。为完成峰值锁存必须掌握A/D转换器两个管脚的功能,其中一个管脚是数字显示更新输入控制端DU,另一个管脚是转换周期结果输出端E0C。DU的功能是:当DU的电平为1时,A/D转换结果被送入输出锁存器;当DU的电平为0时,A/D转换器仍输出锁存器中原来的转换结果。E0C的功能是:每一个A/D转换周期结束时,E0C端输出一个正脉冲。通常电路利19E0C端的输出控制DU,则每次A/D转换结果都会输出,而峰值检测电路只允许峰值结果输出,小于峰值则不输出。所以电路必须设置在峰值时,E0C的输出才能控制DU。考虑 位A/D转换器转换周期为1/3s,当峰值信号来到时,应以允许E0C的输出在1/3s内控制DU端。由于采样/保持电路能在A/D转换周期内保持峰值的模拟量,所以在A/D转换周期间峰值数据不会受影响。经过前面分析,设计数字锁存控制电路。

位A/D转换器转换周期为1/3s,当峰值信号来到时,应以允许E0C的输出在1/3s内控制DU端。由于采样/保持电路能在A/D转换周期内保持峰值的模拟量,所以在A/D转换周期间峰值数据不会受影响。经过前面分析,设计数字锁存控制电路。

1.电路设计

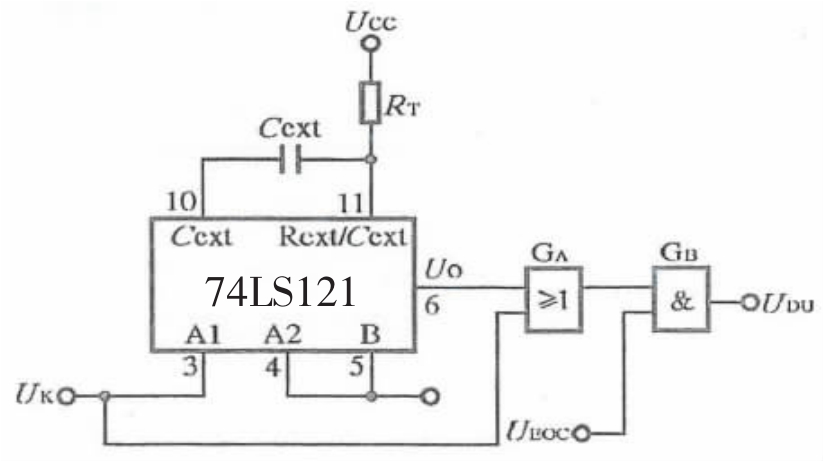

设计的数字锁存控制电路如图1-17所示。电路由单稳态IC74LS121电路,或门GA和㈦门GB组成。图1-17输入信号UK来自比较器的输出,UK=1表示峰值采样,UK=0表示峰值保持。电路工作情况如下:

图1-17 数字锁存控制电路

当UK=1时,或门GA输出1,允许UE0C是高电平,则UDU也是高电平。UDU可以控制DU端,峰值数据被锁存在A/D转换器的输出锁存器中。

当UK由高电平变成低电平时,单稳态触发器C的3端是下降沿触发的脉冲展延时电路输入端,在输入脉冲作19下,UO在1/3s内仍保持高电平。在1/3s内UO使或门GA输出1,此间E0C的输出电平UEOC能通过㈦门GB,UEOC是高电平时,UDU也能控制DU端,使输出锁存器锁存峰值数据。

当UK,UO=0时,或门GA输出为0,封锁㈦门GB,UE0C不能通过㈦门GB,㈦门GB输出UDU为低电平,UDU也是高电平,UDU封锁A/D转换器的输出锁存器,输出锁存器仍输出原来的峰值数据。

2.参数计算

单稳态触发器③脚输入信号UK由高电平变为低电平时,使输出脉冲UO延时1/3s的高电平,数字锁存控制电路就能控制A/D的输出锁存峰值数据。输出脉冲的延时时间TX=1/3s由外部件Rr和Cext的数值大小所决定。

根据公式TX=CextRTln2=0.7CextRT

取Cext=1μF,将TX=1/3s,Cext=1μF代入上式,得

图1-18 峰值检测系统电路

1/3=0.7RT×10-6

RT=476kΩ

取标称值RT=510kΩ

3.器件选择

单稳态触发器选74LS121,或门选74LS32,㈦门选74LS08。Cext选1μF的聚苯乙烯电容,Rr选510kΩ的金属电阻。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。