A/D转换器芯片ADC0809片内有8路模拟选通开关,可分时采集8路模拟信号,其转换时间为100μs左右。

1.ADC0809的内部逻辑结构

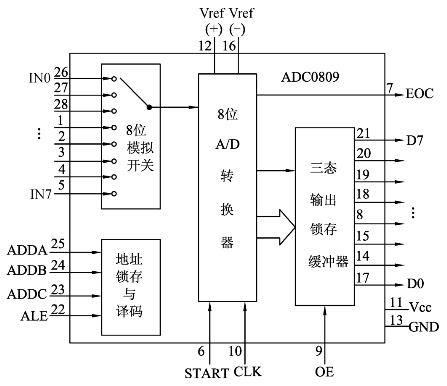

ADC0809的内部逻辑结构如图10-1所示。

图10-1 ADC0809内部逻辑结构

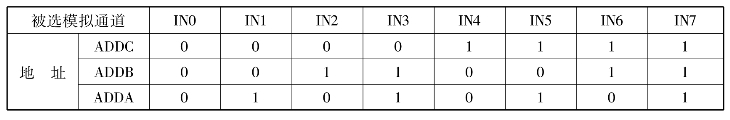

图中多路开关可选通8个模拟通道,允许8路模拟量分时输入,共用一个A/D转换器进行转换,这是一种经济的多路数据采集方法。地址锁存与译码电路完成对A、B、C三个地址位进行锁存和译码,其译码输出用于通道选择,转换结果通过三态输出锁存器存放、输出,因此可以直接与系统数据总线相连,表10-1为通道选择表。

表10-1 ADC0809模拟输入通道与地址译码的选通关系

八位逐次逼近式A/D转换器由控制与时序电路、逐次逼近寄存器、树状开关以及256R电阻阶梯网络等组成。

输出锁存器用于存放和输出转换得到的数字量。

2.引脚说明

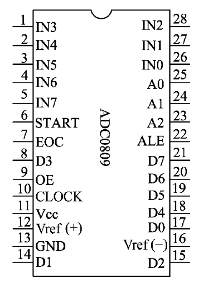

ADC0809芯片为28引脚双列直插式封装,其引脚排列见图10-2。

对ADC0809主要信号引脚的功能说明如下:

·IN0~IN7:8路模拟信号输入端。(https://www.xing528.com)

·ADDC(A2)、ADDB(A1)、ADDA(A0):地址输入端。

·ALE:地址锁存允许输入信号,在此脚施加正脉冲,上升沿有效,此时锁存地址码,从而选通相应的模拟信号通道,以便进行A/D转换。

图10-2 ADC0809引脚排列

·START:启动信号输入端,应在此脚施加正脉冲,当上升沿到达时,内部逐次逼近寄存器复位;在下降沿到达后,开始A/D转换过程。在转换期间,应保持低电平。

·EOC:转换结束,输出信号(转换结束标志),高电平有效。

·OE:输出允许信号,用于控制三条输出锁存器向单片机输出转换得到的数据。OE=1,输出转换得到的数据;OE=0,输出数据线呈高阻状态。

·CLOCK(CP、CLK):时钟信号输入端,因ADC0809的内部没有时钟电路,所需时钟信号必须由外界提供,外接时钟频率典型值为640kHz,极限值为1280kHz。

·Vcc:+5V单电源供电。

·Vref(+)、Vref(-):基准电压的正极、负极。一般Vref(+)接+5V电源,Vref(-)接地。

·D7~D0:数字信号输出端。

·GND:接地端。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。