由于本书后续章节相关内容主要以ARM7TDMI 内核为例进行介绍,因此,在这里有必要详细介绍ARM7TDMI。

(1)ARM7TDMI 概述

ARM7TDMI 是ARM 公司最早为业界普遍认可且得到了最为广泛应用的处理器核,特别是在手机和PDA 中,随着ARM 技术的发展,它已是目前最低端的ARM 核。 ARM7TDMI 是从最早实现了32 位地址空间编程模式的ARM6 核发展而来的,可以稳定地在低于5 V 的电源电压下可靠工作。 增加了64 位乘法指令、支持片上调试、Thumb 指令集和EmbededICE 片上断点和观察点。

ARM7TDMI 名称的具体含义是:

①ARM7:32 位ARM 体系结构4T 版本。

②T:支持“Thumb”16 位压缩指令集。

③D:支持片上调试(Debug),使处理器能够停止以响应调试请求。

④M:增强型Multiplier,与前代相比具有较高的性能且产生64 位的结果。

⑤I:“EmbeddedICE”硬件以支持片上断点和观察点。

(2)ARM7TDMI 组织结构

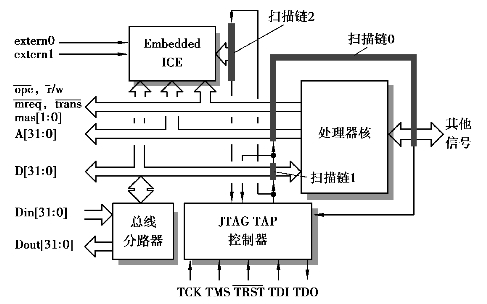

ARM7TDMI 组织如图2.13 所示。 ARM7TDMI 核采用了三级流水线结构,ARM7TDMI 重要的特性为:

①它实现ARM 体系结构版本4T,支持64 位结果的乘法,半字、有符号字节存取。

②支持Thumb 指令集,可降低系统开销。

③32 ×8 DSP 乘法器。

④32 位寻址空间-4GB 线性地址空间。

⑤它包含了EmbeddedICE 模块以支持嵌入式系统调试。

图2.13 ARM7TDMI 的组织

⑥调试硬件由JTAG 测试访问端口访问,因此,JTAG 控制逻辑被认为是处理器核的一部分。

⑦广泛的ARM 和第三方支持,并与ARM9 Thumb 系列ARM10 Thumb 系列和StrongARM处理器相兼容。

(3)ARM7TDMI 硬件接口

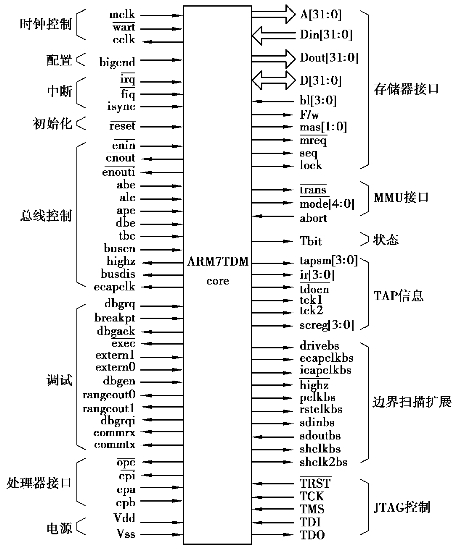

ARM7TDMI 的硬件接口外围信号如图2.14 所示,按接口信号的功能划分为存储器接口、MMU 接口、片上调试、JTAG 边界扫描扩展以及时钟接口等14 类接口信号。 各接口信号包括接口信号和接口控制信号。 下面详细说明每组信号的作用,必要时对单个信号和接口的时序进行详细说明。

1)存储器接口

存储器接口包括32 位地址(A[31:0])、双向数据总线D[31:0]、分开的数据输出Dout[31:0]和数据输入Din[31:0]总线以及10 个控制信号,这10 个控制信号及含义分别为:

②seq 指示存储器地址与前周期使用的地址连续(也可能相同)。

③lock 指示处理器应该保持总线,以确保SWAP 指令读相和写相的不可分割性。

④ 指示处理器执行的是读周期还是写周期。

指示处理器执行的是读周期还是写周期。

⑤mas[1:0]是对存储器访问大小的编码,指出访问的是字节、半字或字。

bl[3:0]由外部控制的使能信号,作用于数据输入总线上4 字节中每字节的锁存,这使得少于32 位位宽的宽存储器如8 位、16 位和32 位存储器易于实现与处理器接口;

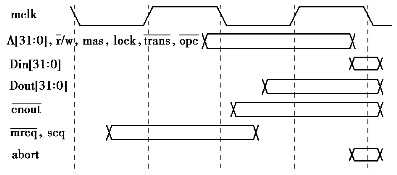

ARM7TDMI 存储器访问有四种周期类型,它是由 和seq 信号控制,主要接口信号的时序如图2.15 所示,这些信号主要是用于存储器接口逻辑的设计,在此不作详细介绍。

和seq 信号控制,主要接口信号的时序如图2.15 所示,这些信号主要是用于存储器接口逻辑的设计,在此不作详细介绍。

2)MMU 接口

ARM7TDMI 处理器核提供了MMU 的接口控制信号,进行存储器区域的访问控制:

① (传送控制)信号

(传送控制)信号

它指明处理器是工作在用户( =0)模式还是特权(

=0)模式还是特权( =1)模式,使得存储器的一些区域被限制为仅用于监控访问。

=1)模式,使得存储器的一些区域被限制为仅用于监控访问。

图2.14 ARM7TDMI 核的接口信号

图2.15 ARM7TDMI 核存储器和MMU 接口时序

②mode[4:0]信号

它们是反映处理器操作模式的信息,是CPSR 低5 位的反相,存储器管理很少使用,只是在调试时需要详细的模式信息时会用到。(https://www.xing528.com)

③中止(abort)

当一个存储器不允许访问时,在中止(abort)输入端发出信号,中止时序连同数据在时钟周期结束时有效。 如图2.15 所示。 一个中止的存储器访问使处理器执行预取或数据终止,这与在访问期间 的值有关。 如果希望支持存储器的只执行区域,MMU 也可以使用

的值有关。 如果希望支持存储器的只执行区域,MMU 也可以使用 信号,但是应该注意,这将排除使用代码区的文字库进行与PC 相关的读写。 因为这个原因,在ARM 系统中并不广泛使用对只执行区域的保护。

信号,但是应该注意,这将排除使用代码区的文字库进行与PC 相关的读写。 因为这个原因,在ARM 系统中并不广泛使用对只执行区域的保护。

3)总线控制

通常ARM7TDMI 核一经得到新地址就立即发出总线控制请求,以便MMU 或存储器控制器有最长的时间来处理它。 但是,在简单的系统中,地址总线直接连接到ROM 或SRAM,需要将原来的地址保持到周期的末端。 处理器核有一个由ape 控制的锁存器,当外部逻辑需要时,它可以给地址重新定时。

信号 用来指示ARM7TDMI 核执行写周期。 如果外部数据总线是双向的,就用

用来指示ARM7TDMI 核执行写周期。 如果外部数据总线是双向的,就用 来将dout[31:0]加到总线上。 有时希望推迟写操作,以使其他部件可以驱动总线,可以使用数据总线的使能信号dbe 来确保

来将dout[31:0]加到总线上。 有时希望推迟写操作,以使其他部件可以驱动总线,可以使用数据总线的使能信号dbe 来确保 在这个情况下保持无效。 处理器核必须停止(用

在这个情况下保持无效。 处理器核必须停止(用 ),直到总线可以使用为止。 dbe 按照外部逻辑的要求由外部定时。 其他总线控制信号

),直到总线可以使用为止。 dbe 按照外部逻辑的要求由外部定时。 其他总线控制信号 、

、 、abe、ale、tbe、busen、highz、busdis 和ecapclk 执行各种其他功能。 读者应参考相应的ARM7TDMI 数据手册来了解细节。

、abe、ale、tbe、busen、highz、busdis 和ecapclk 执行各种其他功能。 读者应参考相应的ARM7TDMI 数据手册来了解细节。

4)时钟控制

处理器所有的状态变化由存储器时钟mclk 控制。 尽管这个时钟可以由外部操纵,以便使处理器等待低速的读写,但它常常是一个自由的时钟,使用 跳过时钟周期。 内部时钟实际上正好是mclk 和

跳过时钟周期。 内部时钟实际上正好是mclk 和 的逻辑与,因此,只有当mclk 为低时,

的逻辑与,因此,只有当mclk 为低时, 才能变化。

才能变化。

eclk 时钟输出反映了处理器核使用的时钟,因此,它一般反映了mclk 在 门控后的行为,但在调试模式下它也反映了调试时钟的行为。

门控后的行为,但在调试模式下它也反映了调试时钟的行为。

5)状态输出

Tbit 信号表明当前处理器执行的是ARM 指令还是Thumb 指令。

6)配置

bigend 信号是用来在小端和大端格式之间选择,即选择字节按地址的存放位置顺序。

7)中断

是两个中断请求输入信号,

是两个中断请求输入信号, 为快速中断请求,

为快速中断请求, 为一般中断请求。

为一般中断请求。

8)初始化

信号是用来复位、启动处理器,处理器从地址0000000016 开始执行程序。

信号是用来复位、启动处理器,处理器从地址0000000016 开始执行程序。

9)Debug 接口

ARM7TDMI 实现了典型的ARM 调试结构。 EmbeddedICE 模块包含断点和观察点寄存器,使运行的代码能够停下来以便调试。 这些寄存器通过JTAG 测试端口使用扫描链2(见图2.13)进行控制。 当遇到断点或观察点时,处理器停下来并进入调试状态。 一旦进入调试状态,就可以使用扫描链1 强制指令进入指令流水线,检查处理器的寄存器。 对所有寄存器的数据进行存储,并将把它们的值送到数据总线,在数据总线上再用扫描链1 采样并移出。 访问特权模式寄存器需要强制加入指令来改变模式(注意,在调试状态,阻止从用户状态转换到特权模式的障碍已不存在)。

若需检查系统状态,可以让ARM 以系统速度访问存储器,然后立即切换回调试状态。

调试接口可扩展集成的EmbeddedICE 宏单元所提供的功能,它使外部硬件能够支持调试(通过dbgen),并发出异步的调试请求(在dbgrq 端口)或与指令同步的请求(在breakpt 端口)。 外部硬件通过dbgack 得知处理器核什么时候处于调试模式。 内部的调试请求信号在dbgrqi 输出。

外部事件可以通过extern0 和extern1 来触发观察点,而EmbeddedICE 观察点的匹配则由rangeout0 和rangeout1 端口的信号表示。

如果通信发送缓冲器是空的,在commtx 端口发出信号,如果接收缓冲器是空的,则在commrx 端口发出信号。

处理器在 端口指示当前在执行级的指令是否被执行。 如果指令没有被执行,就是它的条件码测试失败了。

端口指示当前在执行级的指令是否被执行。 如果指令没有被执行,就是它的条件码测试失败了。

10)协处理器接口

协处理器接口信号 、cpa 和cpb,另外提供给协处理器的信号是opc,它指示存储器访问是取指令还是取数据。 协处理器流水线跟随器使用它来跟踪ARM 指令的执行。 在不需要连接协处理器时,cpa 和cpb 应该连接高电平,这将使所有协处理器指令产生未定义指令陷阱。

、cpa 和cpb,另外提供给协处理器的信号是opc,它指示存储器访问是取指令还是取数据。 协处理器流水线跟随器使用它来跟踪ARM 指令的执行。 在不需要连接协处理器时,cpa 和cpb 应该连接高电平,这将使所有协处理器指令产生未定义指令陷阱。

11)电源

ARM7TDMI 核应在正常5 V 或3 V 电源电压下操作,这主要依赖于实现工艺技术和在核中使用的电路设计形式。

12)JTAG 接口

JTAP 控制信号符合标准的规定,这些控制信号通过专用引脚连到片外测试控制器。

13)TAP 信息

这些信号用来支持对JTAP 系统增加更多的扫描链,关于边境扫描扩展信号在下面详述。

tapsm[3:0]指示TAP 控制器所处的状态;ir[3:0]给出TAP 指令寄存器的内容;screg[3:0]是TAP 控制器当前所选择的扫描寄存器的地址;tck1 和tck2 形成一对非重迭时钟来控制扩展扫描链, 指示何时在tdo 有串行数据输出。

指示何时在tdo 有串行数据输出。

14)边界扫描扩展

ARM7TDMI 单元包含全部的JTAG TAP 控制器,以支持EmbeddedICE 功能,这个TAP 控制器能够支持任何通过JTAG 端口访问的片上扫描电路。 因此,提供了接口信号drivebs、ecapclkbs、icapclkbs、 、pclkbs、rstclkbs、sdinbs、sdoutbs、shclkbs 和shclk2bs,使任意的扫描路径都可加入到系统中。 读者应该参考相关的ARM7TDMI 数据手册,以详细了解这些信号各自的功能。

、pclkbs、rstclkbs、sdinbs、sdoutbs、shclkbs 和shclk2bs,使任意的扫描路径都可加入到系统中。 读者应该参考相关的ARM7TDMI 数据手册,以详细了解这些信号各自的功能。

(4)综合的ARM7TDMI-ARM7TDMI-S

标准的ARM7TDMI 处理器核是以物理版图提供的“硬” IP 核,定制为某种VLSI 实现工艺技术。 而ARM7TDMI-S 是ARM7TDMI 的一个可综合的版本,它是以高级语言描述的“软”IP 核,可以根据用户选择的目标工艺的单元库来进行逻辑综合和物理实现,它比“硬”的IP 核更易于转移到新的工艺技术上实现。 而综合出的整个核比“硬”核大50%,电源效率降低50%;同时,ARM7TDMI-S 在综合过程中存在支持关于处理器核功能的选项,这些选项会导致综合出处理器核较小而且的功能有所下降。 这些选项包括:

①可省略的EmbeddedICE 单元。

②用仅支持产生32 位结果的ARM 乘法指令的较小的和较简单的乘法器来替代完全64位结果的乘法器。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。