基于JTAG 仿真器的调试是目前ARM 开发中采用最多的一种方式。 大多数ARM 设计采用了片上JTAG 接口,并将它作为其测试和调试方法的重要组成。 JTAG 仿真器,也称为JTAG的在线调试器ICD(In-Circuit Debugger),是通过ARM 芯片的JTAG 边界扫描口进行调试的设备。 JTAG 仿真器连接比较方便,实现价格比较便宜,是通过现有的JTAG 边界扫描口与ARM CPU 核通信,实现了完全非插入式调试,连接比较方便,不使用片上资源,无须目标存储器,不占用目标系统的任何端口。 由于JTAG 调试的目标程序是在目标板上执行,仿真更加接近于目标硬件。 JTAG 仿真器是通过ARM 处理器特有的JTAG 边界扫描接口与目标机通信进行调试,并可以通过并口或串口、USB 口等与宿主机PC 通信。

基于JTAG 的ARM 的内核调试通道,具有典型的ICE(In-Circuit Emulator)功能,包含有Embedded ICE 模块的基于ARM 的SoC 芯片通过JTAG 调试端口与主计算机连接。 通过配置,支持正常的断点、观察点以及处理器和系统状态访问,完成调试。

为了对代码运行过程进行实时跟踪,ARM 提供了跟踪宏单元ETM(Embedded Trace Macrocell),通过嵌入式实时跟踪系统,实时观察其操作过程,对应用程序的调试将更加全面、客观和真实。

ARM 开发者通过EmbeddedICE 和ETM 获得了传统意义的在线仿真器(ICE)工具能够提供的各种功能。 通过这些技术能够全面观察应用代码的实时行为,并且能够设置断点、检查并修改处理器寄存器和存储器单元,还总是能够严格地反链接到高级语言源代码,构成ARM完整的调试、实时跟踪的完整解决方案并降低了开发成本。

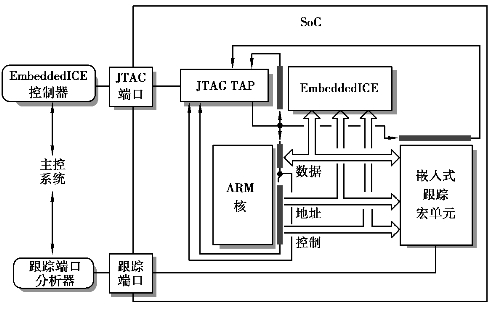

为了对代码运行过程进行实时跟踪,ARM 提供了完整的实时调试解决方案,如图2.12所示。

图2.12 实时调试系统结构

(1)JTAG 边界扫描

“JTAG 边界扫描”或IEEE1149 标准是由“测试联合行动组”(JTAG Joint Test Action Group)开发的针对PCB 的“标准测试访问接口和边界扫描结构”的标准。 由于JTAG 调试的目标程序是在目标版上执行,仿真更加接近于目标硬件。

支持这个测试标准的芯片必须提供五个专用信号接口:

①TRST:测试复位输入,用于测试接口的初始化。

②TCK:测试时钟,独立于任何系统时钟,用于控制测试接口的时序。

③TMS:测试模式选择信号,控制测试接口状态机的操作。

④TDI:测试数据输入,给边界扫描链或指令寄存器提供数据。

⑤TDO:测试数据输出。 输出边界扫描链的采样值,在芯片串行测试时,将数据传送给下一个芯片。(https://www.xing528.com)

(2)EmbeddedICE

ARM 的EmbeddedICE 调试结构是一种基于JTAG 的ARM 的内核调试通道,提供了传统的在线仿真系统的大部分功能,可以调试一个复杂系统中的ARM 核。

EmbeddedICE 是基于JTAG 测试端口的扩展,引入了附加的断点和观测点寄存器,这些数据寄存器可以通过专用JTAG 指令来访问,一个跟踪缓冲器也可用相似的方法访问。 ARM 核周围的扫描路径可以将指令加入ARM 流水线,并且不会干扰系统的其他部分,这些指令可以访问及修改ARM 和系统的状态。 ARM 的EmbeddedICE 具有典型的ICE 功能,如条件断点,单步运行。 由于这些功能的实现是基于片上JTAG 测试访问端口进行调试,芯片不需要增加额外的引脚,同时也避免使用笨重的、不可靠的探针接插设备完成调试。 且芯片中的调试模块与外部的系统时序分开,它可以直接运行在芯片内部的独立时钟速度。

EmbeddedICE 模块包括两个观察点寄存器和控制与状态寄存器。 当地址、数据和控制信号与观察点寄存器的编程数据相匹配时,也就是触发条件满足时,观察点寄存器可以中止处理器。 由于比较是在屏蔽控制下进行的,因此,当ROM 或RAM 中的一条指令执行时,任何一个观察点寄存器可配置为能够中止处理器的断点寄存器。

基于ARM 的包括EmbeddedICE 模块的系统芯片通过JTAG 端口和协议转换器与主计算机连接。 这种配置支持正常的断点、观察点以及处理器和系统状态访问,这是程序设计人员在本地或基于ICE 的调试中习惯采用的方式。 采用适当的主机调试软件,以较少的硬件代价得到完全的源代码级调试功能。

(3)TAP 控制器

测试访问端口(TAP)控制器,控制测试接口的操作。 在ARM7TDMI 处理器中,EmbeddedICE 逻辑部件提供了集成在芯片内的对内核进行调试的功能。 这部分功能是通过处理器上的TAP 控制器串行控制的。

(4)ARM 的嵌入式跟踪宏单元

在ARM 开发调试时,观察系统的实时操作对应用程序的调试是非常重要的。 EmbeddedICE 提供的断点及观察点将使处理器偏离正常执行序列,破坏了软件的实时行为,因而它不能完成上述功能。 ARM 结构的处理器采用嵌入式跟踪宏单元ETM 很好地解决了系统实时调试的问题。 由调试软件配置并通过标准JTAG 接口传输到ETM 上。 在程序执行时,ETM 可以通过产生对处理器地址、数据及控制总线活动的追踪(Trace)来获得处理器的全速操作情况。 利用已有的可编程跟踪器,追踪可配置为4 位、8 位或16 位数据总线宽度端口。 在实时仿真时,外设和中断程序依然能够继续运行。

在程序执行时通过产生对处理器地址、数据及控制总线活动的追踪来获得观察处理器全速操作情况时,需要巨大的数据带宽。 例如,一个以100 MHz 运行的ARM 处理器产生的接口信息超过1 GB/S。 将这些信息从芯片取出需要大量的引脚,具有这种能力的芯片是不经济的。 但是,专用设备的开发必然导致成本上升,可以采用数据压缩技术。 通过使用一系列数据压缩相关技术,ETM 可以将跟踪信息压缩到必要的长度,使这些信息依配置的不同通过不同的引脚传送到片外。 当不需要输出跟踪时,这些引脚还可以用于其他目的。

如图2.12 中,EmbeddedICE 单元支持断点和观察点功能并提供主机和目标软件的通信通道。 ETM 单元压缩处理器接口信息并通过跟踪端口送到片外。 这两个单元都由JTAG 端口控制。 SoC 外部的EmbeddedICE 控制器用于将主机系统连接到JTAG 端口,跟踪端口分析器使主机系统与跟踪端口对接。 主机通过一个网络可以与跟踪端口分析器和EmbeddedICE二者连接。

用户控制断点和观察点的设置并可以配置各种跟踪功能,既可以跟踪所有应用软件,也可以跟踪某一特定程序。 跟踪触发条件可以指定,跟踪采集可以在触发之前、之后或以触发为中心,可以选择跟踪是否包括数据访问。 跟踪采集可以是数据访问的地址、数据本身,也可以是两者兼有。

ETM 是使用软件通过JTAG 端口进行配置的,所使用的软件是ARM 软件开发工具的一个扩展。 跟踪数据从跟踪端口分析仪下载并解压,最终反链接到源代码。

有了EmbeddedICE 和ETM,ARM SoC 开发者在低成本的前提下获得了传统的在线仿真器(ICE)工具能够提供的所有功能。 通过这些技术能够全面观察应用代码的实时操作,并且能够设置断点、检查并修改处理器寄存器和存储器单元,能够真实、实时地严格反链接到高级语言源代码。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。