【摘要】:ARM 处理器对异常中断的响应过程如下:①将CPSR 的内容保存到将要执行的异常中断对应的SPSR 中,以实现对处理器当前状态、中断屏蔽位以及各条件标志位的保存。各异常中断模式都有自己相应的物理SPSR 寄存器。ARM 处理器对异常的响应过程可以用伪代码描述如下:每个异常模式对应有两个寄存器R13_、R14_分别保存相应模式下的堆栈指针、返回地址;堆栈指针可用来定义一个存储区域保存其他用户寄存器,这样异常处理程序就可以使用这些寄存器。

当发生异常时,除了复位异常立即中止当前指令外,处理器尽量完成当前指令,然后脱离当前的指令处理序列去处理异常。 ARM 处理器对异常中断的响应过程如下:

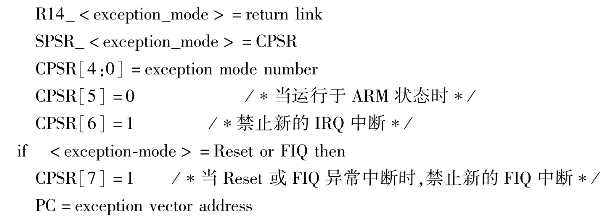

①将CPSR 的内容保存到将要执行的异常中断对应的SPSR 中,以实现对处理器当前状态、中断屏蔽位以及各条件标志位的保存。 各异常中断模式都有自己相应的物理SPSR 寄存器。

②设置当前状态寄存器CPSR 中的相应位:

a.设置CPSR 模式控制位CPSR[4:0],使处理器进入相应的执行模式。

b.设置中断标志位(CPSR[6] =1),禁止IRQ 中断。

c.当进入Reset 或FIQ 模式时,还要设置中断标志位(CPSR[7] =1)禁止FIQ 中断。

③将引起异常指令的下一条指令的地址保存到新的异常工作模式的R14,即R14_mode中,使异常处理程序执行完后能正确返回原程序。(https://www.xing528.com)

④给程序计数器(PC)强制赋值,使程序从表2.3 给出的相应的矢量地址开始执行中断处理程序,一般地说,矢量地址处将包含一条指向相应程序的转移指令,从而可跳转到相应的异常中断处理程序处执行异常中断处理程序。

ARM 处理器对异常的响应过程可以用伪代码描述如下:

每个异常模式对应有两个寄存器R13_<mode >、R14_<mode >分别保存相应模式下的堆栈指针、返回地址;堆栈指针可用来定义一个存储区域保存其他用户寄存器,这样异常处理程序就可以使用这些寄存器。

FIQ 模式还有额外的专用寄存器R8_fiq ~R12_fiq,使用这些寄存器可以加快快速中断的处理速度。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。