【摘要】:所有处理器模式下都可以访问当前的程序状态寄存器。图2.8程序状态寄存器程序状态寄存器的条件码标志N、Z、C、V 均为条件码标志位。在Thumb 状态下,仅有分支指令是有条件执行的。表2.4各条件码的含义程序状态寄存器的控制位最低8 位I、F、T 和M[4:0]位用作控制位。②T 位:ARM 体系结构V5 及以上的版本的T 系列处理器,当该位为“1”时,程序运行于Thumb 状态,否则,运行于ARM 状态。

所有处理器模式下都可以访问当前的程序状态寄存器(CPSR)。 CPSR 包含条件码标志、中断禁止位、当前处理器模式以及其他状态和控制信息。

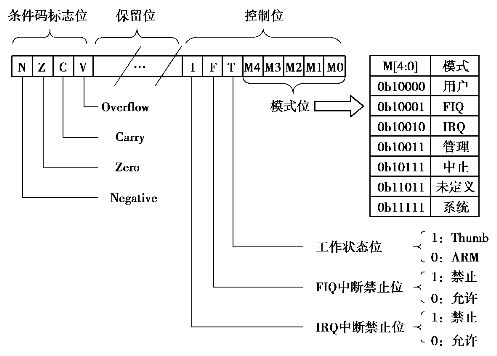

在每种异常模式下都有一个对应的物理寄存器——程序状态保存寄存器(SPSR)。 当异常出现时,SPSR 用于保存CPSR 的状态,以便异常返回后恢复异常发生时的工作状态。 程序状态寄存器的格式如图2.8 所示。

图2.8 程序状态寄存器

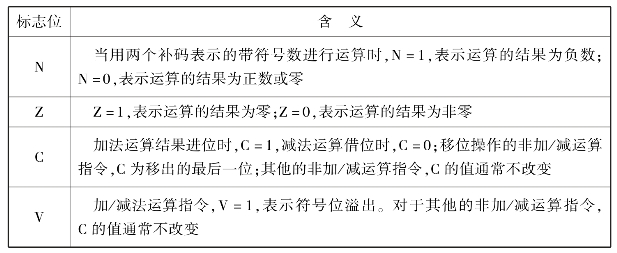

(1)程序状态寄存器的条件码标志

N、Z、C、V 均为条件码标志位。 它们的内容可被算术或逻辑运算的结果所改变,并且可以决定某条指令是否被执行。 在ARM 状态下,绝大多数的指令都是有条件执行的。 在Thumb 状态下,仅有分支指令是有条件执行的。 各条件码的含义见表2.4。

表2.4 各条件码的含义(https://www.xing528.com)

(2)程序状态寄存器的控制位

最低8 位I、F、T 和M[4:0]位用作控制位。 当异常出现时,改变控制位。 当处理器在特权模式下时,也可以由软件改变。

①禁止位:I=1,则禁止IRQ 中断;F=1,则禁止FIQ 中断。

②T 位:ARM 体系结构V5 及以上的版本的T 系列处理器,当该位为“1”时,程序运行于Thumb 状态,否则,运行于ARM 状态。 ARM 体系结构V5 及以上的版本的非T 系列处理器,当该位为“1”时,执行下一条指令以引起为定义的指令异常;当该位为“0”时,表示运行于ARM 状态。

③M 模式位:M0、M1、M2、M3 和M4 (M[4:0])是模式位,这些位决定处理器的工作模式,如图2.8 所示。 注意,M[4:0]其他组合的结果是不可预知的。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。