指令流水线是RISC 处理器执行指令时采用的机制。 采用流水线技术的主要原因是现代处理器的指令变得越来越复杂,往往需要使用多个时钟周期才能实现。 处理器的乘法和除法指令就是这方面的典型代表。 在处理器执行多周期的指令过程中,系统总线通常处于空闲状态。 如果在处理器中采用流水线技术,其总线逻辑就可以在执行指令的同时提前读入几条指令准备运行。

指令流水线是RISC 结构的一切处理器共同的一个特点,ARM 处理器也不例外,但不同的ARM 核其流水线级数不同。 例如:ARM7 采用三级流水线结构(取指、译码、执行),即运行一条指令分为三个阶段:

①取指

取指级完成程序存储器中指令的读取,并放入指令流水线中。

②译码

对指令进行译码,为下一周期准备数据路径需要的控制信号。 在这一级指令“占有”译码逻辑,而不“占有”数据路径。

③执行

指令“占有”数据路径,寄存器堆被读取,操作数在桶式移位器中被移位,ALU 产生相应的运算结果并回写到目的寄存器中,ALU 结果根据指令需求更改状态寄存器的条件位。

ARM9 采用五级流水线结构(取指、译码、执行、缓冲、写回),即运行一条指令分为五个阶段:

①取指

指令从存储器中取出,放入指令流水线。

②译码

指令译码,从寄存器堆中读取寄存器操作数。 在寄存器堆中有三个操作数读端口,因此,大多数ARM 指令能在一个周期内读取其操作数。

③执行

将一个操作数移位,产生ALU 的结果。 如果指令是“load”或“store”,在ALU 中计算存储器的地址。(https://www.xing528.com)

④缓冲数据

如果需要,则访问数据存储器,否则,ALU 的结果只是简单的缓冲一个时钟周期,以便使所有的指令具有同样流水线流程。

⑤回写

将指令产生的结果回写到寄存器堆,包括任何从存储器读取的数据。

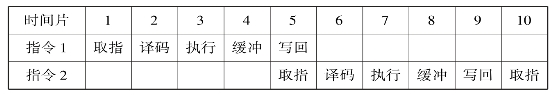

以五级流水线为例,采用指令流水线技术和不采用指令流水线技术的对比见表2.1 和表2.2,可以看出:不采用指令流水线技术,处理器10 个时间片一共完成2 条指令;而采用流水线技术,处理器10 个时间片一共完成了6 条指令。 因此,采用指令流水线技术将大大提高微处理器的运行效率。

表2.1 不采用指令流水线技术

表2.2 采用指令流水线技术

续表

例题2.1 已知某ARM 处理器采用一条五级流水线,假设每一级所需时间为4 ns,则该处理器要执行100 亿条指令最快需要多少时间?

解 因为1 ns=10 -9 s,而每一级所需时间为4 ns,并且每一级能执行一条指令,所以执行一条指令需要4 ns,即4 ×10 -9 s

因此100 亿条指令最快需要1010 ×4 ×10 -9 s=40 s

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。