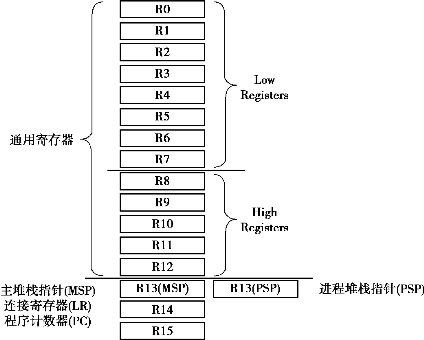

内核寄存器是CPU的组成部分,它们没有地址,可以通过寄存器名字来操作内核寄存器。Cortex-M3处理器拥有R0~R15的寄存器组,如图6.1所示。

图6.1 R0~R15寄存器组

R0~R12:通用寄存器。

R0~R12都是32位通用寄存器,用于数据操作。绝大多数16位Thumb指令只能访问R0~R7,而32位Thumb-2指令可以访问所有寄存器。

R13:两个堆栈指针。

一个R13对应两个物理寄存器,即主堆栈指针(MSP)和进程堆栈指针(PSP)。某个时刻只能访问某一个(MSP或者PSP),通过控制寄存器的CONTROL[1]位来选择使用哪一个。如果CONTROL[1]=0,则选择MSP,此时操作R13(SP)就是操作MSP;如果CONTROL[1]=1,则选择PSP,此时操作R13(SP)就是操作PSP。一般MSP用作操作系统内核栈区管理,复位后缺省使用的是主堆栈指针;PSP用作用户程序栈区管理,这样区分可以有效保护操作系统不被破坏。

堆栈指针的最低两位永远是0,这意味着堆栈总是4字节对齐的,参见第1章的堆栈指示器。

R14:连接寄存器。

当呼叫一个子程序时,由R14存储返回地址,不像大多数其他处理器,ARM为了减少访问内存的次数(访问内存的操作往往要3个以上指令周期,带MMU和Cache的就更加不确定了),把返回地址直接存储在寄存器中。这样足以使很多只有1级子程序调用的代码无需访问内存(堆栈内存),从而提高了子程序调用的效率。如果多于1级,则需要把前一级的R14值压到堆栈里。在ARM上编程时,应尽量只使用寄存器保存中间结果,迫不得已时才访问内存。

R15:程序计数寄存器。

指向当前的程序预取指令地址。如果修改它的值,就能改变程序的执行流。

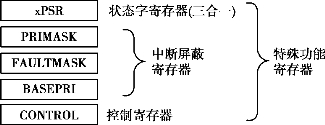

除了上面的寄存器组,Cortex-M3还在内核水平上搭载了若干特殊功能寄存器,包括程序状态字寄存器组(xPSR)、中断屏蔽寄存器组(PRIMASK、FAULTMASK、BASEPRI)和控制寄存器(CONTROL),如图6.2所示。

图6.2 Cortex-M3的特殊功能寄存器

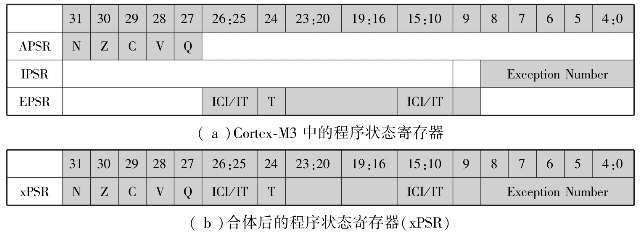

1)状态字寄存器

包括应用状态寄存器、中断状态寄存器和执行状态寄存器,如图6.3所示。

(https://www.xing528.com)

(https://www.xing528.com)

图6.3 3个状态寄存器及其合成

2)中断屏蔽寄存器

①PRIMASK:只有1位

=1:关掉所有可屏蔽中断,开放NMI和硬fault,相当于将BASEPRI设为0;

=0:允许中断。

②FAULTMASK:只有1位

=1:关掉所有中断,只开放NMI,中断退出时自动清零;

=0:允许中断。

③BASEPRI:有9位,设置中断屏蔽阈值,优先级号大于等于阈值被屏蔽。若BASEPRI设为0,则取消BASEPRI对中断的屏蔽。

这3个寄存器任何一个屏蔽了中断,则相应的中断被阻断,哪怕其他两个寄存器都是允许中断的。

3)控制寄存器CONTROL

拥有两个控制位CONTROL[1:0],分别用来设置特权级和选择堆栈指针。其中CONTROL[0]设置特权级,CONTROL[1]选择堆栈指针。

CONTROL[0]=0:特权模式;

CONTROL[0]=1:用户模式;

CONTROL[1]=0:R13选MSP;

CONTROL[1]=1:R13选PSP。

需要注意这些系统寄存器只有在特权级下才可以修改其内容,在特权模式下可以修改CONTROL[0]进入用户模式,但是要从用户模式进入特权模式就比较麻烦,因为此时不允许修改CONTROL。这么做的目的是保护操作系统不被破坏,因为操作系统程序是工作在特权级模式下,用户程序是工作在用户模式下,所以这么做是为了提高系统的安全性。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。