Cortex-M3在内核水平上搭载了一个异常响应系统,支持为数众多的系统异常和外部中断。其中,编号为1—15的对应系统异常,大于等于16的则全是外部中断。除了个别异常的优先级被定死外,其他异常的优先级都是可编程的。

因为芯片设计者可以修改Cortex-M3的硬件描述源代码,所以做成芯片后,支持的中断源数目常常不到240个,并且优先级的位数也由芯片厂商最终决定。

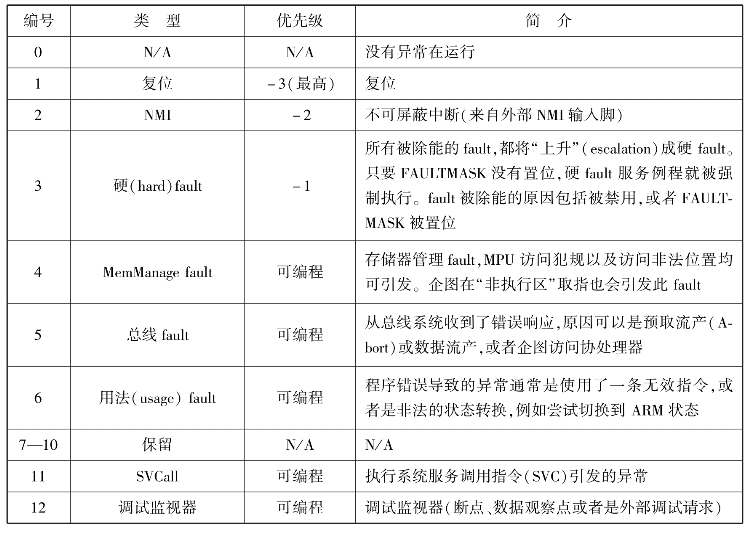

类型编号为1—15的系统异常见表3.8(注意:没有编号为0的异常)。

表3.8 类型编号为1—15的系统异常

续表

(https://www.xing528.com)

(https://www.xing528.com)

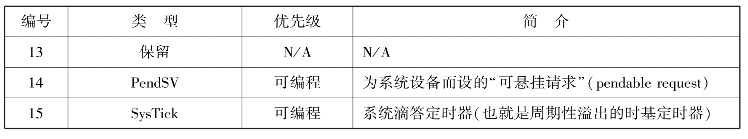

从16开始的外部中断类型见表3.9。

表3.9 从16开始的外部中断类型

在NVIC的中断控制及状态寄存器中,有一个VECTACTIVE位段;另外,还有一个特殊功能寄存器IPSR。在这二者中,都记录了当前正服务异常的编号。

需要注意的是:这里所讲的中断号,都是指NVIC所使用的中断号。另外,芯片一些管脚的名字也可能被取为类似“IRQ #”的名字,请不要混淆,它们没有必然联系。常见的情况是,编号最靠前的几个中断源被指定到片上外设,接下来的中断源才给外部中断引脚使用,因此还需要参阅芯片的数据手册来了解清楚。

如果一个发生的异常不能被即刻响应,就称它被“悬起(pending)”。不过,少数fault异常是不允许被悬起的。一个异常被悬起的原因,可能是系统当前正在执行一个更高优先级异常的服务例程,或者相关掩蔽位的设置导致该异常被除能。对于每个异常源,在被悬起的情况下,都会有一个对应的“悬起状态寄存器”保存其异常请求,直到该异常能够执行为止,这与传统的ARM是完全不同的。在以前,是由产生中断的设备保持住请求信号。现在NVIC的悬起状态寄存器的出现解决了这个问题,即使后来设备已经释放了请求信号,曾经的中断请求也不会错失。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。