Cortex-M3只有一个单一固定的存储器映射。这一点极大地方便了软件在各种Cortex-M3单片机间的移植。举个简单的例子,各款Cortex-M3单片机的NVIC和MPU都在相同的位置布设寄存器,使得它们变得通用。尽管如此,Cortex-M3定出的框架是粗线条的,它依然允许芯片制造商灵活地分配存储器空间,以制造出各具特色的单片机产品。

存储空间的一些位置用于调试组件等私有外设,这个地址段被称为“私有外设区”。私有外设区的组件包括:

①闪存地址重载及断点单元(FPB);

②数据观察点单元(DWT);

③指令跟踪宏单元(ITM);

④嵌入式跟踪宏单元(ETM);

⑤跟踪端口接口单元(TPIU);

⑥ROM表。

在后续讨论调试特性的章节中,将详细讲述这些组件。

Cortex-M3的地址空间是4 GB,程序可以在代码区、内部SRAM区以及外部RAM区中执行。但指令总线与数据总线是分开的,最理想的是把程序放到代码区,从而使取指和数据访问各自使用自己的总线,并行操作。Cortex-M3预定义的存储器映射如图3.16所示。

图3.16 Cortex-M3预定义的存储器映射

内部SRAM区的大小是512 MB,用于让芯片制造商连接片上的SRAM,这个区通过系统总线来访问。在这个区的下部,有一个1 MB的位带区,该位带区还有一个对应的32 MB的“位带别名(Alias)区”,容纳了8 M个“位变量”(对比8051的只有128位)。位带区对应的是最低的1 MB地址范围,而位带别名区里面的每个字对应位带区的一个比特。位带操作只适用于数据访问,不适用于取指。通过位带的功能,可以把多个布尔型数据打包在单一的字中,却依然可以从位带别名区中像访问普通内存一样地使用它们。位带别名区中的访问操作是原子的,消灭了传统的“读—改—写”三步曲。位带操作的细节在3.5.4中详细介绍。(https://www.xing528.com)

地址空间的另一个512 MB范围由片上外设的寄存器使用。这个区中也有一条32 MB的位带别名,以便快捷地访问外设寄存器。例如,可以方便地访问各种控制位和状态位。要注意的是,外设内不允许执行指令。

还有两个1 GB的范围,分别用于连接外部RAM和外部设备,它们之中没有位带。两者的区别在于外部RAM区允许执行指令,而外部设备区则不允许执行指令。

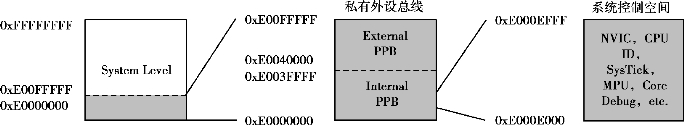

最后还剩下0.5 GB的隐秘地带,包括了Cortex-M3内核的系统级组件、内部私有外设总线、外部私有外设总线,以及由提供者定义的系统外设。

私有外设总线有两条:

①AHB私有外设总线,只用于Cortex-M3内部的AHB外设,它们是NVIC、FPB、DWT和ITM。

②APB私有外设总线,既用于Cortex-M3内部的APB设备,也用于外部设备(这里的“外部”是对内核而言的)。Cortex-M3允许器件制造商再添加一些片上APB外设到APB私有总线上,它们通过ABP接口来访问。

NVIC所处的区域称为“系统控制空间(SCS)”,在SCS里的还有SysTick、MPU以及代码调试控制所用的寄存器,如图3.17所示。

图3.17 系统控制空间

最后,未用的供应商指定区也通过系统总线来访问,但是不允许在其中执行指令。Cortex-M3中的MPU是选配的,由芯片制造商决定是否配上。

上述的存储器映射只是一个粗线条的模板,半导体厂家会提供更详尽的图示来表明芯片中片上外设的具体分布,以及RAM与ROM的容量和位置信息。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。