Cortex-M3中的特殊功能寄存器包括:

①程序状态寄存器组(PSRs或xPSR);

②中断屏蔽寄存器组(PRIMASK、FAULTMASK、BASEPRI);

③控制寄存器(CONTROL)。

特殊功能寄存器只能被专用的MSR和MRS指令访问,而且它们也没有对应的存储器地址。

MRS<gp_reg>,<special_reg>;读特殊功能寄存器的值到通用寄存器

MSR<special_reg>,<gp_reg>;写通用寄存器的值到特殊功能寄存器

1)程序状态寄存器组

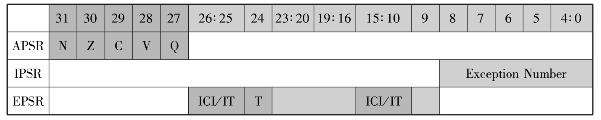

程序状态寄存器在其内部又被分为3个子状态寄存器:

①应用程序PSR(APSR);

②中断号PSR(IPSR);

③执行PSR(EPSR)。

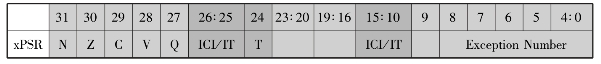

通过MRS/MSR指令,这3个PSRs既可以单独访问,也可以组合访问(2个组合、3个组合都可以)。当使用三合一的方式访问时,应使用寄存器名“xPSR”或者“PSR”。Cortex-M3中的程序状态寄存器如图3.10所示,合体后的程序状态寄存器(xPSR)如图3.11所示。

图3.10 Cortex-M3中的程序状态寄存器

图3.11 合体后的程序状态寄存器(xPSR)

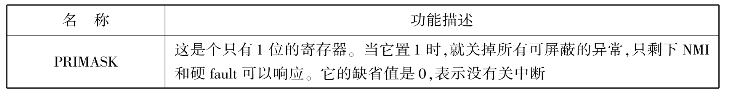

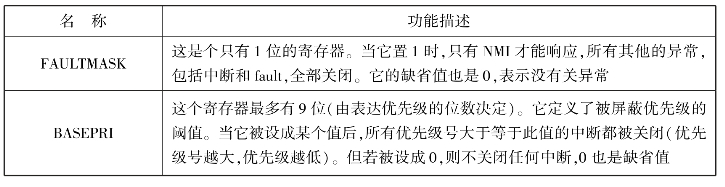

2)中断屏蔽寄存器组

中断屏蔽寄存器组包括PRIMASK、FAULTMASK和BASEPRI三个寄存器,这三个寄存器用于控制异常的使能和除能,见表3.2。

表3.2 Cortex-M3的屏蔽寄存器组

续表

(https://www.xing528.com)

(https://www.xing528.com)

对于执行时间要求很高的关键任务而言,通过PRIMASK和BASEPRI暂时关闭中断是非常重要的。而FAULTMASK则可以被操作系统用于暂时关闭错误处理机能,这种处理在某个任务崩溃时可能需要。

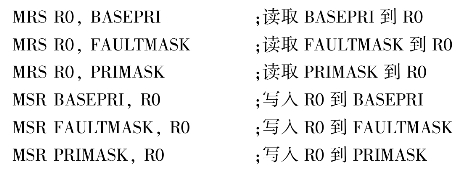

要访问PRIMASK、FAULTMASK以及BASEPRI,同样要使用MRS/MSR指令,如:

只有在特权级下,才允许访问这三个寄存器。

3)控制寄存器

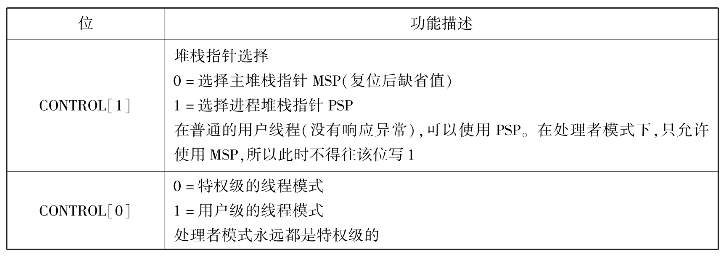

控制寄存器用于定义特权级别,还用于选择当前使用哪个堆栈指针,见表3.3。

表3.3 Cortex-M3的CONTROL寄存器

在Cortex-M3的处理者模式中,CONTROL[1]总是0。在线程模式中则可以为0或1。仅当处于特权级的线程模式下,此位才可写,其他场合下禁止写此位。CONTROL[0]也仅在特权级下操作时才允许写该位,一旦进入了用户级,唯一返回特权级的途径,就是触发一个异常(如软中断),进入处理者模式,再由服务例程改写该位。

CONTROL寄存器也是通过MRS和MSR指令来操作的:

MRS R0,CONTROL

MSR CONTROL,R0

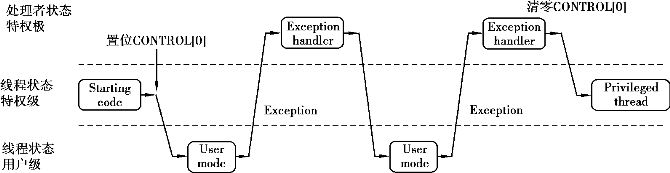

在复位后,处理器进入“线程模式+特权级”。在特权级下的代码可以通过置位CONTROL[0]来进入用户级。而不管是任何原因产生了任何异常,处理器都将以特权级来运行其服务例程,如果CONTROL[0]没被修改,异常返回后将回到产生异常之前的特权级别。用户级下的代码不能再试图修改CONTROL[0]来回到特权级。它必须通过一个异常,由那个异常来清零CONTROL[0],才能在返回到线程模式后进入特权级。用户级的代码如想进入特权级,通常使用一条“系统服务调用指令”(SVC)来触发“SVC异常”,该异常的服务例程可以选择修改CONTROL[0]。特权级和处理器模式的改变图如图3.12所示。

图3.12 特权级和处理器模式的改变图

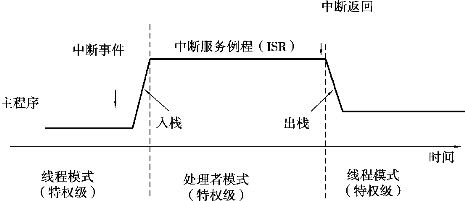

如前所述,特权等级和堆栈指针的选择均由CONTROL负责。当CONTROL[0]=0时,在异常处理的始末,只发生了处理器模式的转换,如图3.13所示。

图3.13 中断前后处理器模式的转换

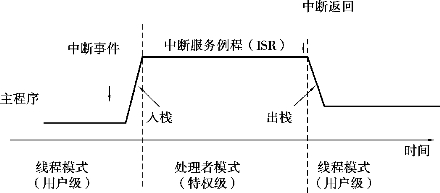

但若CONTROL[0]=1(线程模式+用户级),则在中断响应的始末,处理器模式和特权级别都要发生变化,如图3.14所示。

图3.14 中断前后处理器模式和特权级别

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。