CPU是单片机的核心部分,它由运算逻辑单元(ALU)、程序计数器(PC)、指令寄存器、指令译码器等部件组成。

1.运算逻辑单元(ALU)

运算逻辑单元(ALU)的功能是进行算术运算和逻辑运算,可对半字节(4位)、单字节等数据进行操作,如能完成加、减、自动加1、自动减1、比较等算术运算和与、或、异或、求补、循环移位等逻辑操作。操作结果的状态,如产生进位、结果为零等状态信息将影响到状态寄存器(SREG)相应的标志位。

运算逻辑单元(ALU)还包含一个布尔处理器,用来处理位操作。它可执行置位、清零、取反等操作。

ATmega16的ALU还能实现无符号数、有符号数以及浮点数的硬件乘法操作。一次硬件乘法操作的时间为2个时钟周期。

2.程序计数器(PC)、指令寄存器和指令译码器

程序计数器(PC)用来存放下一条需要执行指令在程序存储器空间的地址(指向Flash空间)。取出的指令存放在指令寄存器中,然后送入指令译码器产生各种控制信号,控制CPU的运行(执行指令)。

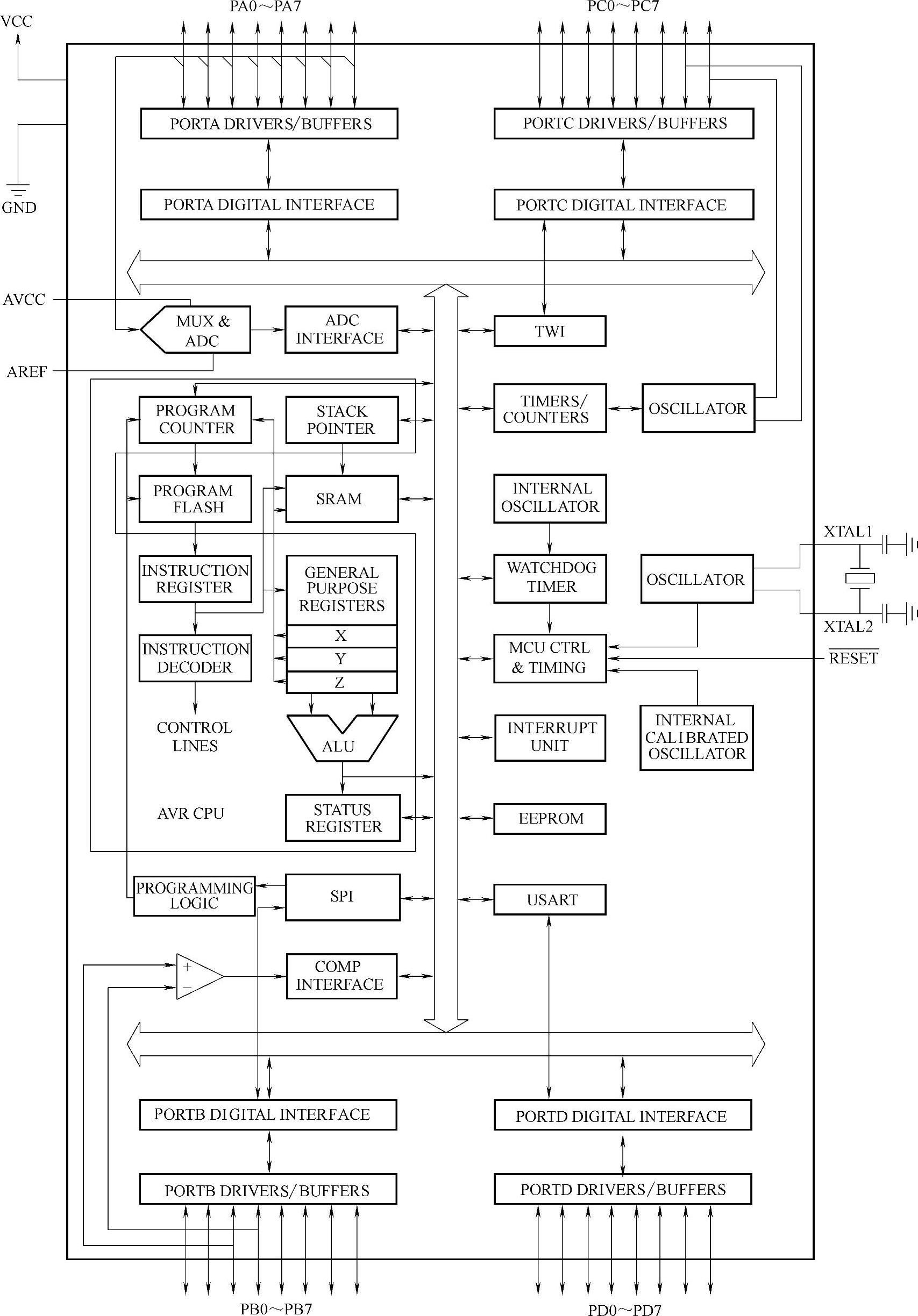

图2-4 ATmega16的结构框图

AVR单片机一条指令的长度大多数为16位,还有少部分为32位,因此AVR单片机的程序存储器结构实际上是以字(16位)为一个存储单元的。ATmega16的程序计数器为13位,正好满足了对片内8KB(即16KB)的Flash程序存储器空间直接寻址的需要,因此就不能(不支持)在外部扩展更多的程序存储器。

AVR单片机CPU在译码执行一条指令的同时,就将PC指定的Flash单元中的指令取出,放入指令寄存器中,构成了一级流水线运行方式。AVR单片机采用一级流水线技术,在当前指令执行的时候,就取出下一条将要执行的指令,加上大多数AVR指令的长度是1W,就使得AVR单片机CPU实现了一个时钟周期执行一条指令。采用这种结构,减少了取指令的次数,大大提高了CPU的运行速度,同时也提高了取指令操作的(系统的)可靠性。而在其他的CISC以及类似的RISC结构的单片机中,外部振荡器的时钟被分频降低到传统的内部指令执行周期,这种分频最大达12倍(例如,标准8031结构的单片机)。

3.通用工作寄存器组(https://www.xing528.com)

在AVR单片机中,由命名为R0~R31的32个8位通用工作寄存器构成一个“通用快速工作寄存器组”,图2-5所示为通用快速工作寄存器组的结构图。

AVR单片机CPU中的ALU与这32个通用工作寄存器组直接相连,为了使ALU能够高效和灵活地对寄存器组进行访问操作,通用寄存器组提供和支持ALU使用4种不同的数据输入/输出的操作方式:

1)提供一个8位源操作数,并保存的一个8位结果;

2)提供两个8位源操作数,并保存的一个8位结果;

3)提供两个8位源操作数,并保存的一个16位结果;

4)提供一个16位源操作数,并保存的一个16位结果。

因此,AVR单片机大多数操作工作寄存器组的指令都可以直接访问所有的寄存器,而且多数这样的指令的执行时间是一个时钟周期。例如,从寄存器组中取出两个操作数,对操作数实施处理,处理结果回写到目的寄存器中。这3个过程是在一个时钟周期内完成的,构成一个完整的ALU指令操作。

在传统的基于累加器结构的单片机中(如8051),则需要大量的程序代码来完成和实现在累加器和存储器之间的数据传送。如上面所介绍的操作过程就需要3条指令来实现:第1条完成从寄存器中取出源操作数;第2条完成对操作数实施处理;第3条将处理结果回写。这样就构成了累加器和存储器之间数据传送的瓶颈,影响了指令运行效率。

而在AVR单片机中,由于采用了32个通用工作寄存器构成快速存取寄存器组,相当于用32个通用工作寄存器代替了累加器,从而避免了在传统结构中的那种由于累加器和存储器之间频繁的数据传送交换而形成的瓶颈现象,又进一步提高了指令的运行效率和速度。

在AVR单片机中,通用寄存器组与片内的数据存储器(SRAM)处在相同的空间,32个通用寄存器被直接映射到用于数据空间的前32个地址,如图2-5所示。虽然寄存器组的物理结构与SRAM不同,但是这种内存空间的组织方式为访问工作寄存器提供了极大的灵活性,如可以利用地址指针寄存器X、Y或Z实现对通用寄存器组的间接寻址操作。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。