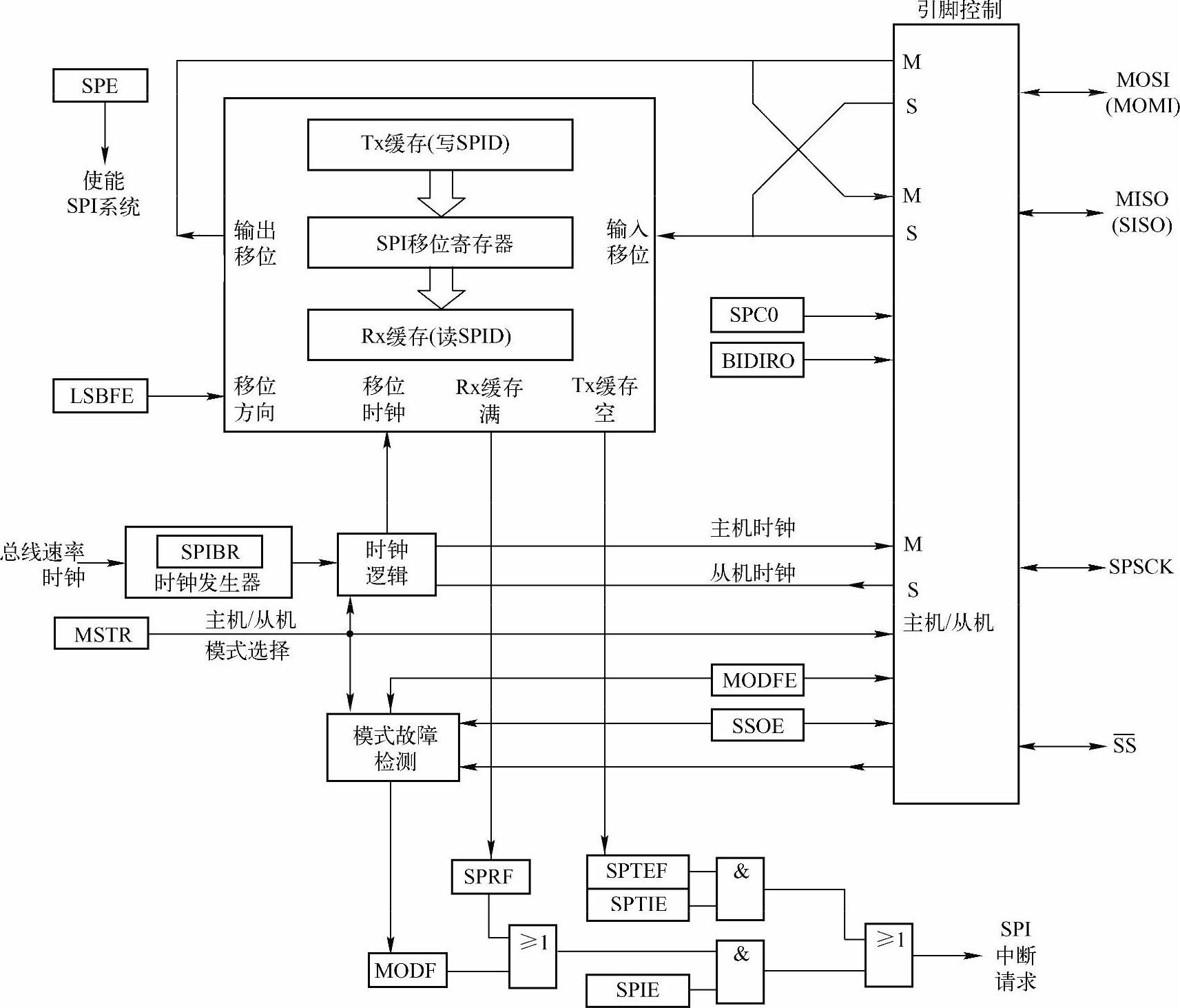

HCS08的SPI模块由8位移位寄存器、时钟控制逻辑、引脚控制逻辑、SPI控制逻辑和分频器组成,SPI模块结构框图如图11-6所示。SPI模块的核心部件是SPI移位寄存器。通过写SPID寄存器把发送数据写入到双缓冲发送器,在数据开始发送时,数据被传送到SPI移位寄存器。当移位完一个字节的数据后,数据被移位进入双缓冲的接收器,可通过读SPID来读取接收数据。在GPIO引脚和SPI模块之间有引脚复用控制逻辑。

当SPI被配置为主设备时,时钟输出被连接到SPSCK引脚,移位寄存器的输出被连接到MOSI引脚,移位寄存器的输入被连接到MISO引脚。

图11-6 SPI模块结构框图

当SPI被配置为从设备时,SPSCK引脚被连接到SPI模块的时钟输入,移位寄存器的输出被连接到MISO引脚,移位寄存器的输入被连接到MOSI引脚。(https://www.xing528.com)

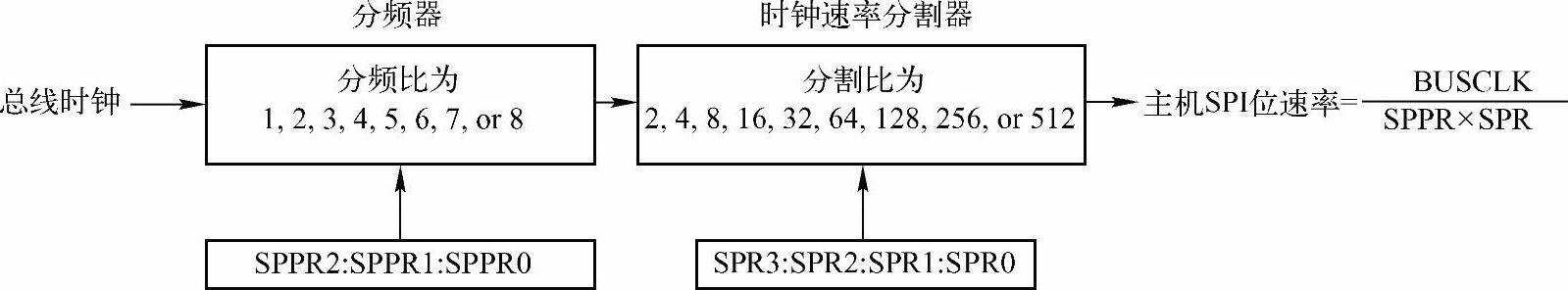

在时钟控制逻辑中,SPI波特率发生器时钟源是总线时钟。3个分频位(SPPR2:SPPR21:SPPR0)共提供8种分频约数将总线频率分频得到预分频值。3位速率分割位(SPR2:SPR21:SPR0)可组合成8种速率除数选择将预分频值再次分频进而获得SPI内部主机模式位率时钟,其逻辑结构如图11-7所示。

图11-7 SPI波特率发生器结构图

在使用多片MCU的SPI进行连接的系统中,如果一片MCU为主设备,则其余为从设备,那么只需要简单地把所有设备的SPSCK引脚连接在一起,所有MISO引脚连在一起,所有MOSI引脚连在一起就可以了。在和MCU采用SPI通信时的引脚连接要根据SPI模块实际的主从工作方式、引脚和内部移位寄存器的具体连接方式等实际情况而定。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。