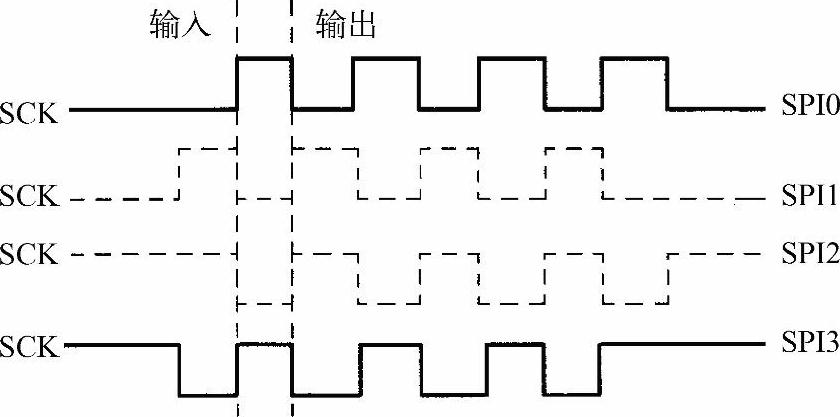

为适应来自不同厂商、不同种类的SPI外设,SPI总线模块通常都有一个可配置时钟极性(CPOL)位和时钟相位(CPHA)控制位来选择SPI0~SPI34种时钟格式中的一种,SCI总线四种工作方式如图11-3所示。在这4种工作方式中,使用最为广泛的是SPI0和SPI3方式。时钟极性(CPOL)对传输协议没有重大的影响,如果CPOL=1,SPI同步时钟在空闲状时为高电平;若CPOL=0,SPI同步时钟在空闲时保持低电平。CPHA设定时钟与数据之间两种不同的相位关系。如果CPHA=1,数据在SPI同步时钟的第二个边沿(上升或下降)被采样;若CPHA=0,数据在SPI同步时钟的第一个跳变沿(上升或下降)被采样。SPI主模块和与之通信的外设从模块之间的时钟极性和相位应该保持一致。

图11-3 SPI总线4种工作方式

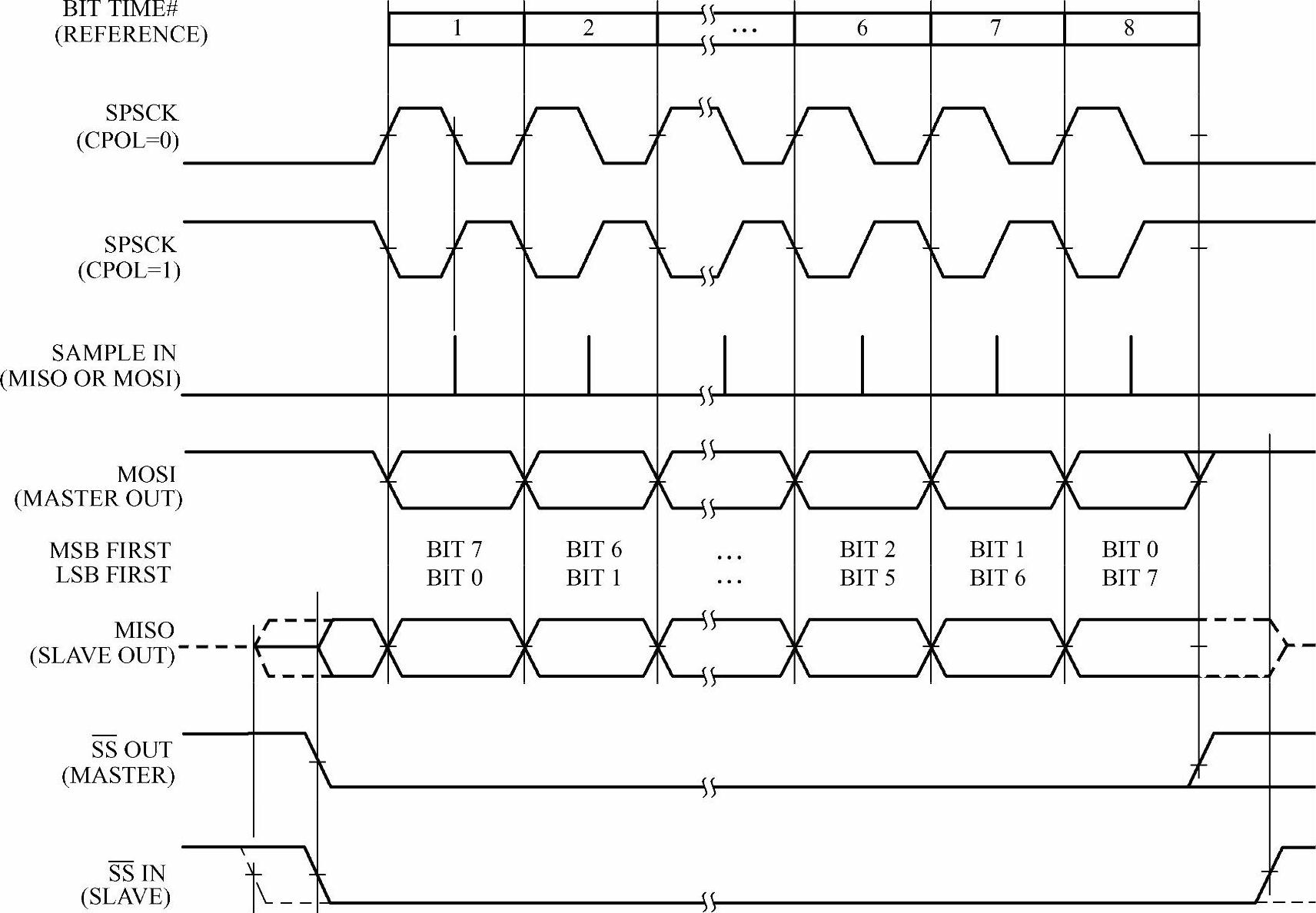

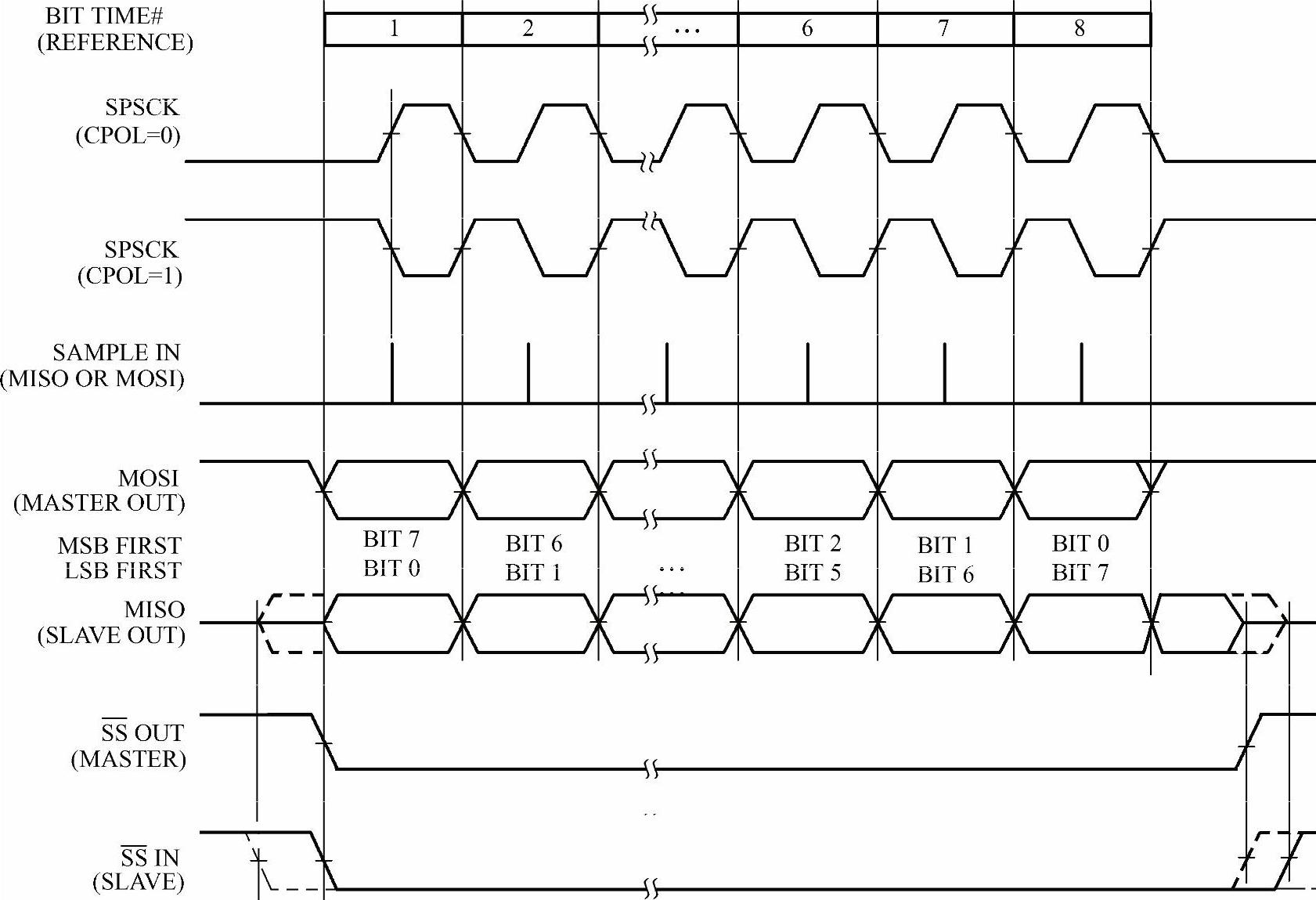

图11-4描述了CPHA=1时的SPI总线时序,图11-5显示了当CPHA=0时的SPI总线时序。SPI数据位的顺序是MSB先发还是LSB先发,取决于LSBFE位的设置情况。图中还标注了SPSCK的两种极性,但使用时只会采用其中一种,这取决于CPOL的值。两图中的“SAMPLE IN”波形针对从设备的MOSI输入或主设备的MISO输入,“MOSI”波形针对主设备的MOSI输出引脚,“MISO”波形针对从设备的MISO输出引脚,“ OUT”波形针对主设备的

OUT”波形针对主设备的 输出引脚,“

输出引脚,“ IN”波形针对从设备的

IN”波形针对从设备的 输入引脚。

输入引脚。

当CPHA=1时,传送字节8个位的参考时间为:第1位以第1个SPSCK边沿开始,第8位在第16个SPSCK边沿之后的半个SPSCK周期处结束。主设备的 输出在数据传送开始前的半个SPSCK周期变为有效低电平,并在第8位传送结束时返回高电平。一旦

输出在数据传送开始前的半个SPSCK周期变为有效低电平,并在第8位传送结束时返回高电平。一旦 变为有效低电平,从设备便开始驱动它的MISO输出,但是直到第一个SPSCK边沿时数据才被定义。第一个SPSCK边沿将主设备发送数据的第一位从移位器送至主设备的MOSI输出引脚,同时也把从设备发送数据的第一位从移位器送至从设备的MISO输出引脚。下一个SPSCK边沿将使主设备在自己的MISO输入、从设备在自己的MOSI输入各自对数据位值进行采样。在第三个SPSCK边沿,从设备内的SPI移位器将刚才的采样值移入到移位器一端,同时把移位器另一端的一个数据位各自移至MOSI、MISO输出引脚。当CHPA=1时,在两次字节传送之间,并不要求从设备的

变为有效低电平,从设备便开始驱动它的MISO输出,但是直到第一个SPSCK边沿时数据才被定义。第一个SPSCK边沿将主设备发送数据的第一位从移位器送至主设备的MOSI输出引脚,同时也把从设备发送数据的第一位从移位器送至从设备的MISO输出引脚。下一个SPSCK边沿将使主设备在自己的MISO输入、从设备在自己的MOSI输入各自对数据位值进行采样。在第三个SPSCK边沿,从设备内的SPI移位器将刚才的采样值移入到移位器一端,同时把移位器另一端的一个数据位各自移至MOSI、MISO输出引脚。当CHPA=1时,在两次字节传送之间,并不要求从设备的 输入被拉到高电平。

输入被拉到高电平。

(https://www.xing528.com)

(https://www.xing528.com)

图11-4 SPI总线时序(CPHA=1)

当CPHA=0时,传送字节8个位的参考时间为:第1位在从设备被选定(“SS IN”变低)时开始,第8位在第16个SPSCK边沿处结束。主设备的 输出在第一位数据开始传送时变为有效低电平,并在第8位传送结束之后的半个SPSCK周期返回高电平。一旦

输出在第一位数据开始传送时变为有效低电平,并在第8位传送结束之后的半个SPSCK周期返回高电平。一旦 变为有效低电平,从设备便开始把发送数据的第1位驱动到的MISO输出。第一个SPSCK边沿将使主设备在自己的MISO输入、从设备在自己的MOSI输入各自对数据位值进行采样。在第二个SPSCK边沿,主从设备内的SPI移位器将刚才的采样值移入到移位器一端,同时把移位器另一端的一个数据位各自移至MOSI、MISO输出引脚。当CHPA=0时,在两次字节传送之间,从设备的

变为有效低电平,从设备便开始把发送数据的第1位驱动到的MISO输出。第一个SPSCK边沿将使主设备在自己的MISO输入、从设备在自己的MOSI输入各自对数据位值进行采样。在第二个SPSCK边沿,主从设备内的SPI移位器将刚才的采样值移入到移位器一端,同时把移位器另一端的一个数据位各自移至MOSI、MISO输出引脚。当CHPA=0时,在两次字节传送之间,从设备的 输入必须被拉到高电平。

输入必须被拉到高电平。

图11-5 SPI总线时序(CPHA=0)

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。