A-D转换器种类很多,不同量化和编码过程对应不同原理的A-D转换器,例如,计数比较型、逐次逼近型、双积分型等,每一种类型还可细分多个子类型。在此我们介绍最常用的两种A-D转换器,逐次逼近型和双积分型的工作原理。

1.逐次逼近型A-D转换器

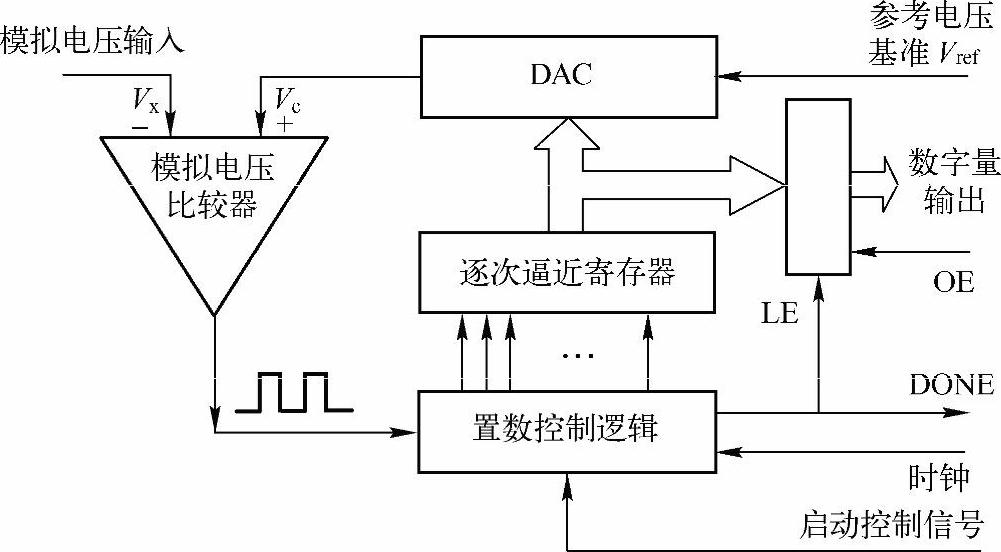

逐次逼近型A-D转换器(简称为SAR)是一种直接转换的ADC,这种转换器是以DAC为基础,再加上模拟电压比较器、逐次逼近寄存器、置数控制逻辑以及输出锁存器等组成,逐次逼近型ADC结构图如图9-2所示。

图9-2 逐次逼近型ADC结构图

逐次逼近型A-D转换器在转换过程中的逐次逼近是按照对分比较或者对分搜索的原理进行的,其具体转换的工作原理如下。

在启动信号控制下,首先置数控制逻辑给逐次逼近型寄存器最高位Dn−1置1,其余各位清0,此时寄存器内容经DAC转换成模拟量VC,该值目前约为满量程的1/2,将VC与输入模拟量Vx输入模拟电压比较器进行比较,如果Vx≥VC,则电压比较器输出0,说明逐次逼近型寄存器中的数字量偏小,应该保留Dn−1=1;相反的,如果Vx<VC,则电压比较器输出1,说明逐次逼近型寄存器中的数字量偏大,应该修改Dn−1=0;然后,再由置数控制逻辑给逐次逼近型寄存器的下一位Dn−2置1,进行同样的转换和比较,并且根据比较结果决定这一位的“1”是否保留。这样重复执行上述过程,当进行n次直到最低位D0确定是“1”或者“0”后转换完成,最终逐次逼近型寄存器中的数值即为A-D转换的结果。此时转换完成(DONE)信号和锁存允许(LE)信号同时输出有效电平,将转换结果锁存到输出锁存器中,当输出使能信号(OE)有效时,数字量即从输出锁存器中输出供后续处理。

逐次逼近型A-D转换器易于获得较高的转换速度和分辨率,可支持多通道模拟输入,且与MCU的接口简单,价格适中得到极为广范的应用。常见的逐次逼近型A-D转换器有ADC0809、ADC0801等,同时目前有些单片机内部也集成了10位或12位的逐次逼近型A-D转换模块。

2.双积分型A-D转换器(https://www.xing528.com)

双积分型A-D转换器属于间接型的ADC,这种转换器先对输入模拟采样信号与基准信号进行两次积分,以获得与采样平均值成正比的时间间隔,同时在这个时间间隔内用计数器对标准时钟脉冲(CP)计数,计数器输出的计数结果就是对应数字量。

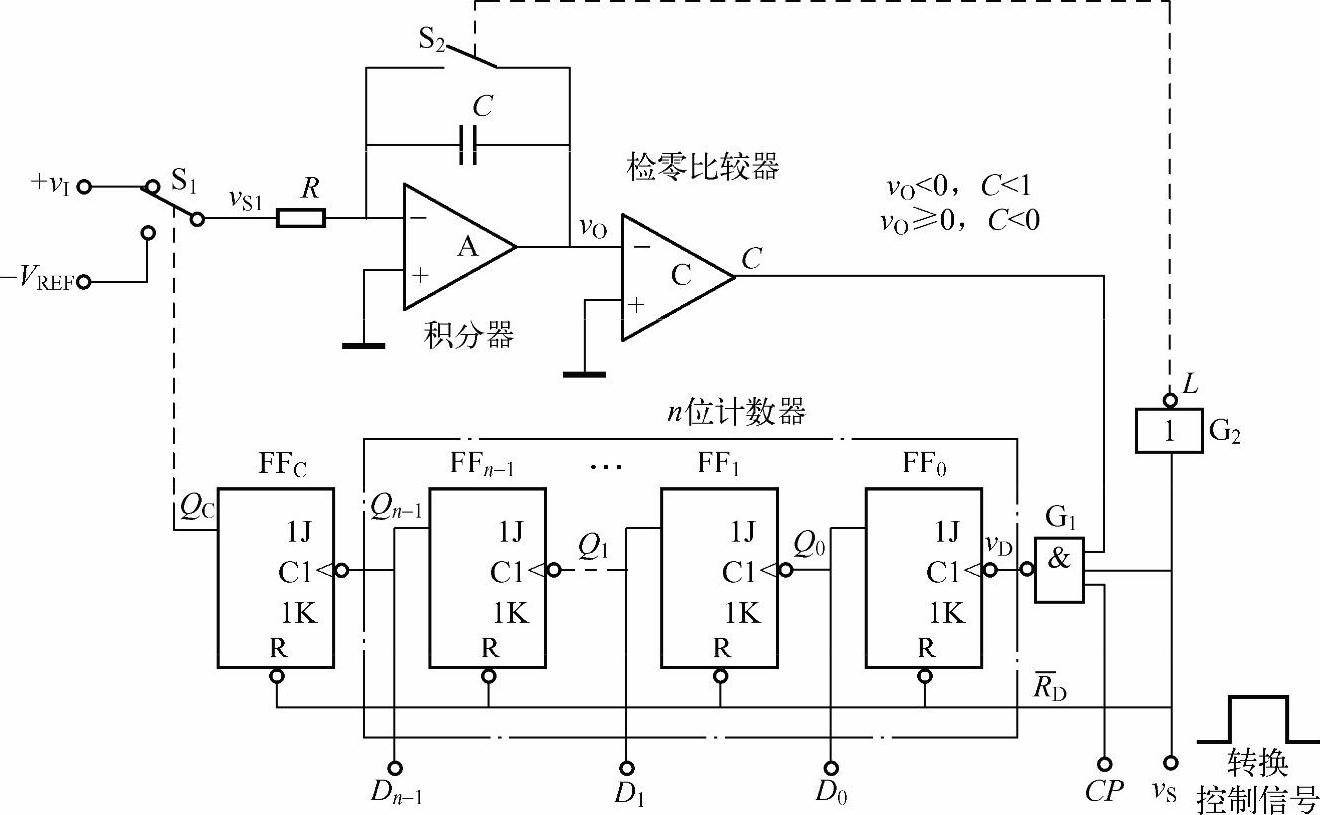

图9-3所示为双积分型ADC简化电路结构图,它包括:积分器、检零比较器、n位计数器和辅助触发器以及开关S1和S2组成。积分器由R、C和运算放大器A组成,它是电路的核心。检零比较器的“-”端接积分器的VO,“+”端接地,n位计数器和辅助触发器由n-1个JK触发器接成n位二进制异步加计数器,开关S1由FFC的输出驱动,S2由G2的输出驱动。

图9-3 双积分型ADC简化电路结构图

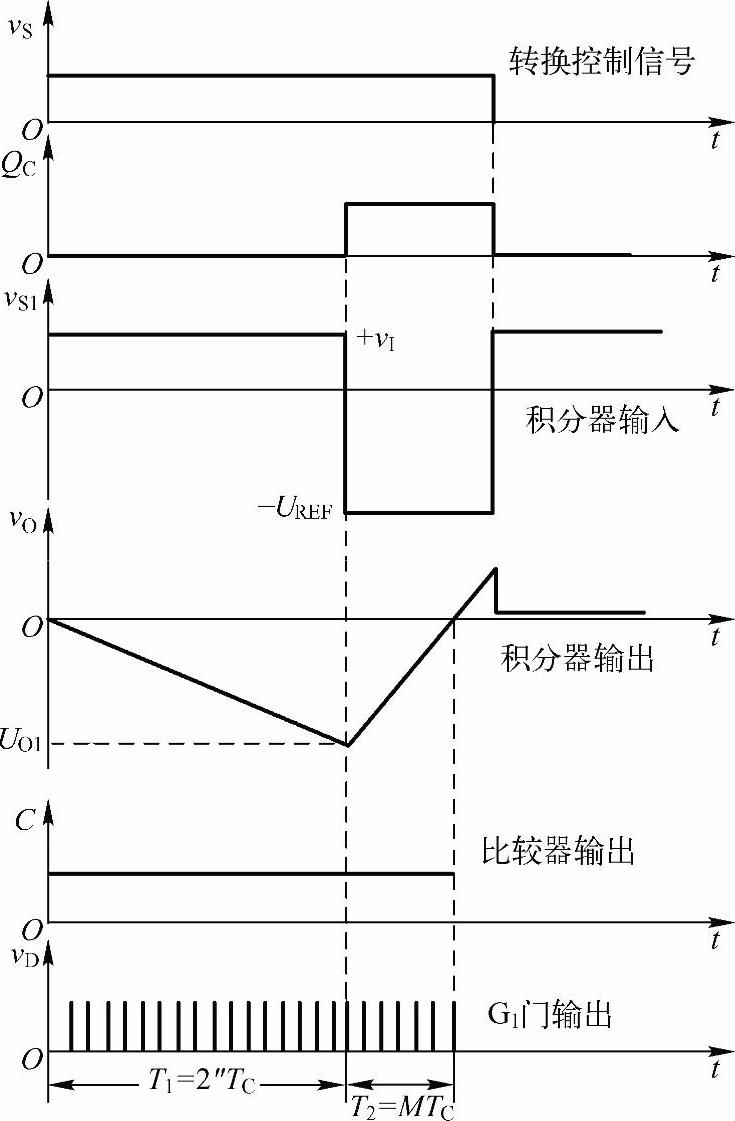

双积分型ADC的工作分为3个阶段,第一阶段为初始准备阶段,此时将计数器和FFC清零,并通过G2将开关S2闭合,电容C得到充分放电,S1掷向VI,第二阶段为取样阶段(一次积分阶段),双积分型ADC工作波形图如图9-4所示,该阶段中积分器输出的电压VO1与输入模拟电压的取样平均值VI成正比。第三阶段是比较阶段(二次积分阶段),将VO1转换成与之成正比的时间间隔T2,并用计数器以时钟周期TC进行度量。

双积分A-D转换器的突出优点是转换精度高、工作性能比较稳定且抗干扰能力强,其输出只对输入信号平均值有响应,且只要两次积分过程中积分器的时间常数相等则计数器的计数结果就与RC无关,因此该电路对RC精度要求不高,结构也比较简单,因而在数字电压表、工业现场的实时信号采集等领域得到非常广泛的应用。

图9-4 双积分型ADC工作波形图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。