CPU读/写存储器需要通过存储器的地址来进行读/写,CPU和片内外围模块通信需要通过外围模块的地址(寄存器地址)来进行访问。CPU和存储器、外围模块通信本质上都是CPU和不同地址通信,不同地址可以代表不同对象。RAM存储器具有地址,Flash存储器也具有地址,不同存储器和CPU连接就有两种编址方式:独立编址和统一编址。同样,存储器具有地址,各个外围模块(称为模块寄存器)也有地址,存储器、寄存器和CPU连接也有两种编址方式:独立编址和统一编址。

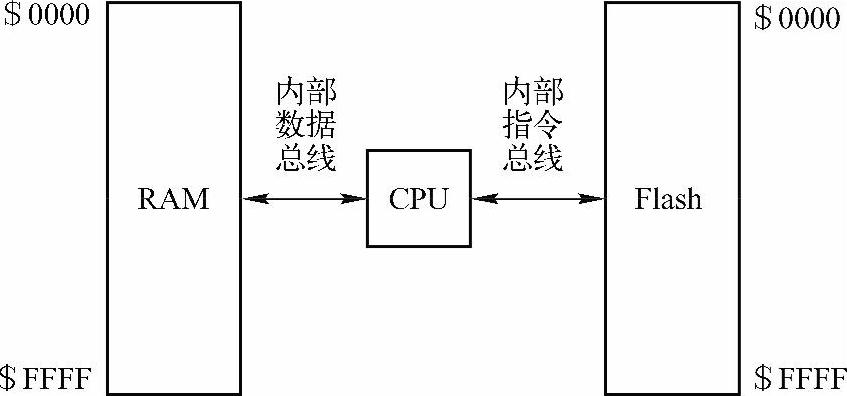

存储器独立编址方式如图2-4所示,RAM和Flash的地址各自独立编址,这种编址方式也称为哈佛结构,独立编址的好处是可以生成双倍的存储器空间,独立编址的存储器地址出现重叠,但通过不同的控制线并配合不同的指令就可以区分不同存储器。

图2-4 存储器独立编址方式

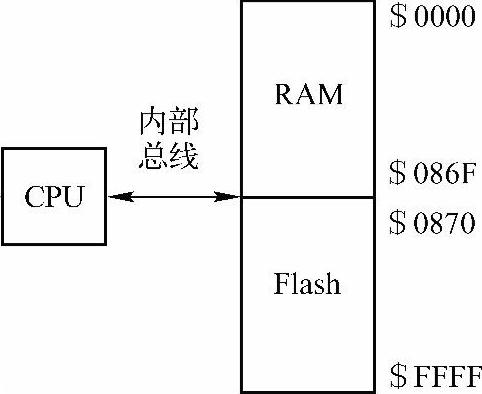

存储器统一编址方式如图2-5所示,RAM和Flash的统一编址在一个地址范围内,分段使用,这种编址方式也称为普林斯顿结构,如飞思卡尔的S08、S12等系列,MCU就采用这种结构。统一编址所获得的存储器空间比分离编址减半,但通过同一指令再配合不同地址参数就可以区分不同存储器。(https://www.xing528.com)

图2-5 存储器统一编址方式

在单片机系统中,CPU将片内外围模块如I/O、A-D、Timer、SCI、SPI和IIC等都视为内部寄存器处理,这些模块的寄存器统称为模块控制和状态寄存器。与存储器结构相类似,控制和状态寄存器的编址也有相应的两种方案。独立编址方案为寄存器再独立开辟一个空间,用专门的I/O访问控制线与指令实现对其访问。飞思卡尔的S08、S12系列MCU则将模块控制和状态寄存器与存储器统一编址在一个空间,仅仅分配不同的单元地址而已,因而属于普林斯顿型的统一编址方案。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。