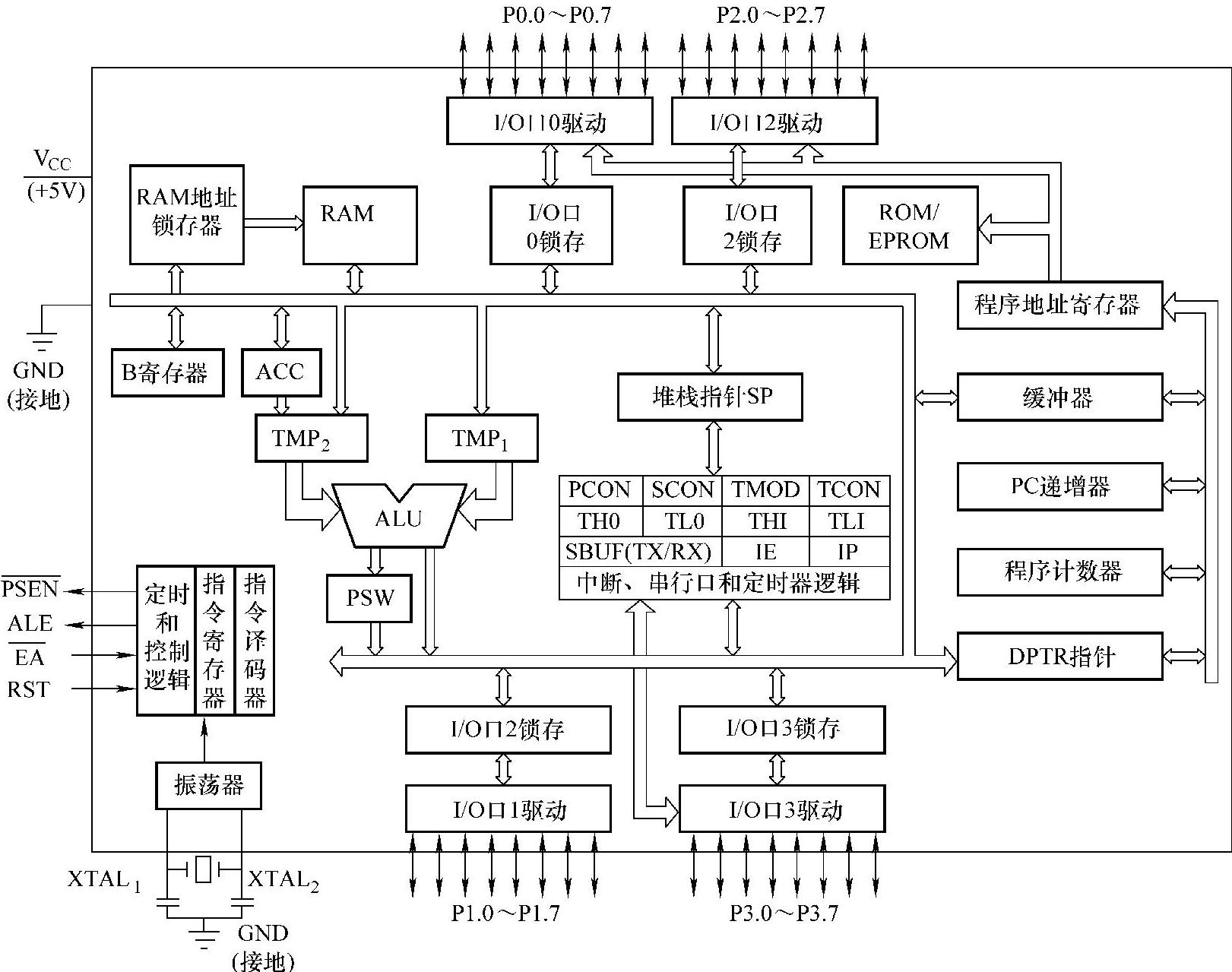

MCS51单片机内部基本模块包括中央处理器(CPU)、存储器(数据存储器RAM和程序存储器ROM)、并行I/O口、串行通信口、定时器/计数器、中断系统等功能器件,内部模块之间通信由总线连接。如图3-1所示。其中,中央处理器包含运算器和控制器两部分电路,而运算器包含算术逻辑单元(ALU),累加器(ACC)、B寄存器、暂存器,程序状态字(PSW),布尔处理器;控制器由指令寄存器、指令译码器、复位电路、时钟发生器、定时控制逻辑、程序计数器、程序地址寄存器、数据指针、堆栈指针等组成。

图3-1 单片机内部结构图

下面分别介绍各块的功能。

(1)算术逻辑单元(ALU)

功能十分强大,它不仅对8位变量进行逻辑“与”、“或”、“异或”、“循环”、“求补”、“清零”等基本操作,而且还可以进行加、减、乘、除等基本运算。

(2)累加器(ACC)

为8位寄存器,是程序中最常用的专用寄存器,在指令系统中累加器的助记符为A。作用:作为暂存寄存器,用于提供操作数和存放运算结果。直接与内部总线相连,一般信息传递和交换都要经过ACC。

(3)B寄存器

为8位寄存器,主要用于乘除指令中。乘法指令的两个操作数分别取自累加器A和寄存器B,其中B为乘数,乘法结果的高8位存放于寄存器B中。除法指令中,被除数取自A,除数取自B,除法的结果商数存放于A中,余数存放于B中。在其他指令中,B寄存器也可作为一般的数据单元来使用。

(4)程序状态字(PSW)

是一个8位寄存器,用于设定CPU的状态和指示指令执行后的状态。包括了CY、AC、F0、F1、AS1、AS0、OV、P等几个状态位。

●CY(PSW.7) 进位标志。在执行加减运算指令时,如果运算结果最高位(D7)发生了进位或借位,则CY由硬件自动置1。

●AC(PSW.6) 半进位标志位,也称为辅助标志位。在执行加减运算指令时,如果运算结果的低半字节(D3)发生了向高半字节进位或借位,则AC由硬件自动置1。

●F0、F1(PSW.5和PSW.1) 用户标志位。用户可以根据需要对F0、F1赋予一定的含义,由用户置1和清0,作为软件标志。

●RS1、RS0(PSW.4和PSW.3) 工作寄存器组选择控制位。通过对这两位设定,可以从4个工作寄存器组中选择一组作为当前工作寄存器。

●OV(PSW.2) 溢出标志位。有两种情况影响该位,一是执行加减运算时,如果D7或D6任一位,并且只一位发生了进位或借位,则OV自动置1。

●P(PSW.0) 奇偶标志位。每条指令执行完后,该位都会指示当前累加器A中1的个数。如果A中有奇数个1,则P自动置1。

(5)布尔处理器

即位处理器,它包含有位累加器CY、位寻址寄存器、位寻址I/O口、位寻址内部RAM、程序存储器等,组成一个完整的、独立的、功能很强的位处理器。

计算机内部使用二进制代码表示十进制数,称为BCD码。BCD码可以用若干二进制代码来表示一位十进制数,即二进制编码的十进制数(BinaryCodedDecimal)。布尔处理器则可以进行快速的二进制控制以及提供最快速的切换处理,并且在编程时利用指令控制状态和标志实现复杂逻辑的简单实现。

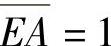

1)存储器 存储器是单片机重要组成部分,分为数据存储器和程序存储器。图3-2给出单片机存储器映像图和地址分配。

①程序存储器。51单片机芯片内部提供4K字节的程序存储器,片外可用16位地址线扩展到64KB的ROM空间。CPU可以通过单片机31引脚 选择由内部的程序区启动或者由外部的程序区启动,

选择由内部的程序区启动或者由外部的程序区启动, 外部扩展ROM到64K的空间,地址从0000H开始编码;

外部扩展ROM到64K的空间,地址从0000H开始编码; ,执行芯片内部程序,一旦程序存储器空间超过4K字节时,CPU自动选择外部ROM执行程序。

,执行芯片内部程序,一旦程序存储器空间超过4K字节时,CPU自动选择外部ROM执行程序。

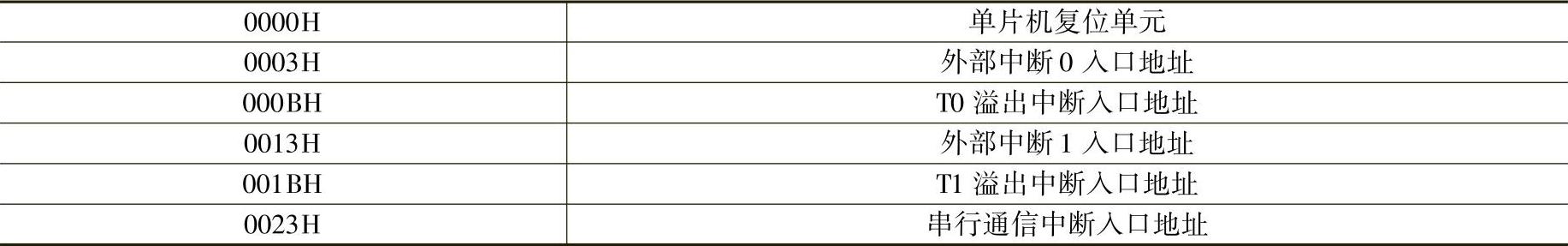

程序存储器有部分重叠,在某些单元被保留做特定程序入口地址见表3-1。

图3-2 储存器映像图

表3-1 单片机特定程序入口地址表

②数据存储器。数据存储器是由随机储存器RAM(读写存储器)构成,用于随时刷新数据并利于存放运算的中间结果,数据暂存和缓冲数据,标志位等。内部RAM共有256个单元,通常把256个单元按其功能划分为两部分:低128单元(单元地址00H~7FH)和高128单元(单元地址80H~FFH)(在逻辑上来讲高128B和特殊寄存器在地址上是重叠的)。在单片机中数据存储器中可以分为寄存器区、位寻址区、用户RAM区、特殊寄存器区(内部数据存储器高128单元)

2)寄存器区 在51单片机中共有4组寄存器,其中每组都有8个8位寄存单元,各组都以R0~R7作寄存单元编号。寄存器常用于存放操作数中间结果等。由于它们的功能及使用不作预先规定,因此称为通用寄存器,有时也叫工作寄存器。4组通用寄存器占据内部RAM的00H~1FH单元地址。

3)位寻址区 内部RAM的20H~2FH单元,既可作为一般单元使用,进行字节操作,也可以对单元中每一位进行位操作,因此把该区称为位寻址区。位寻址区共有16个RAM单元,计128位,地址为00H~7FH。

4)用户RAM区 对51单片机低128字节地址空间,00H~7FH为片内RAM作为处理问题的数据缓冲器;51单片机有32个工作寄存器,00H~1FH为4组工作寄存器区,每组有8个工作寄存器。CPU在复位后默认选择第0组工作寄存器。(https://www.xing528.com)

5)特殊寄存器区 内部RAM的高128字节是供给特殊寄存器使用的,其单元地址为80H~FFH。因这些寄存器的功能已作专门规定,故称为专用寄存器(SpecialFunctionRegister),也可称为特殊功能寄存器。

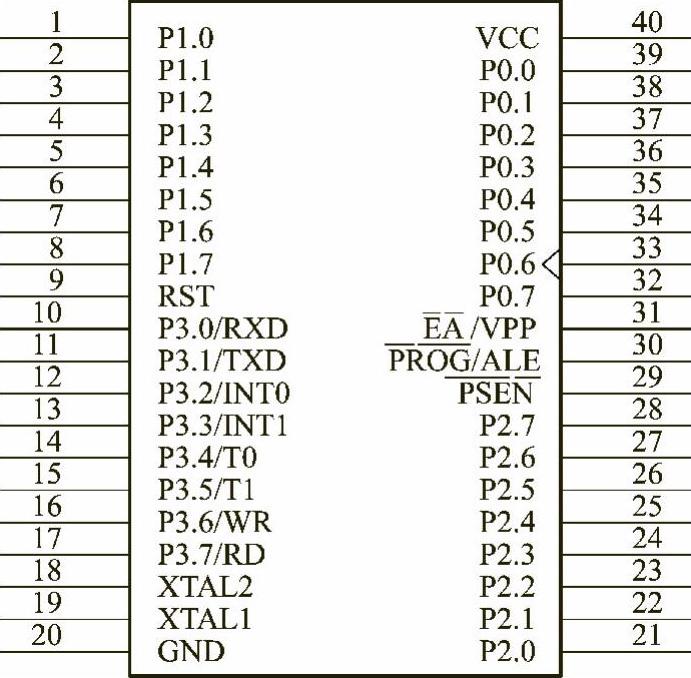

(6)单片机引脚功能 51系列单片机由4个8位I/O并行口,4个控制引脚,两个时钟引脚和两个电源引脚组成的40个双列直插集成芯片,51单片机芯片引脚如图3-3所示。

1)4个8位并行I/O口。

P0.0~P0.7(32~39引脚):在访问外部存储器时,提供低8位地址线和8位双向数据总线,也可以作为普通输出/入端口使用。

P1.0~P1.7(1~8引脚):普通带内部上拉电阻的双向输出/入端口。

P2.0~P2.7(21~28引脚):普通带内部上拉电阻的双向输出/入端口。

P3.0~P3.7(10~17引脚):普通带内部上拉电阻的双向输出/入端口;同时也具有专门的P3口第二功能。P3口第二功能如下:

●P3.0:RXD串行接收端。

●P3.1:TXD串行发送端。

●P3.2:INT0外部中断0输入。

●P3.3:INT1外部中断1输入。

●P3.4:T0外部定时器/计数器0输入。

●P3.5:T1外部定时器/计数器1输入。

●P3.6:WR片外数据存储器写选通控制。

●P3.7:RD片外数据存储器读选通控制。

图3-3 51单片机引脚图

2)电源引脚

●40引脚VCC:供电电压5V。

●20引脚GND:接地。

3)时钟引脚

●时钟引脚XTAL1和XTAL2,电路设计时多采用内部振荡方式产生时钟脉冲。

●19引脚XTAL1:接内部时钟工作电路的输入。

●18引脚XTAL2:接内部时钟工作电路的输出。

4)控制引脚。51单片机的控制线共有4根,分别为RST、 、

、 和E

和E 。其中3根是复用线,分别为

。其中3根是复用线,分别为 、

、 G和

G和 ,具有两种功能。

,具有两种功能。

●复位引脚RST(9引脚)为单片机上电复位输入端,只要在该引脚上连续保持两个机器周期以上的高电平,单片机就可以实现复位操作。

● (29引脚)为外部程序存储器ROM读选通信号。该引脚有效(低电平)时,当单片机读取外部程序存储器ROM的指令和数据时,每个机器周期内

(29引脚)为外部程序存储器ROM读选通信号。该引脚有效(低电平)时,当单片机读取外部程序存储器ROM的指令和数据时,每个机器周期内 两次有效,

两次有效, 相当于外部

相当于外部 芯片输出允许的选通信号。但读片内

芯片输出允许的选通信号。但读片内 和读片外

和读片外 时,不会产生有效的

时,不会产生有效的 信号。

信号。

● (30引脚)为地址锁存允许/编程脉冲。访问外部存储器时,ALE用来锁存P0口送出的低8位地址信号。当ALE信号有效(高电平)时,P0口传送的是低8位地址信号;当ALE无效(低电平)时,P0口传送的是8位数据信号。

(30引脚)为地址锁存允许/编程脉冲。访问外部存储器时,ALE用来锁存P0口送出的低8位地址信号。当ALE信号有效(高电平)时,P0口传送的是低8位地址信号;当ALE无效(低电平)时,P0口传送的是8位数据信号。

当不执行访问外部RAM指令时,ALE以时钟振荡频率1/6的固定频率输出,ALE信号可以作为外部芯片的时钟信号。但当CPU执行访问外部RAM时,ALE将丢失一个ALE脉冲。

:单片机对内部ROM编程时的编程脉冲输入端。

:单片机对内部ROM编程时的编程脉冲输入端。

●EA/VPP(31引脚)为访问程序存储器控制信号。51单片机的寻址范围为64KB,其中4KB在片内,60KB在片外,当 为高电平时,先访问片内ROM,当程序长度超过4KB时将自动转向执行外部ROM中的程序。当

为高电平时,先访问片内ROM,当程序长度超过4KB时将自动转向执行外部ROM中的程序。当 为低电平时,单片机只访问外部ROM。

为低电平时,单片机只访问外部ROM。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。