1.功能描述

KC-201为FM立体声收音模块,配合单片机最小系统电路或本公司单片机实验板能够完成88~108MHz频率的调频广播接收。模块采用TEA5767/CL5767专用FM芯片,接收稳定可靠。板载TDA2822功放电路,同时有左右声道音量调节电位器。KC-201立体声收音模块如图11-43所示。

图11-43 KC-201 FM立体声收音模块

2.模块主要参数和特点

1)采用通用的102BC模块的封装。

2)兼容TEA5767及CL3767软、硬件(软件搜索使用IF中频功率判断方式,如原机型使用立体声判断方式的只需少做软件改动即可)。

3)灵敏度高、噪声小、抗干扰能力强、外接元器件极少、使用极其简单,板子尺寸为47mm×48mm。

4)I2C串行数据总线接口通信。

5)采用先进的SEEK硬件搜台方式,全频段搜索只需4~5s,在幅提高搜台速度。

6)内置LDO调整、低功耗、超宽电压使用范围(DC2.7~5.5V)。

7)内置噪声消除、软静音、低音增强电路设计。

8)FM及MPX立体声采用DSP处理器。

9)应用简便、成本低,性价比高。

3.硬件接口描述

J1:是与单片机连接的IIC总线接口,分别为SDA(数据)、CLK(时钟)、GND(地)、VCC(电源)。

J3:是音频输出口:R+(右声道输出线+)、R-(右声道输出线-)、L+(左声道输出线+)、L-(左声道输出线-)。

J2:为外置耳机插孔,插上耳机后,左右声道音频输出自动切换到耳机上,拔掉耳机后,左右声道输出自动切换到J3输出端。

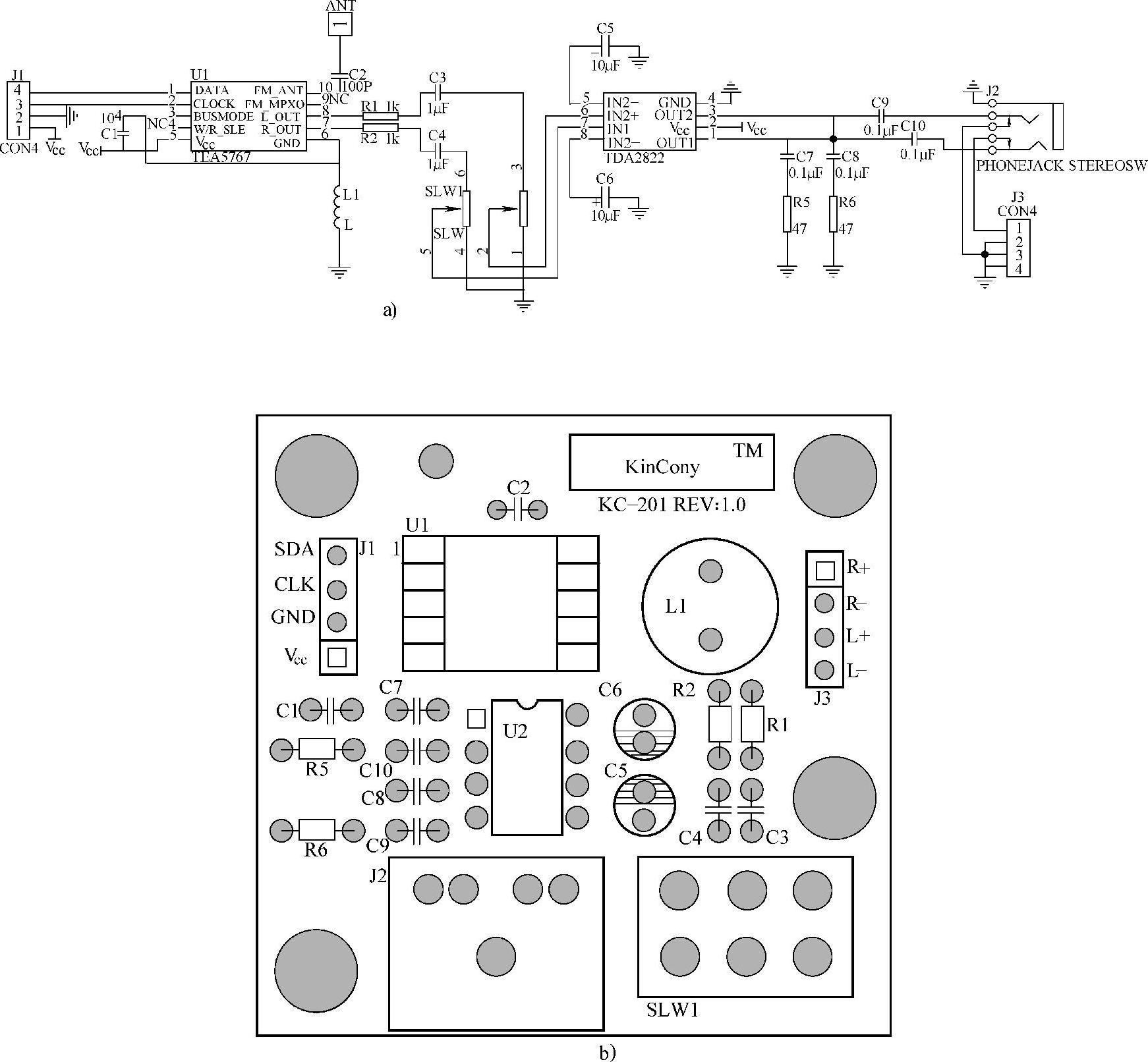

4.电路原理与元器件分布

电路原理和元器件分布如图11-44所示。

5.模块相关背景知识

CL3767是一片低功耗电调谐调频立体声收音机电路,其内部集成了中频选频和解调网络,可以做到完全免调,因此只需要很少量的小体积外围元件。CL3767HN可以应用在欧洲、美国和日本不同的FM波段环境。该产品具有如下特点:

1)高灵敏度(使用低噪声射频输入放大器);

2)兼容美国/欧洲(87.5~108 MHz)和日本(76~91MHz)调频波段;

3)预调谐接收日本电视伴音至108 MHz;

4)高放自动增益控制(AGC)电路;

5)LC调谐振荡用低成本固定芯片;

6)调频中频选择在内部完成,中频免调;

7)三种振荡基准频率输入32.768kHz、13MHz、6.5MHz;

8)锁相环调谐系统;

9)由总线模式引脚来选择I2C总线模式或三线模式;

10)由总线输出7位中频计数,由总线输出4位电平;

11)软静音,立体声消噪(SNC),高电平切割(HCC);

12)软静音,立体声消噪(SNC),高电平切割(HCC)能通过总线关断;

13)免调谐立体声解码器,自动搜索调谐功能;

14)待机模式;

15)两个软件可编程端口,总线输入,输出线三态模式;

16)自动调节温度范围(在VCCA,VCC(VCO)和VCCD=5V)。

图11-44 电路原理和元器件分布

a)电路原理 b)元器件分布

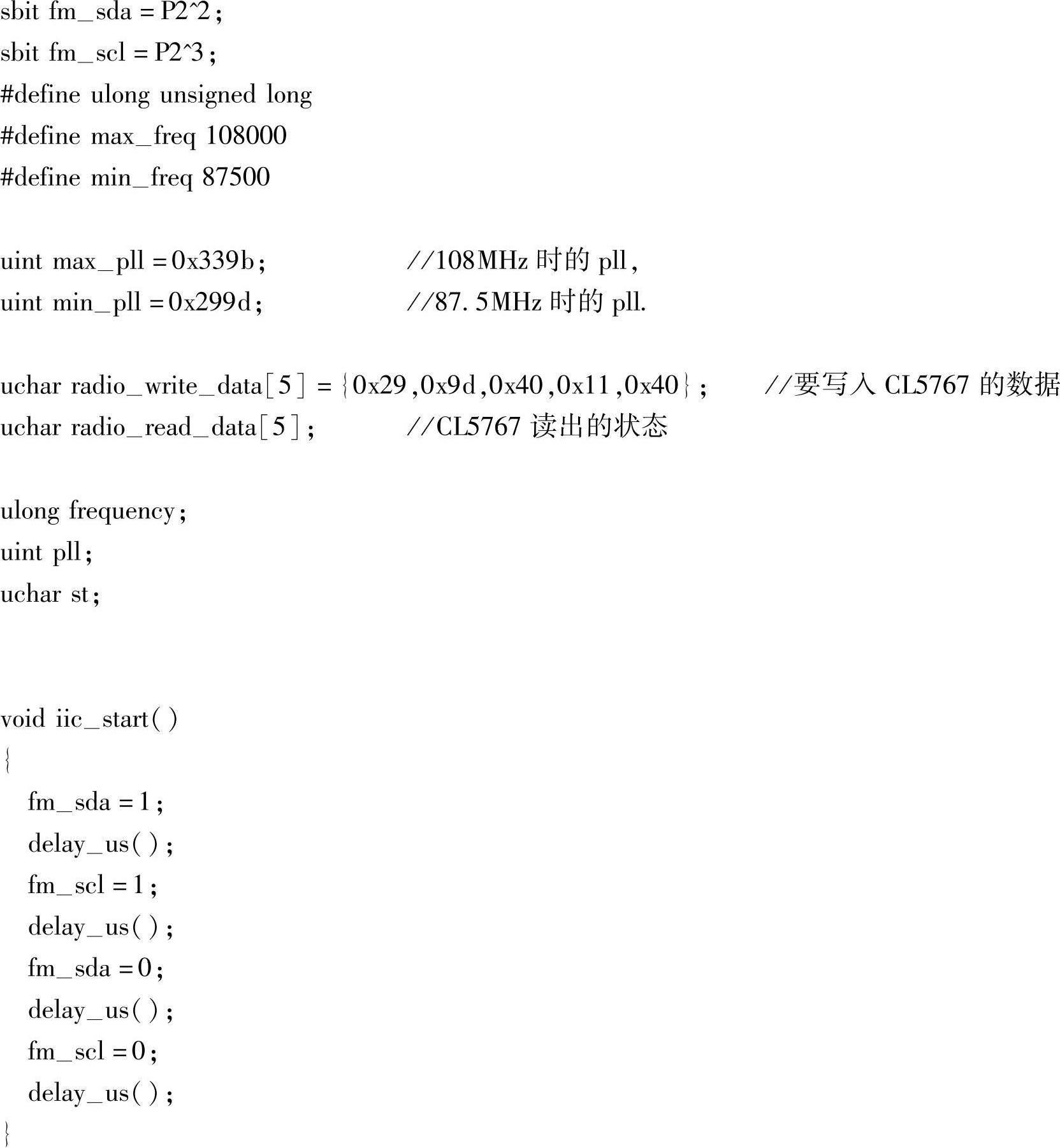

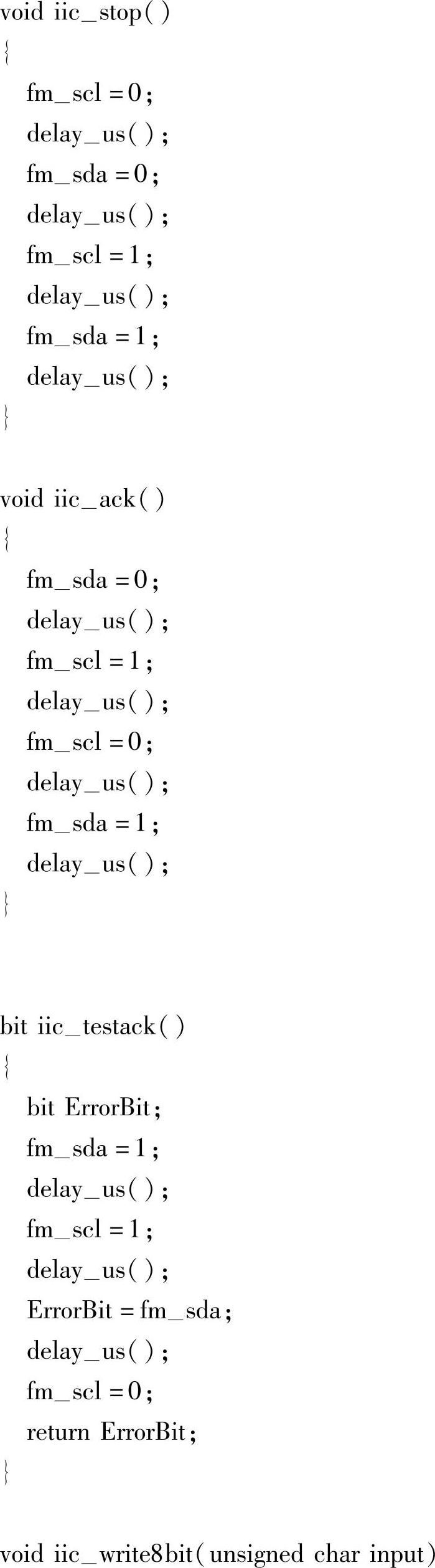

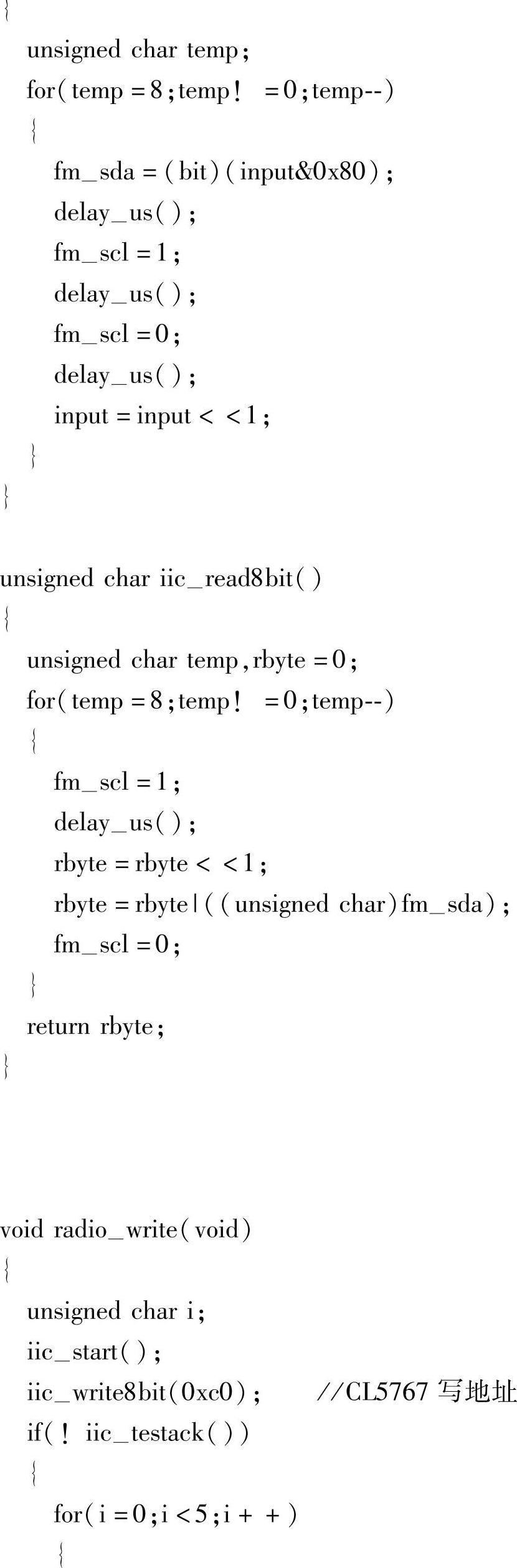

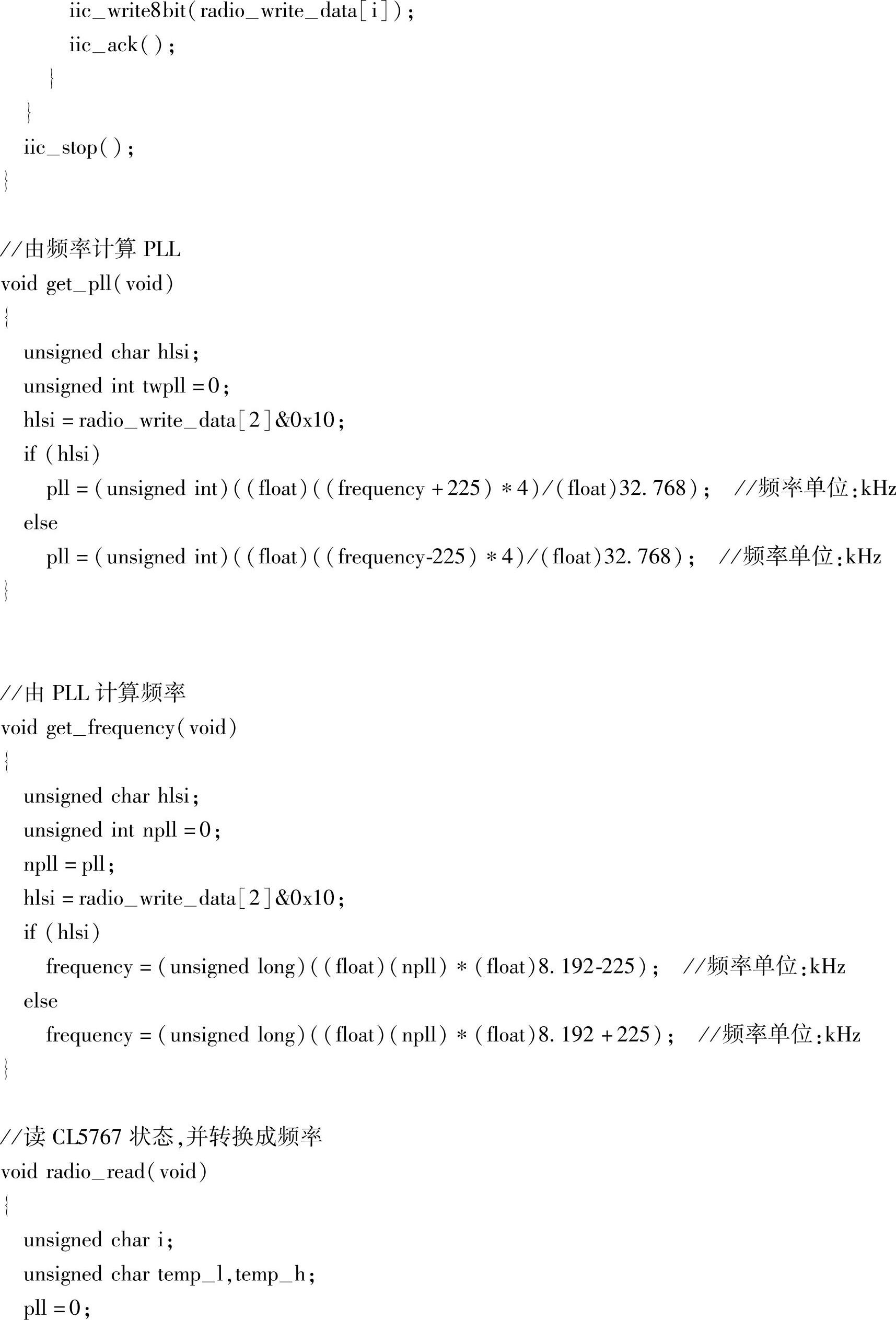

6.软件编程

(1)I2C-总线

I2C总线是通过两根I2C总线是通过两根线(串行数据线和串行时钟线)来连接元器件之间通信的总线,并根据地址识别每个器件。启动总线后的第一个字节的高七位是从器件的寻址地址。

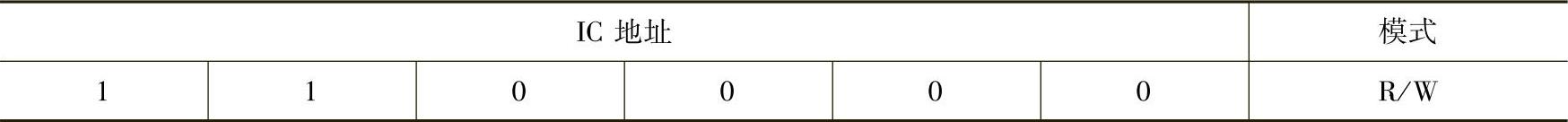

IC的地址为C0:1100000。

I2C总线的逻辑结构:收发机。

最低位未使用。

最大低电平和最小高电平分别限定在0.2VCCD和0.45VCCD。

总线模式(BUSMODE)引脚必须接地时工作在I2C-总线模式。

注:总线工作在最大时钟频率(400kHz)时,不能将IC连接到一个正工作在高时钟的总线上。

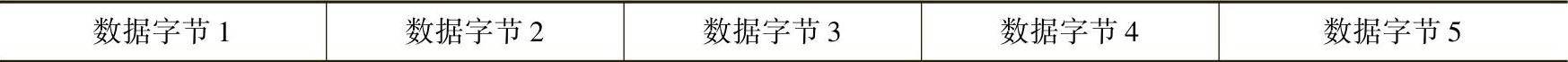

(2)数据传输数据顺序

地址,字节1,字节2,字节3,字节4,字节5(数据传送必须按顺序)。地址最低位为“0”,表示写操作到CL5767。每个字节的第七位被认为是最高位,并作为字节的第一位传送。在时钟的下降沿,数据变为有效信号。在每一字节后面的停止信号可以缩短传送时间。

在整个传输完成之前发送一个停止条件:保留的字节将包含以前的信息。如果一个字没有传送完,新的字节将被使用,但新的调谐周期不会开始。通过standby位设置,芯片可以工作在省电的待机模式,总线仍然激活。屏蔽总线界面可以减小待机电流。如果总线界面被屏蔽则程序没有待机模式,芯片维持正常工作,但已经脱离总线。软口1能够被用作调谐指示器输出,在搜台没有完成的时候,软口1输出低电平。当搜到预先设置的台或搜索完成或界定波段达到时,软口1输出高电平。当第五字节最大有效位设置为逻辑1时,锁相环的参考频率改变。调谐系统能够工作在XTAL2引脚接6.5MHz晶振。

(3)上电复位

在上电复位时,静音位置“1”,其他所有位置“0”。为了初始化集成块所有位必须重新设定。

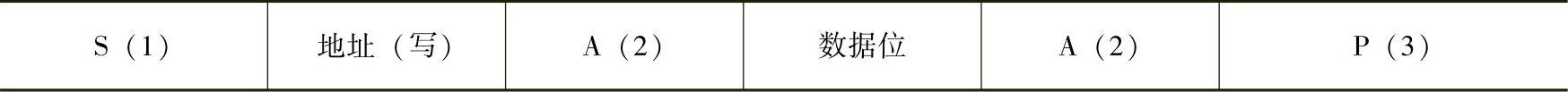

(4)I2C-总线协议

写模式见表11-1。

表11-1 写模式

注意:1:S为启动条件。

2:A为应答信号。

3:P为停止条件。

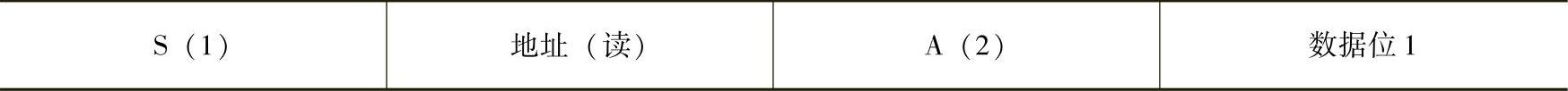

读模式见表11-2。

表11-2 读模式

注意:1:S为启动条件。

2:A为应答信号。

IC地址位见表11-3。

表11-3 IC地址位

注:1:读或者写模式

a)0对CL5767写操作。

b)1对CL5767读操作。

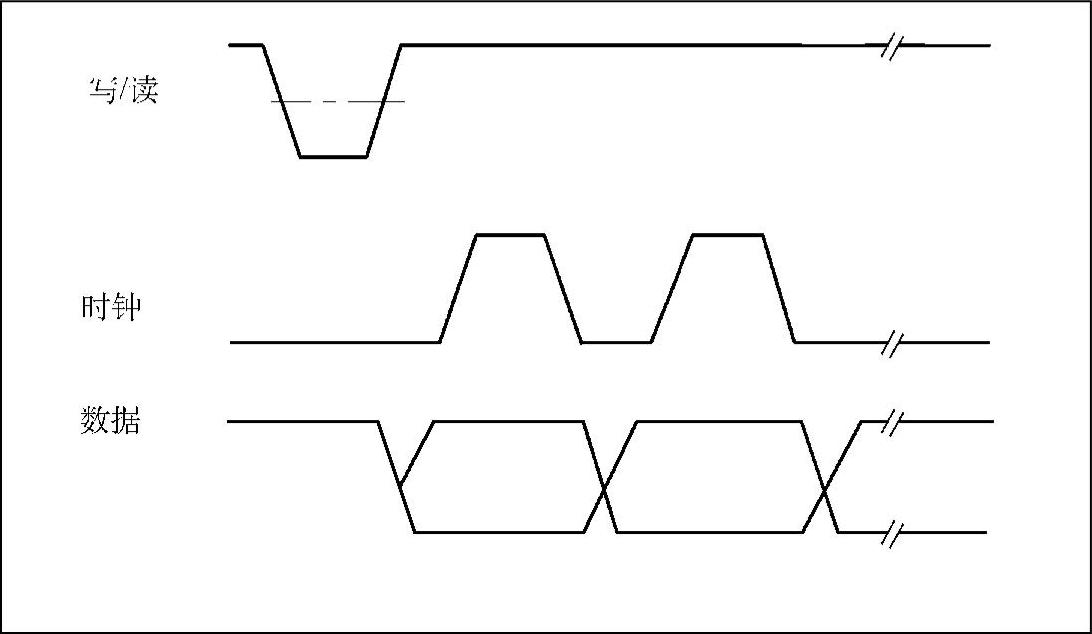

(5)3-线说明3-线控制

写/读,时钟和数据线;工作在最大时钟频率为1MHz。提示:通过standby位设置,芯片可以工作在省电的待机模式。在待机模式下芯片必须设置在写模式。在待机期间,当芯片设置为读模式时,芯片会保持数据。屏蔽总线界面可以减小待机电流。如果总线界面被屏蔽则程序没有待机模式,芯片维持正常工作,但已经脱离时钟和数据线。

(6)数据传输数据顺序

地址,字节1,字节2,字节3,字节4,字节5(数据传送必须按顺序)。在写/读控制的上升沿可以写数据到芯片。在时钟的上升沿之前,数据必须为有效信号。当时钟为低时可改变数据信号,在时钟的上升沿时数据被写入芯片。在以开始二字节或每个字节之后,如果有新的开始信号,数据传输被停止。在写/读控制的下降沿可以从芯片读数据。当时钟为低时,写/读控制改变。在写/读控制的下降沿数据端出现第一个字节的最大有效位。在时钟下降沿移存数据,在上升沿读数据。要实现两个连续的读或写操作,写/读必须固定在最少一个时钟周期。当一个搜索调谐请求被发送时,芯片将自动开始搜索,搜索方向和搜索停止电平可以设置。当搜到一个强度等于或大于停止电平时,调谐系统停止且准备好标志位为高。在搜索期间,当一个制式已经符合时,调谐系统停止且制式标志位为高。在这种情况下准备好标志位也为高。软口1能够被用作调谐指示器输出,在搜台没有完成的时候,软口1输出低电平。当搜到预先设置的台或搜索完成或界定波段达到时,软口1输出高电平。当第五字节最大有效位设置为逻辑1时,锁相环的参考频率改变。调谐系统能够工作在XTAL2引脚接6.5MHz晶振。

(7)上电复位

在上电复位时,静音位置“1”,其他所有位任意设置。为了初始化集成块所有位必须重新设定。

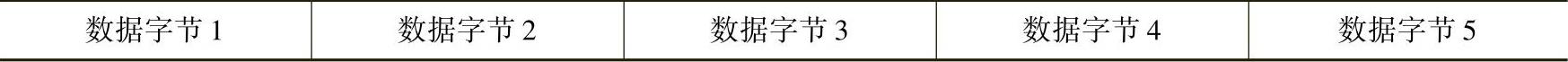

(8)写数据

3线写数据如图11-45所示。

图11-45 3线写数据

写模式见表11-4。

表11-4 写模式

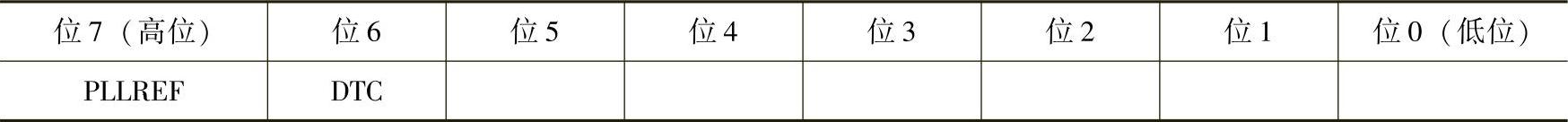

数据字节1的格式见表11-5。(https://www.xing528.com)

表11-5 数据字节1的格式

数据字节1的各个位描述见表11-6。

表11-6 数据字节1的各位描述

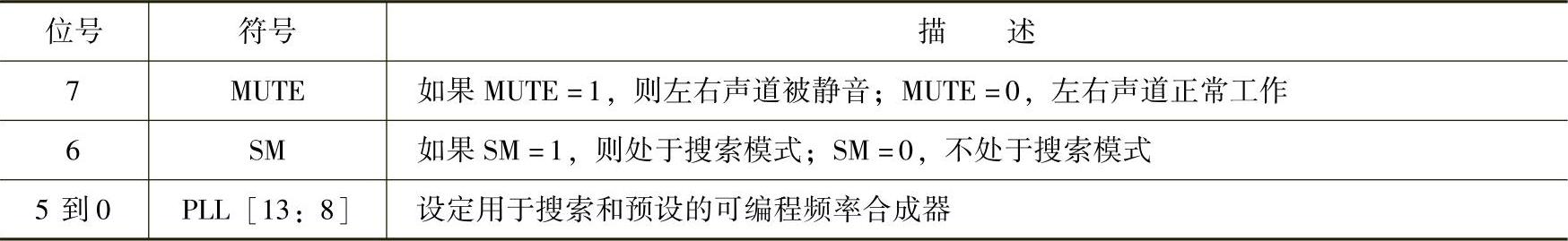

数据字节2的格式见表11-7。

表11-7 数据字节2的格式

数据字节2的各个位描述见表11-8。

表11-8 数据字节2的各个位描述

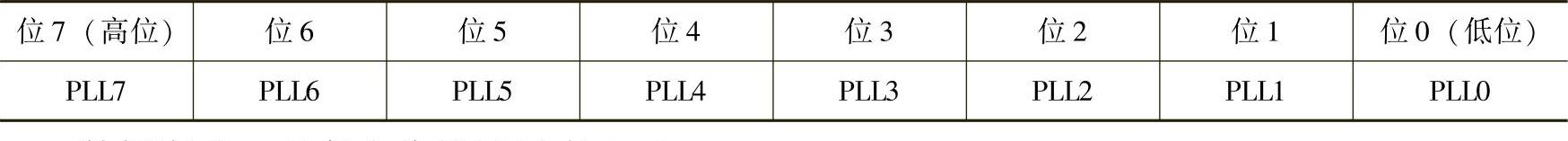

数据字节3的格式见表11-9。

表11-9 数据字节3的格式

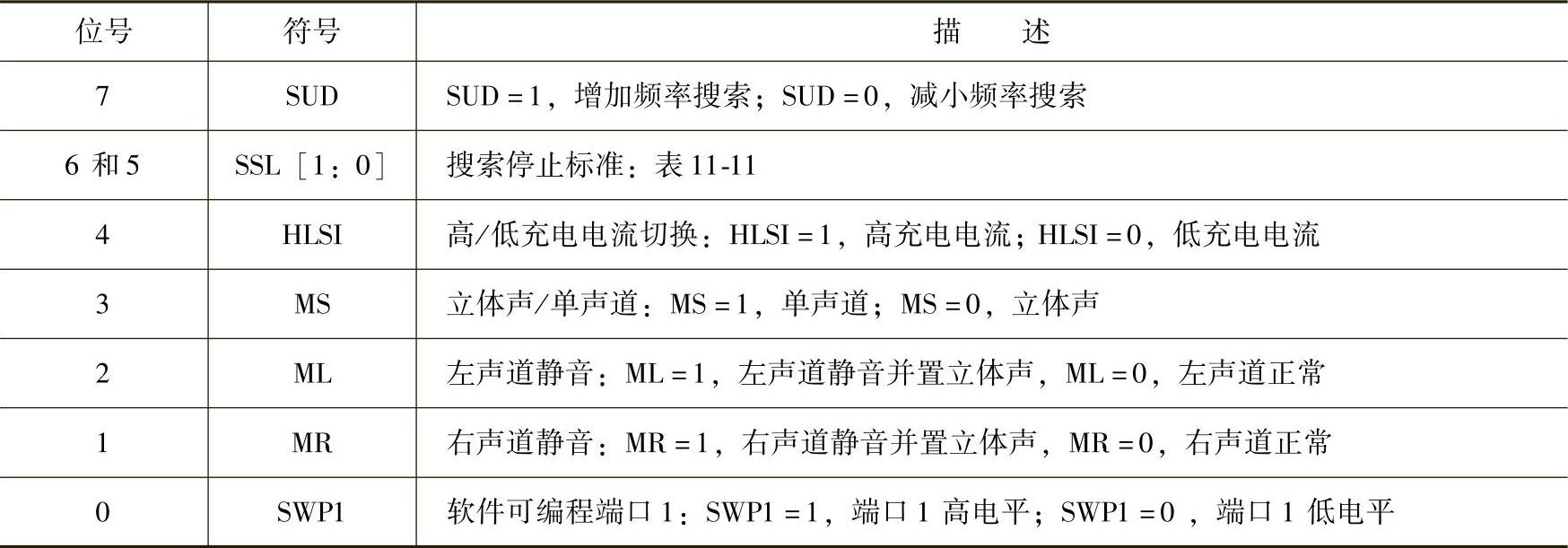

数据字节3的各个位描述见表11-10。

表11-10 数据字节3的各个位描述

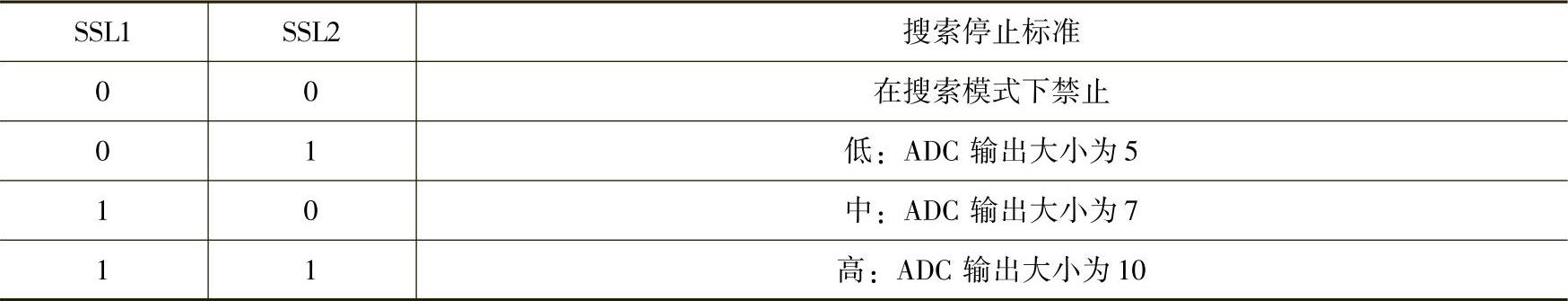

搜索停止标准设定见表11-11。

表11-11 搜索停止标准设定

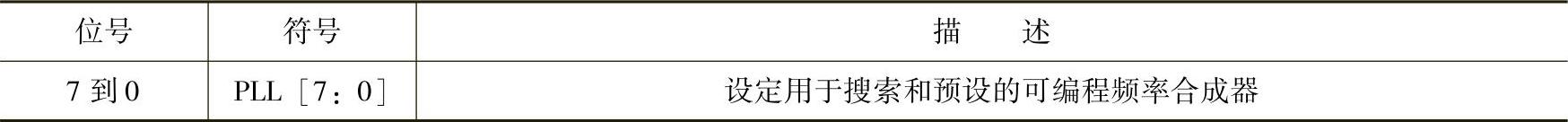

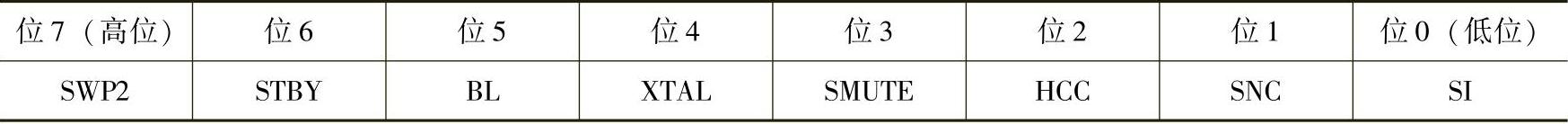

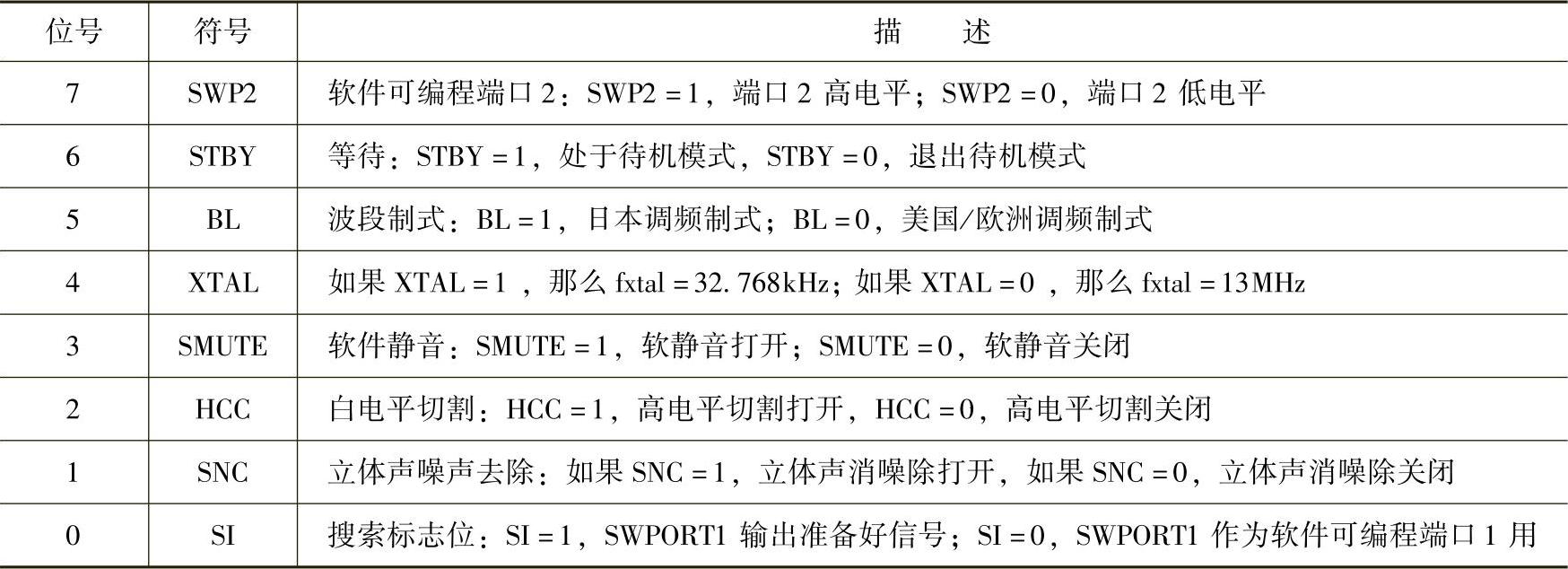

数据字节4的格式见表11-12。

表11-12 数据字节4的格式

数据字节4的各个位描述见表11-13。

表11-13 数据字节4的各个位描述

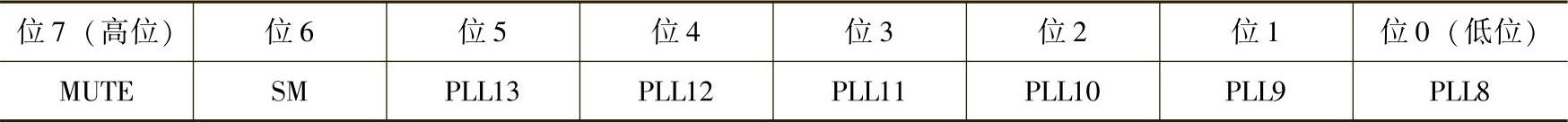

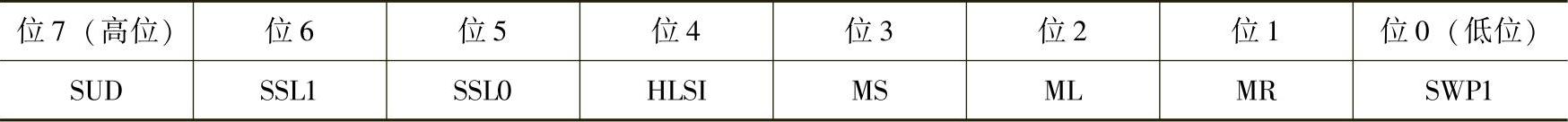

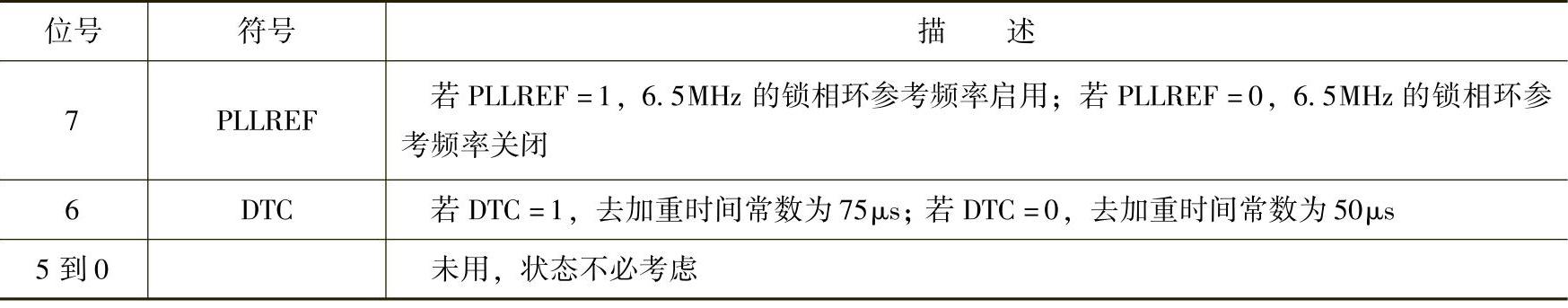

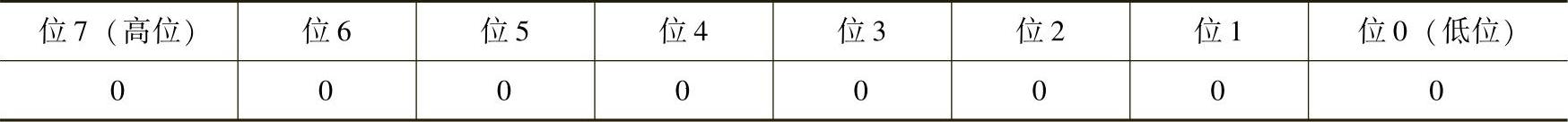

数据字节5的格式见表11-14。

表11-14 数据字节5的格式

数据字节5的各个位描述见表11-15。

表11-15 数据字节5的各个位描述

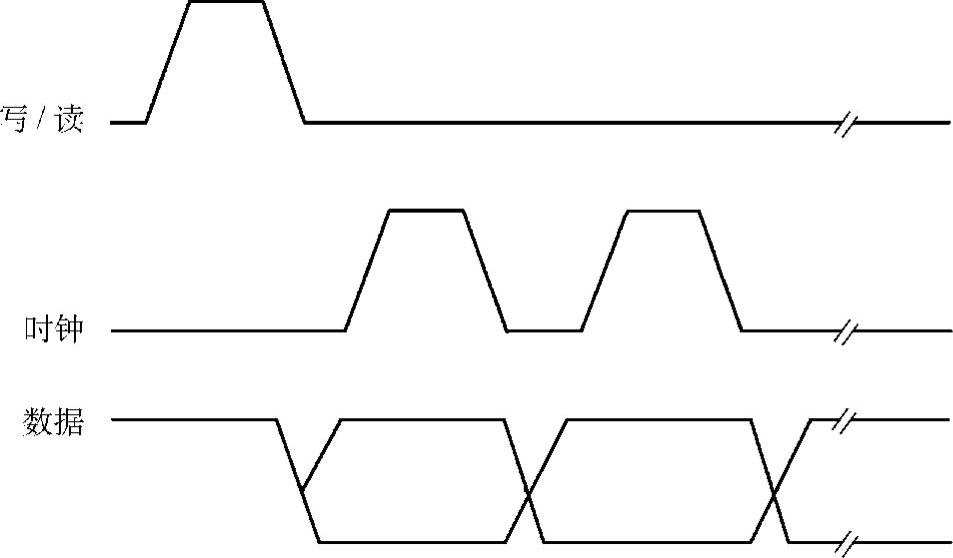

(9)读数据

如图11-46所示。

读模式见表11-16。

表11-16 读模式

图11-46 3线读数据

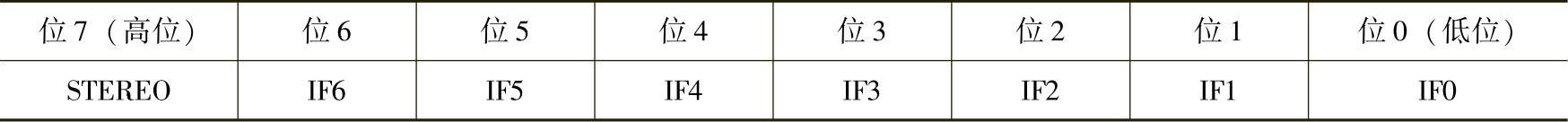

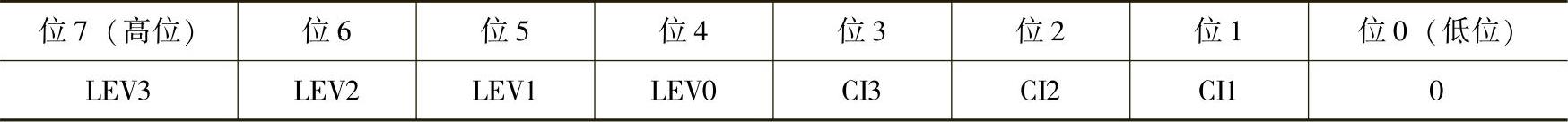

数据字节1的格式见表11-17。

表11-17 数据字节1的格式

数据字节1的各个位描述见表11-18。

表11-18 数据字节1的各个位描述

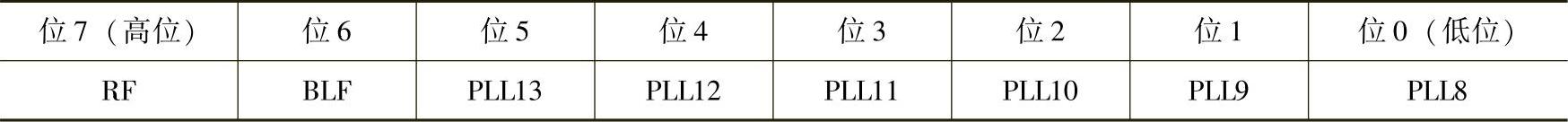

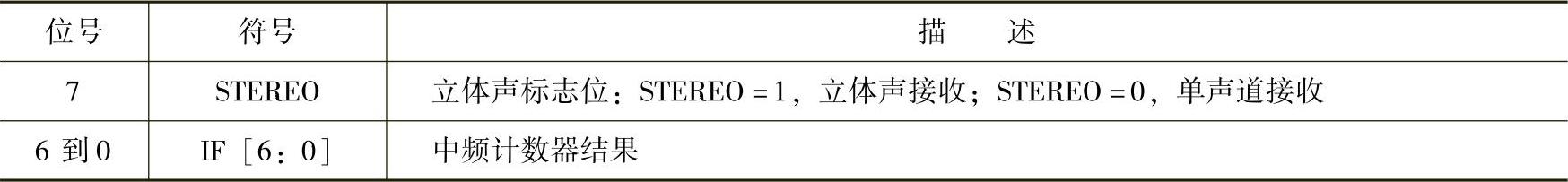

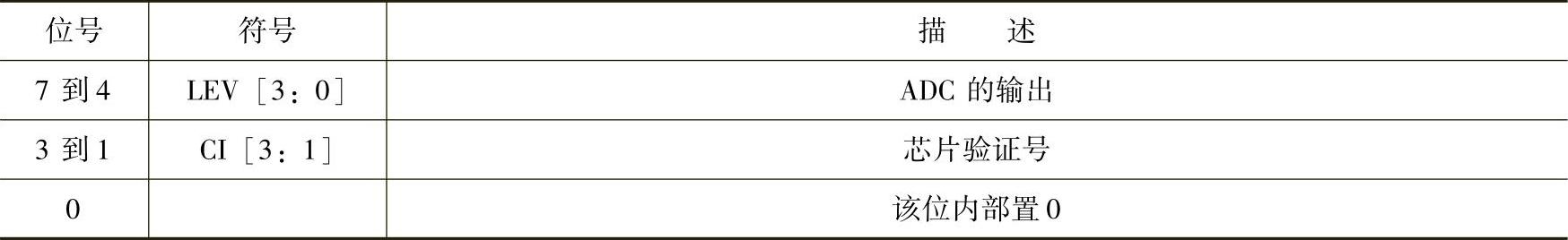

数据字节2的格式见表11-19。

表11-19 数据字节2的格式

数据字节2的各个位描述见表11-20。

表11-20 数据字节2的各个位描述

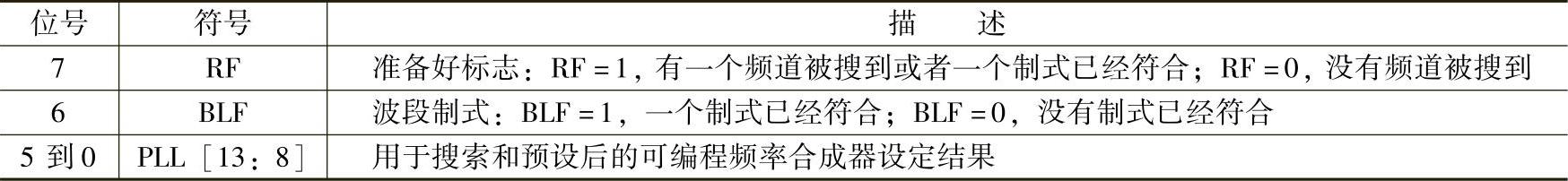

数据字节3的格式见表11-21。

表11-21 数据字节3的格式

数据字节3的各个位描述见表11-22。

表11-22 数据字节3的各个位描述

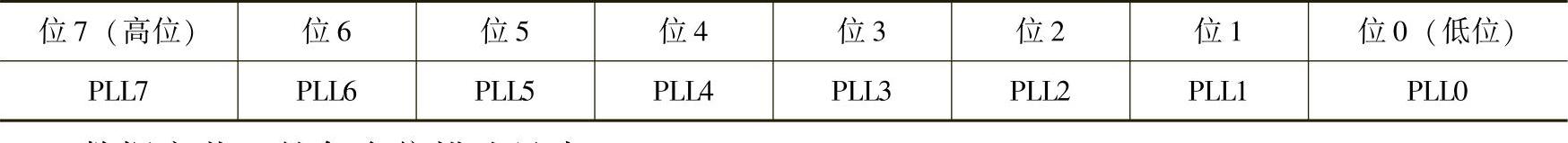

数据字节4的格式见表11-23。

表11-23 数据字节4的格式

数据字节4的各个位描述见表11-24。

表11-24 数据字节4的各个位描述

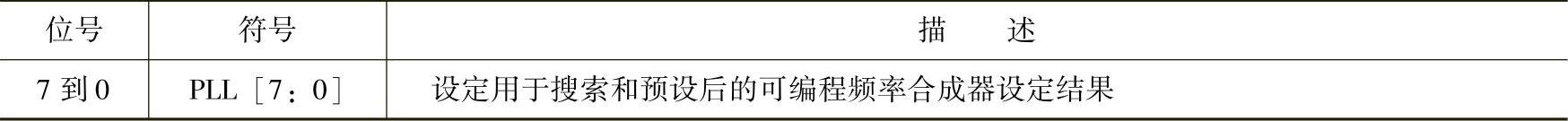

数据字节5的格式见表11-25。

表11-25 数据字节5的格式

数据字节5的各个位描述见表11-26。

表11-26 数据字节5的各个位描述

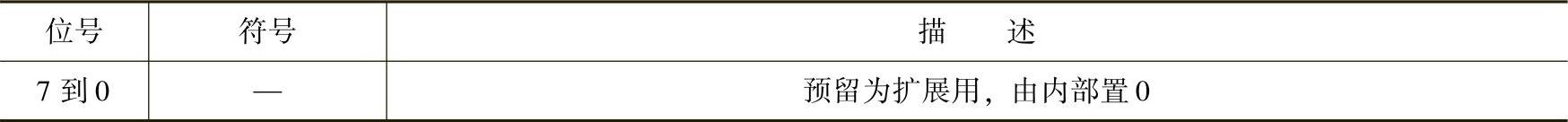

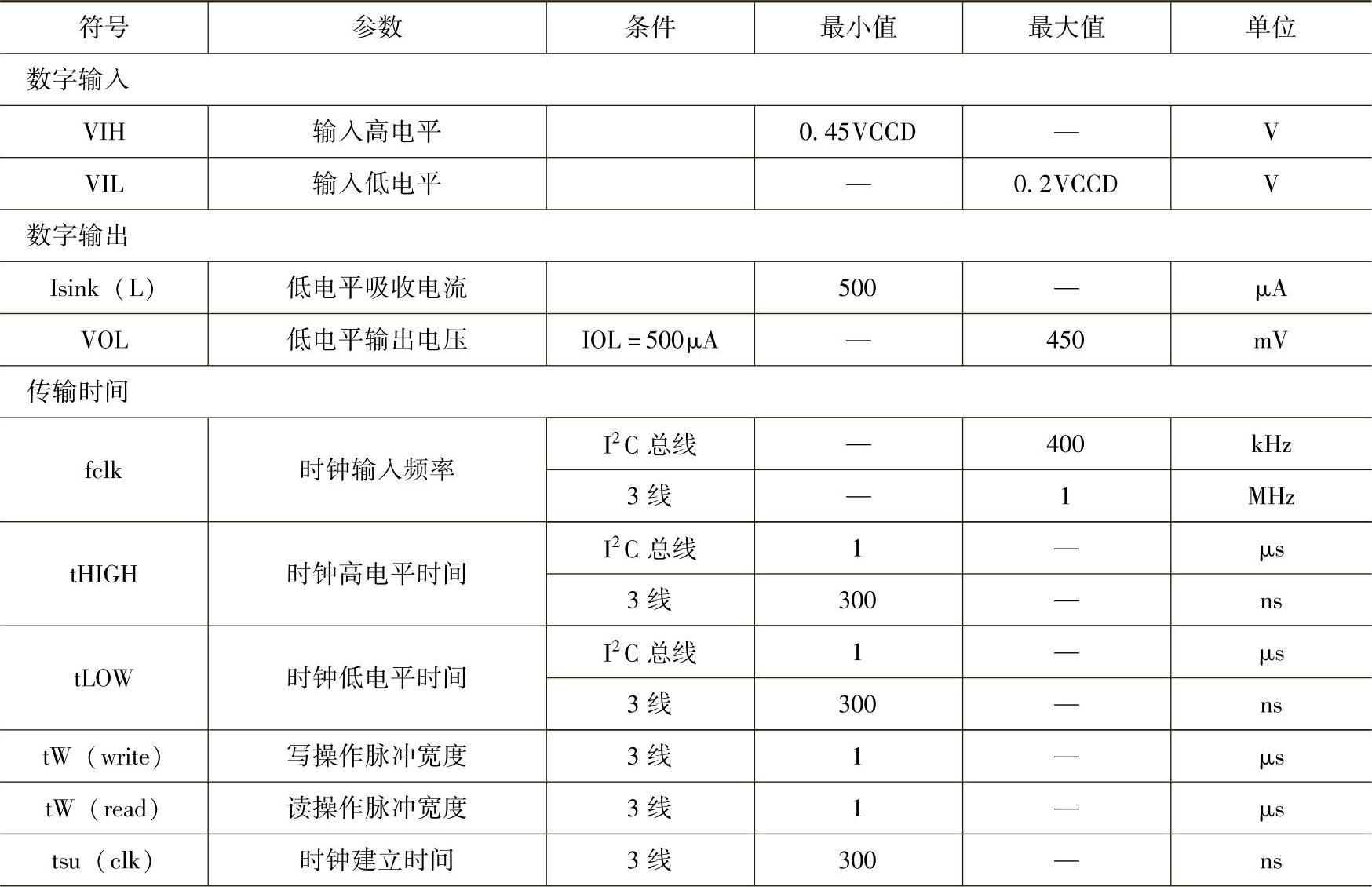

(10)总线传输时间

数字电平和传输时间见表11-27。

表11-27 数字电平和传输时间

(续)

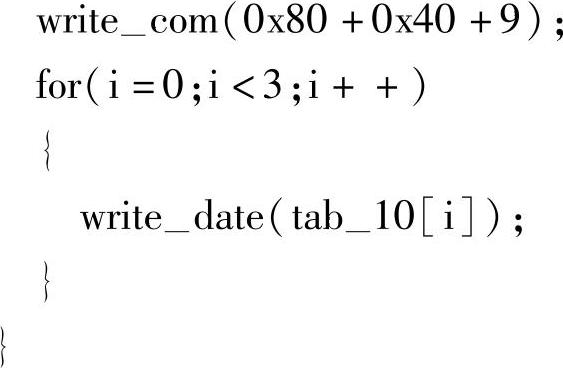

7.C语言实例程序

功能:实现按键控制向上/向下频率进行搜索电台

对于select模型,首先建立套接字集合,即FD—SET,该集合分为可读、可写和出错三种状态;将需要的套接字加入相应集合,然后调用select函数,把集合和超时时间设置传入函数,如果超时时间设为NULL,socket则为阻塞方式工作。当select返回时,用FD—ISSET宏判断对应集合返回情况。即用一个函数处理多个套接字的通信。对于UDP协议,可写没用实际意义,只代表本机缓冲可用,不代表对端能够接收。所以只用select函数判断两个套接字的可读状态。当确定某个套接字可读时,调用recvfrom函数从指定socket接收数据。由于UDP是数据报协议,需保留信息边界,即发送端调用了几次sendto,接收端就要调用几次recvfrom,不存在一次接收到多个包的情况。所以可以直接根据接收到的数据大小判断接收到的数据包类型,然后调用对应的包处理函数,进入对应状态机。这也是所谓了Dispatch分包功能。这个UDP接收线程的工作方式和原理客户端与服务器端相同,可以理解为整个协议栈的入口。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。