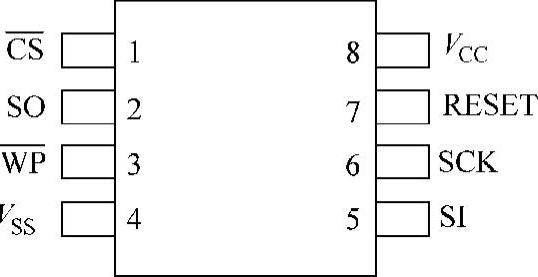

X25045/X5045的引脚排列如图10-60所示。

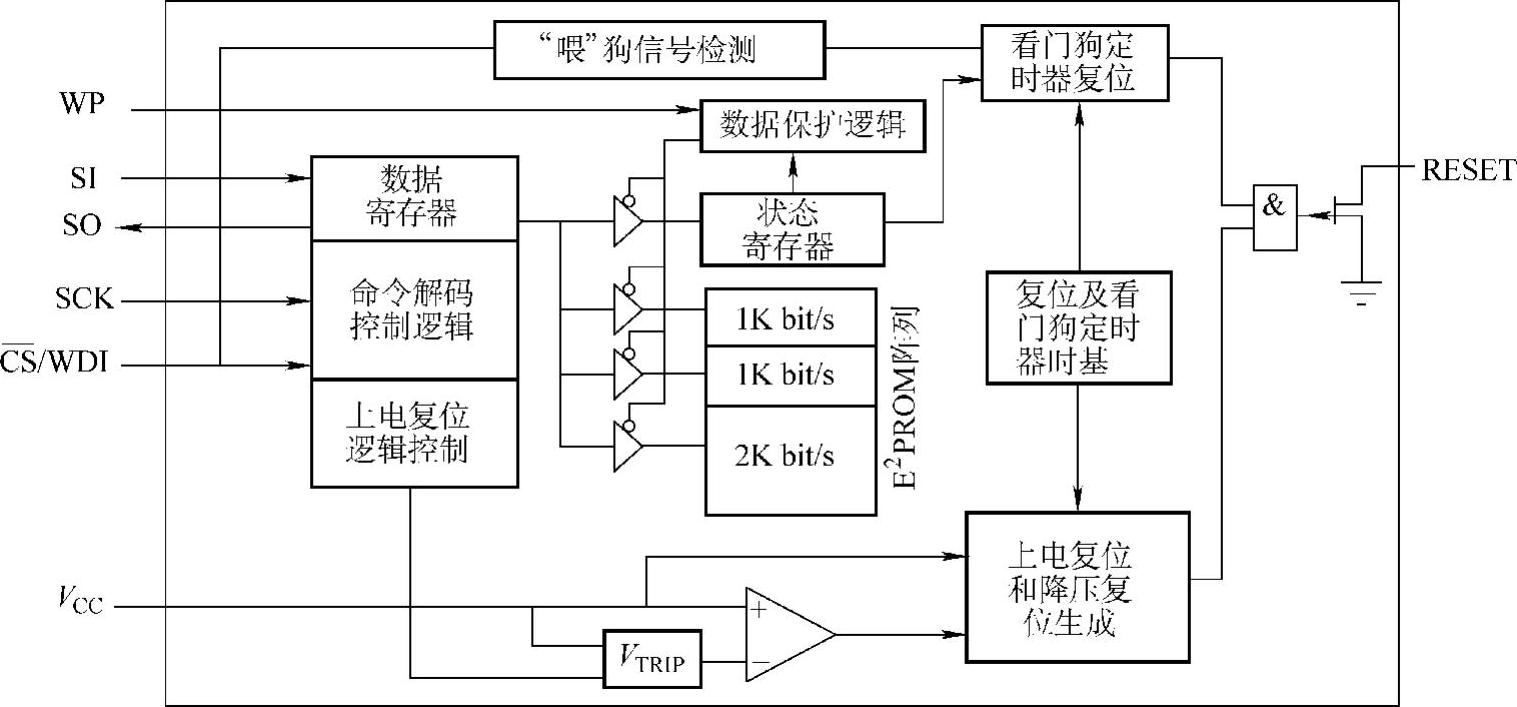

1.X25045/X5045的结构

X25045/X5045的结构如图10-61所示,主要功能组成部分为:看门狗电路、存储器电路、上下电复位电路。其中看门狗电路包含喂狗信号输入电路、看门狗定时器、复位信号输出等部分;E2PROM部分则包含了数据寄存器、命令寄存器、数据保护逻辑、E2PROM阵列、状态寄存器等;上下电检测则包含带隙基准源、比较器、复位信号产生电路等。具体的逻辑关系可以从图10-61中看的一目了然。

2.X25045/X5045的E2PROM

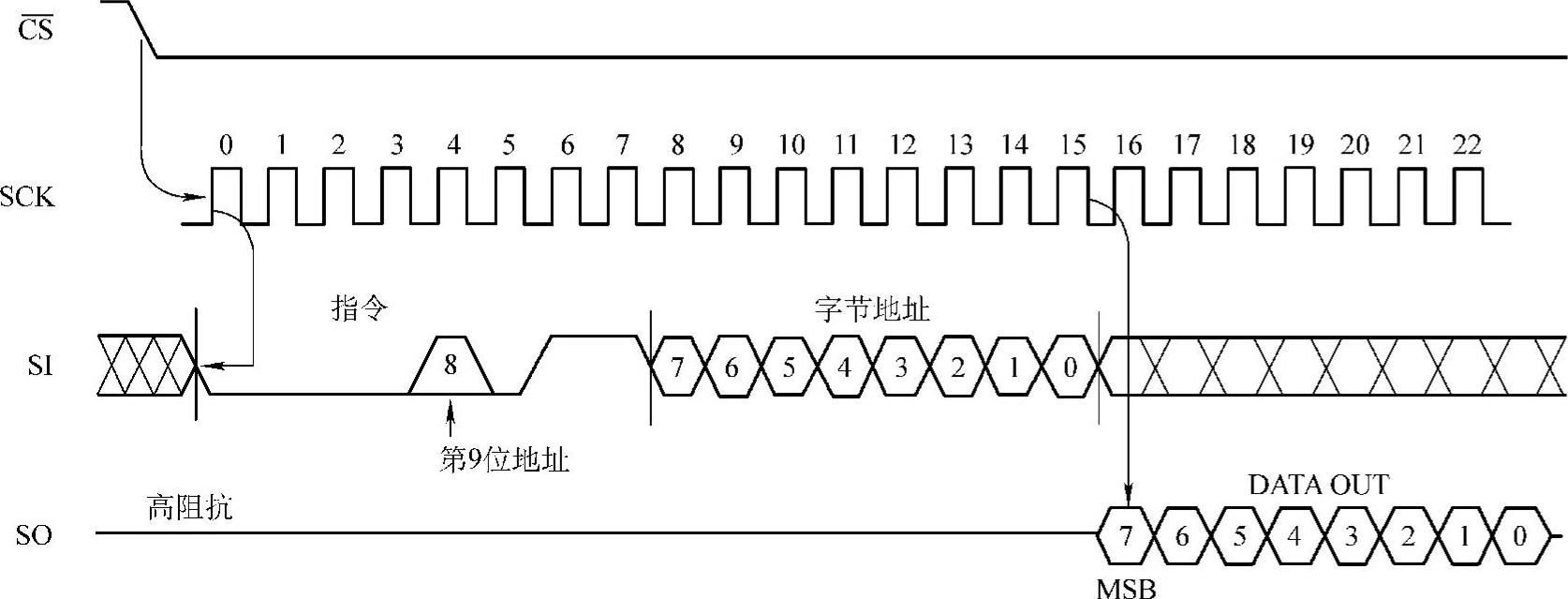

把看门狗电路和E2PROM结合起来,是X25045/X5045的一大特点。通过SPI总线,可以访问芯片内部的512字节串行E2PROM,它们是采用CMOS工艺制造的,每个字节可擦写10万次以上,并可保存数据100年以上。其接口时序如图10-62所示。

图10-60 X25045/X5045的外部引脚排列

CS—芯片选择输入 SO—串行数据输出WP—写保护 Vss—地 SI—串行数据输入 SCK—串行时钟输入 RESET—复位输出, 高有效Vcc—电源电压

芯片工作期间,CS端应始终保持低电平。在一个读时序周期内,数据在串行时钟SCK的下降沿,由SO端串行输出,而缓冲地址或数据在串行时钟SCK的上升沿,由SI端输入锁存。当CS端为低电平时,写保护功能部分可以使用。当CS端为高电平时,所有写保护功能才正常。值得注意的是,在芯片选通时,CS端变为低电平,将要中断对X25045的写操作,若正处在内部写周期内,则对写操作没有影响。

图10-61 X25045/X5045的结构

图10-62 X25045/X5045内部的E2PROM访问时序(https://www.xing528.com)

对X25045/X5045内部的E2PROM的访问是通过一个8bit指令寄存器来实现的,该寄存器可以通过引脚SI来访问,数据在串行时钟输入的上升沿由时钟同步输入。另外,对芯片的所有操作都需要通过对该寄存器的写命令来完成。其中操作主要有:

1)WREN:设置写使能锁存器(允许写)。

2)WRDI:复位写使能锁存器(禁止写)。

3)RDSR:读状态寄存器。

4)WRSR:写状态寄存器。

5)READ:从所选地址开始的存储器中读出数据。

6)WRITE:把数据写入所选地址开始的存储器中。

在执行写操作之前写使能锁存器必须被置位,在写操作完成后该寄存器必须被复位。其指令格式不再详细介绍,可参考详细的资料。

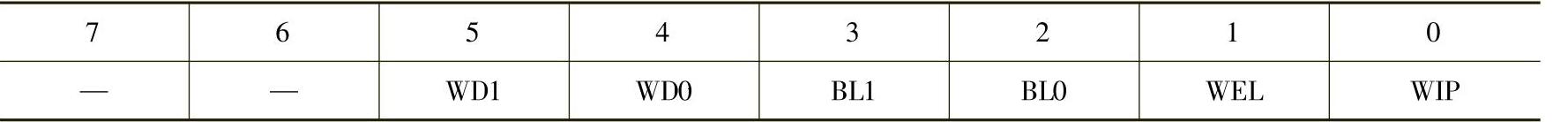

X25045有一个状态寄存器,可以用来提供X25045的状态信息以及设置块保护和看门狗的超时功能,其格式为:

WIP位表示X25045是否在向E2PROM写数据。该位是1时,表示正在进行写操作,此时不能向其写数据;反之,则是没有写操作进行,可以向其写数据。WEL位是写使能锁存器的状态位。可以由指令进行复位和置位操作。写使能锁存器被复位时向其写操作被禁止。

由WREN指令可以对状态寄存器中的BL0,BL1,WD0,WD1进行设置。BL0和BL1位确定E2PROM的块保护地址范围。WD0和WD1位是看门狗超时功能的设定位,可以设置不同的周期(典型值1.4s、600ms、200ms)。当WD0和WD1同时为1时,功能被禁止。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。