μDMA控制器是一种灵活和高可配置的DMA控制器,被设计成能配合Cortex-TM4C处理器的内核工作以实现高效的数据传输。它支持多种数据宽度与地址递增策略,且各DMA通道之间具有不同的优先级和多种传输模式,允许复杂的可编程数据传输。μDMA控制器占用总线总是从属于处理器内核,所以它不会影响到处理器的总线事务。因为μDMA控制器只占用处理器内核的空闲总线周期,它提供的数据传输带宽基本上是不受约束的,因而不影响系统的其他部分。通过对总线架构的优化大大提升了处理器内核和μDMA控制器有效地共享片上总线的能力,从而提高了它的性能。优化包括RAM分段和外设总线分段,在许多情况下,允许处理器内核心和μDMA控制器同时访问总线并进行数据传输。

μDMA控制器可以和从片上SRAM进行双向数据传输。然而,由于闪存和ROM都位于一个单独的内部总线,因此闪存或ROM不可能传输数据到μDMA控制器中。

每个μDMA控制器支持的外设功能,都有一个可被独立配置的专用通道。μDMA控制器使用在系统存储器中由处理器维护的通道控制结构体,实现了一种独特的配置方法。不但支持简单的传输模式,而且它也可以在存储器中建立复杂的“任务”列表,允许μDMA控制器收到单次传输请求后,根据“任务列表”执行任意大小的数据传输和接收从任意位置传送过来的数据。μDMA控制器还支持使用乒乓缓冲以适应与外设的双向数据流。

每个通道还可配置其仲裁大小,是指在μDMA控制器重新仲裁通道的优先级之前,以突发方式传送的项目数量。当每次遇到一个μDMA服务请求时,根据配置的仲裁数目,可精准控制到底有多少项目与外设之间发生了数据传输。

1.通道分配

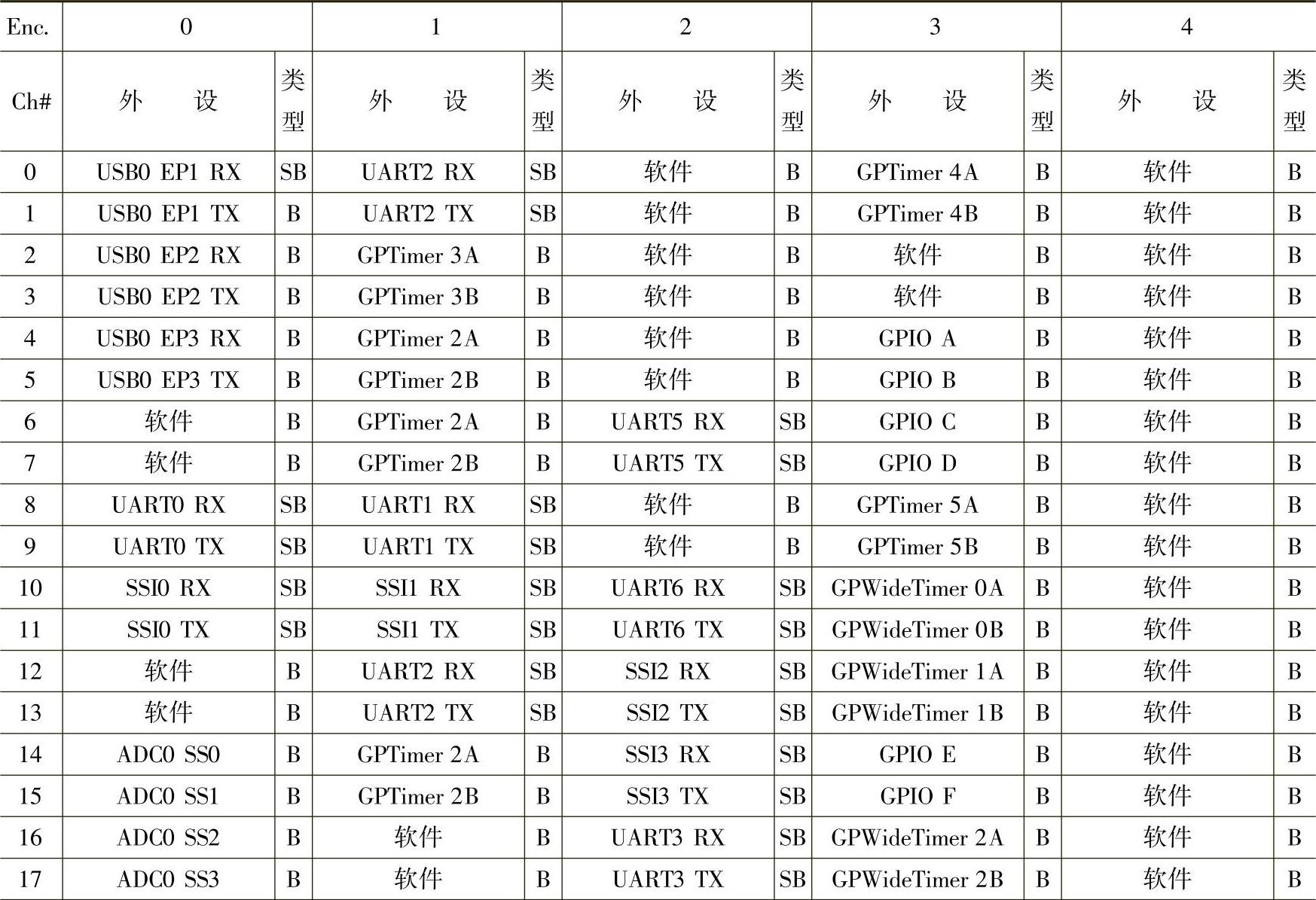

μDMA控制器通道分配见表13-1。

表13-1 μDMA通道分配

(续)

注:1.S为单个请求、B为突发请求、SB为单个加突发请求。

2.表中注明“软件”的通道可用于将来外设的扩展,这些通道目前仅软件可访问,不可连接外设。30号通道为软件专用通道。

2.优先级

每个通道μDMA的优先级由通道的序号和通道的优先级标志位决定。第0号μDMA通道的优先级最高,通道的序号越大,反而其优先级越低。每个μDMA通道都有一个可设置的优先级标志位来确定其优先级高低。若某个通道的优先级位置位,则该通道将具有高优先级,其优先于所有未将此标志位置位的通道。假如有多个通道都设为高优先级,这时将按通道序号来区分它们的优先级高低。通道的优先级位可通过DMA通道优先置位寄存器(DMAPRIOSET)置位,而通过DMA通道优先清除寄存器(DMAPRIOCLR)清零。

3.仲裁个数

当某个μDMA通道请求传输时,μDMA控制器将对所有发出请求的通道进行仲裁,并且只向优先级最高的通道提供服务。一旦传输开始,首先将持续传输一定数量的数据之后再对发出请求的通道进行仲裁。每个通道的仲裁个数都是可设置的,其有效范围为1~1024个项目。当μDMA控制器按照仲裁个数传输了若干个项目之后,随后将检查所有发出请求的通道,并只向优先级最高的通道提供服务。

若某个优先级较低的μDMA通道仲裁个数设置过大,可能使高优先级通道的传输延迟增加,这是因为,μDMA控制器需要等待低优先级的突发传输完全结束之后才会重新进行仲裁,以检查是否存在更高优先级的请求。因此,建议对于低优先级通道的仲裁个数不应设置过大,以充分保障系统对高优先级μDMA通道的响应速度。

4.请求类型

μDMA控制器可用于响应来自外设的两种请求:单次请求或突发请求。每种外设可支持其中一种或两种类型,单次请求表示外设已准备好传输一个项目,而突发请求则表示外设已准备好传输多个项目。

根据外设发出的是单次请求还是突发请求,μDMA控制器的响应也会有所不同。假设同时发出了单次请求和突发请求,且μDMA通道已按突发请求设置,则会优先响应突发请求。各种外设对这两种请求类型的支持见表13-2。

表13-2 支持的请求类型

5.通道配置

μDMA控制器采用在系统内存中保存一个控制表,该表包含多个通道控制的结构体,而每个μDMA通道在控制表中可能有一个或两个结构体。该表的每个结构体都包含源指针、目的指针、传输个数、传输模式。该表可定义到系统内存中的任意连续位置,并按1024字节边界对齐。

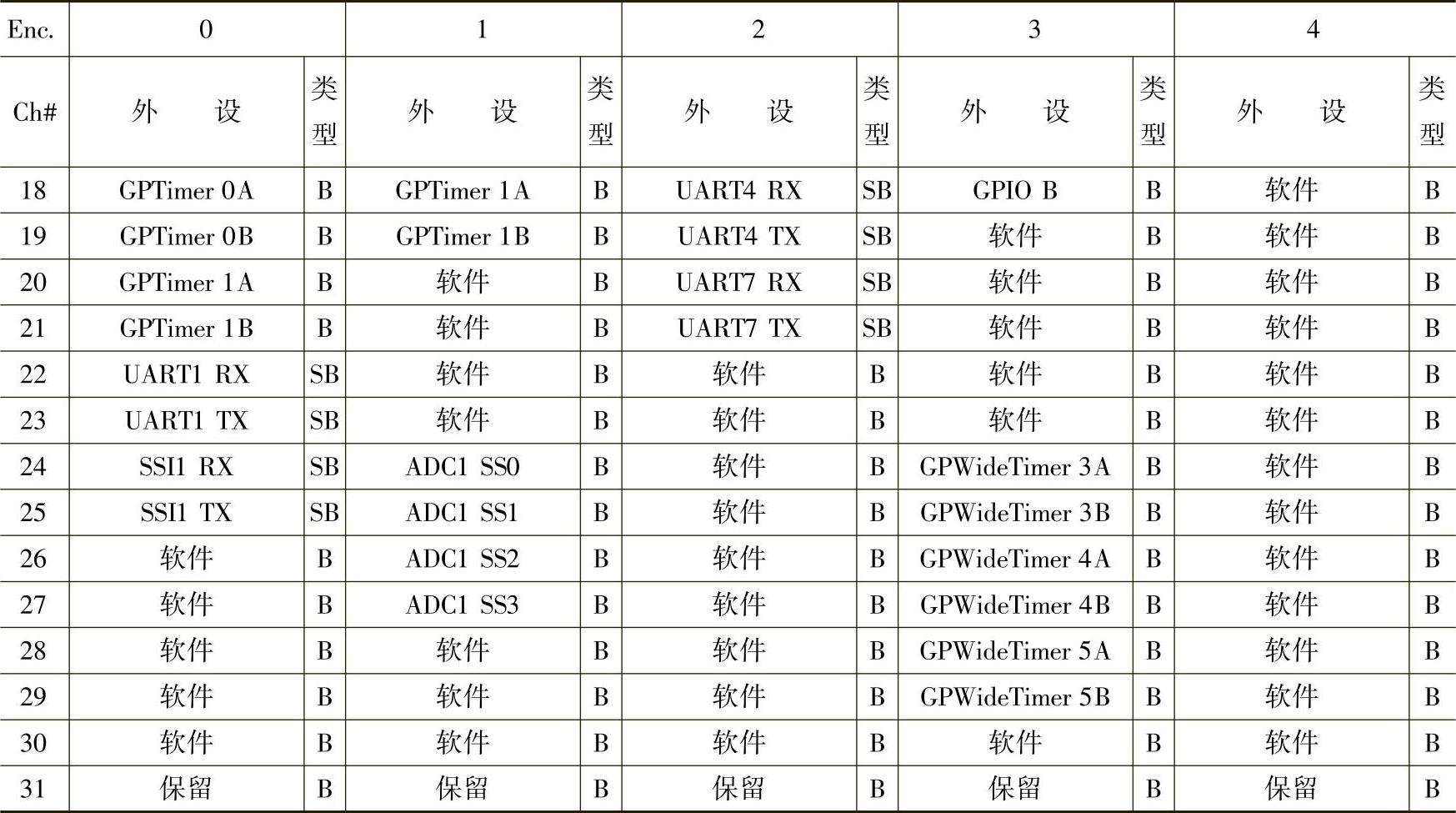

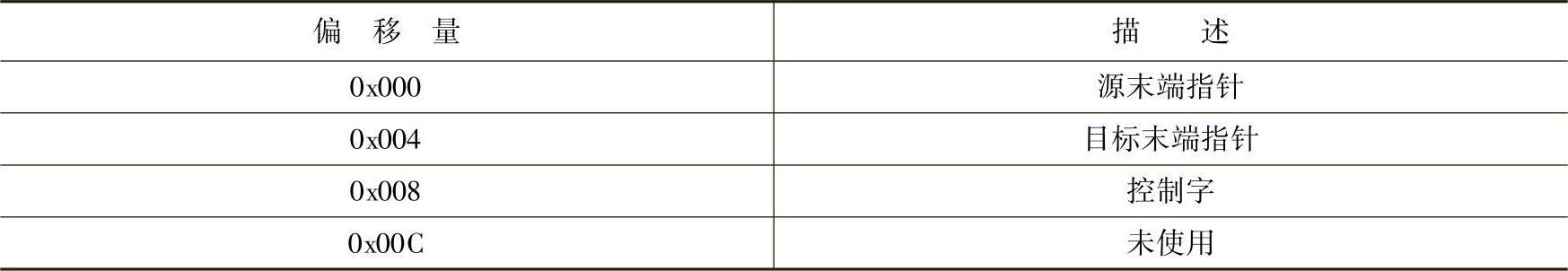

表13-3列出了通道控制表的内存布局。结构体由主控制结构体和副控制结构体组成。在控制表中,所有主控制结构体都在表的前半部分,而副控制结构体都在表的下半部分。在较简单的传输模式中,对传输的连续性要求不高,允许在每次传输结束后再重新配置、重新启动。这种情况一般不需要副控制结构体,因此内存中只需放置表的前半部分即可,而后半部分所占用的存储空间可另作它用。如果采用加复杂的传输模式(如乒乓模式或散聚模式),就需要用到副控制结构体,此时整个控制表都必须加载到存储器中。

对于控制表中任何未用到的存储块都可留给应用程序使用,包括任何应用程序未用的通道控制结构体与各个通道中未用到的控制字。

表13-3 控制结构体存储器映射

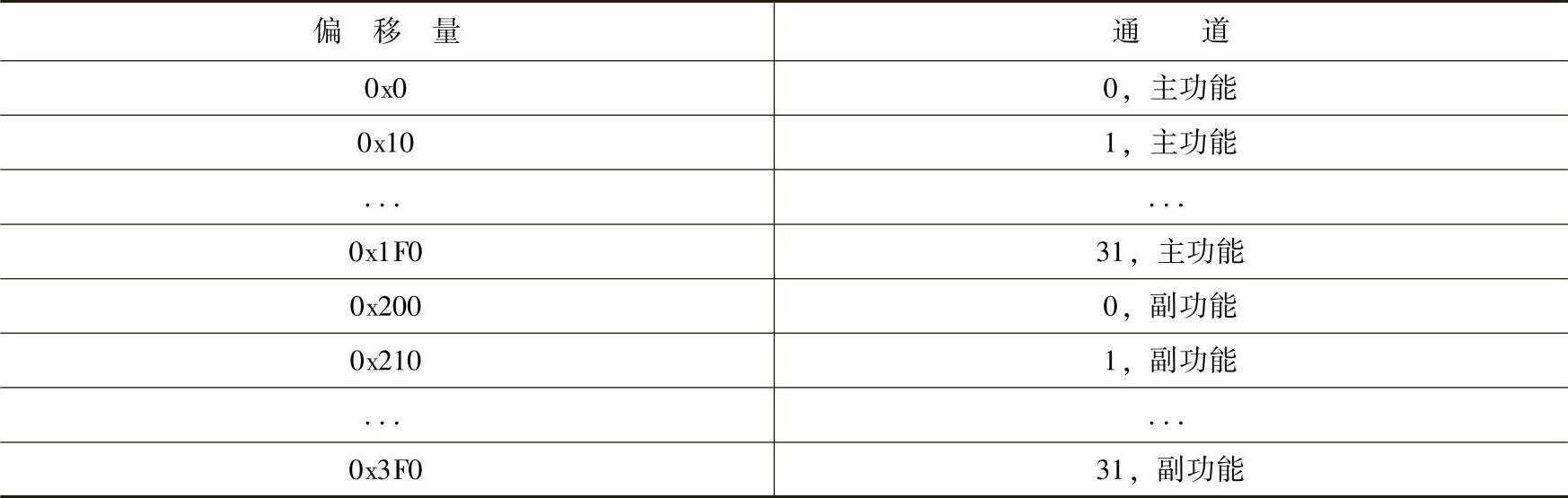

表13-4列出了控制表中单个控制结构体项的内容,并按照16字节边界对齐方式。每个结构体项由4个长整型项组成:源末端指针、目的末端指针、控制字与一个未用的长整型项。末端指针是指向传输过程最末一个单元地址的指针(包含其本身)。若源地址或目的地址无需自动递增(如外设寄存器),则指针应当指向待传输的地址。

表13-4 通道控制结构体

μDMA控制器在传输进行时会自动更新传输大小字段和传输模式字段。在传输完成之后,会使传输个数变为0,传输模式变为“已停止”。因控制字是由μDMA控制器自动修改的,则在每次新建传输之前必须手动配置,而源末端指针和目的末端指针不会被自动修改,只要源地址或目的地址不变,就无需再度配置。

在启动传输之前,必须先将DMA通道使能设置寄存器(DMAENASET)中的相应标志位置位来使能μDMA通道。当要禁止某个通道时,可将DMA通道使能清除寄存器(DMAENACLR)中的相应标志位置位即可,此外,在某个通道的μDMA传输完成后,控制器将自动关闭该通道。

6.传输模式

μDMA控制器支持多种传输模式,前两种模式支持简单的单次传输,而后几种模式可实现持续数据传输。

(1)停止模式

停止模式虽为控制字中传输模式字段的有效值,但它并不是一种真正的传输模式。当控制字中的传输模式为停止模式时,μDMA控制器并不会对该通道进行任何传输,而一旦该通道使能时,μDMA控制器还将自动关闭该通道。在任何μDMA传输结束后,μDMA控制器都会自动将通道控制字的传输模式字段改为停止模式。(https://www.xing528.com)

(2)基本模式

当设备发出一个有效请求时,μDMA控制器执行简单数据传输。此模式用于在外设发出有效的请求信号后,无论何时数据都将被传输。如果请求信号无效,无论是否传输结束都将停止传输。在基本模式中,当所有项目传输结束后,μDMA控制器会自动将该通道置为停止模式。

(3)自动请求模式

执行一个由请求启动的简单传输,即使请求被撤回,传输也将继续进行,直到完成整个数据传输。此模式适用于由软件启动的传输。

(4)乒乓模式

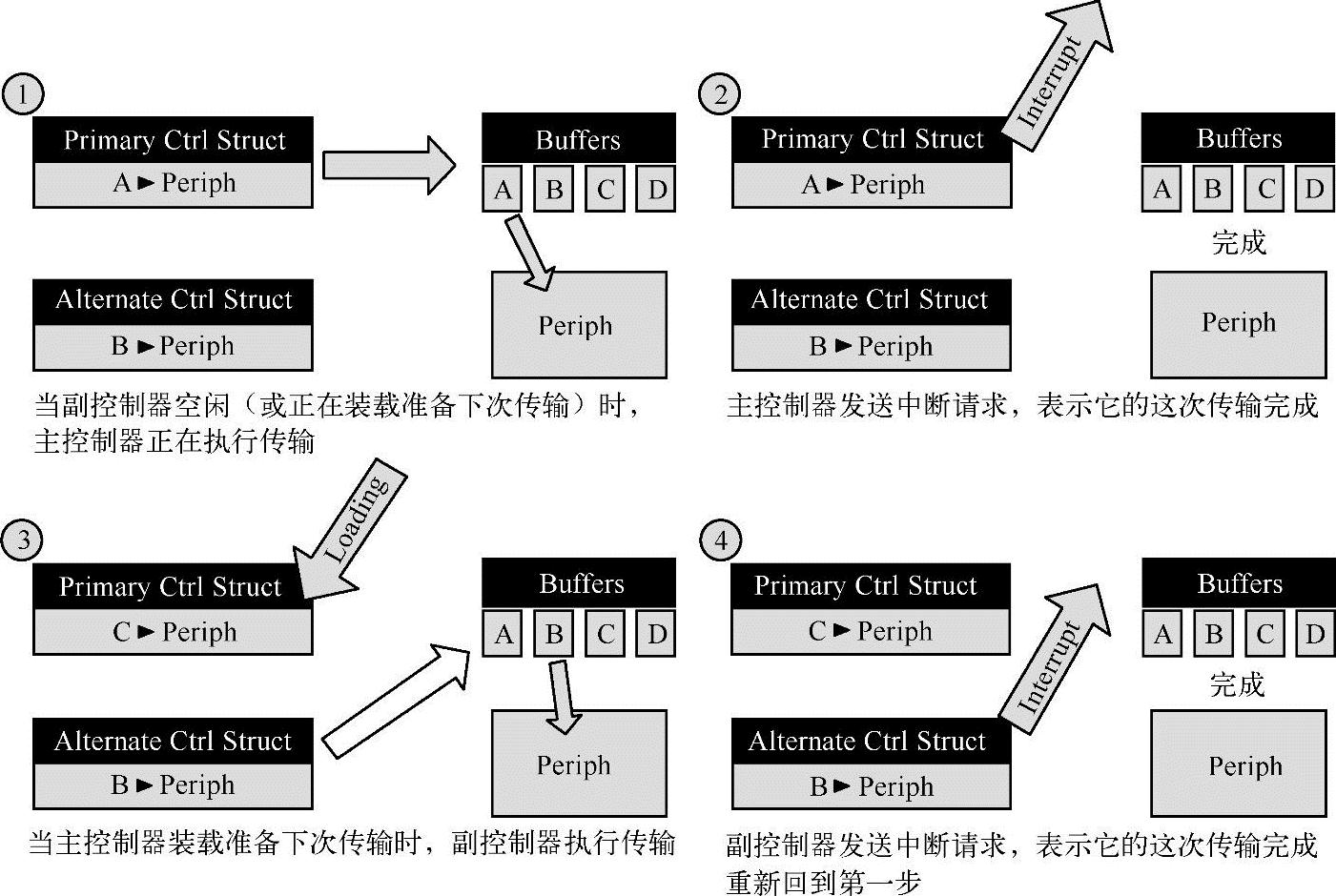

该模式用于两个缓冲器之间的数据传输,当填充每个缓冲区时,可从一个缓冲区切换到另一个缓冲区。虽然这种模式可确保外设之间收发连续的数据流,但需要对中断处理器中作更复杂的设置,并使用处理程序来管理这种所谓的乒乓缓冲器。一个该类型的示例如图13-2所示。

图13-2 乒乓式μDMA数据会话示例

(5)存储器散聚模式

为μDMA控制器提供建立传输“任务”列表方法的一种复杂模式。数据块可以在存储器中的任意存储单元进行双向传输,存储器散聚模式是一种较为复杂的工作模式。通常在搬运数据块时,源数据和目标数据都是按线性分布的;然而有时必须将这些在内存中连续分布的数据分散传递到若干个不同的存储区域,或将内存中几个不同存放单元的数据块汇聚传递到同一个存储区域连续存放,此时就应当采用散聚模式。

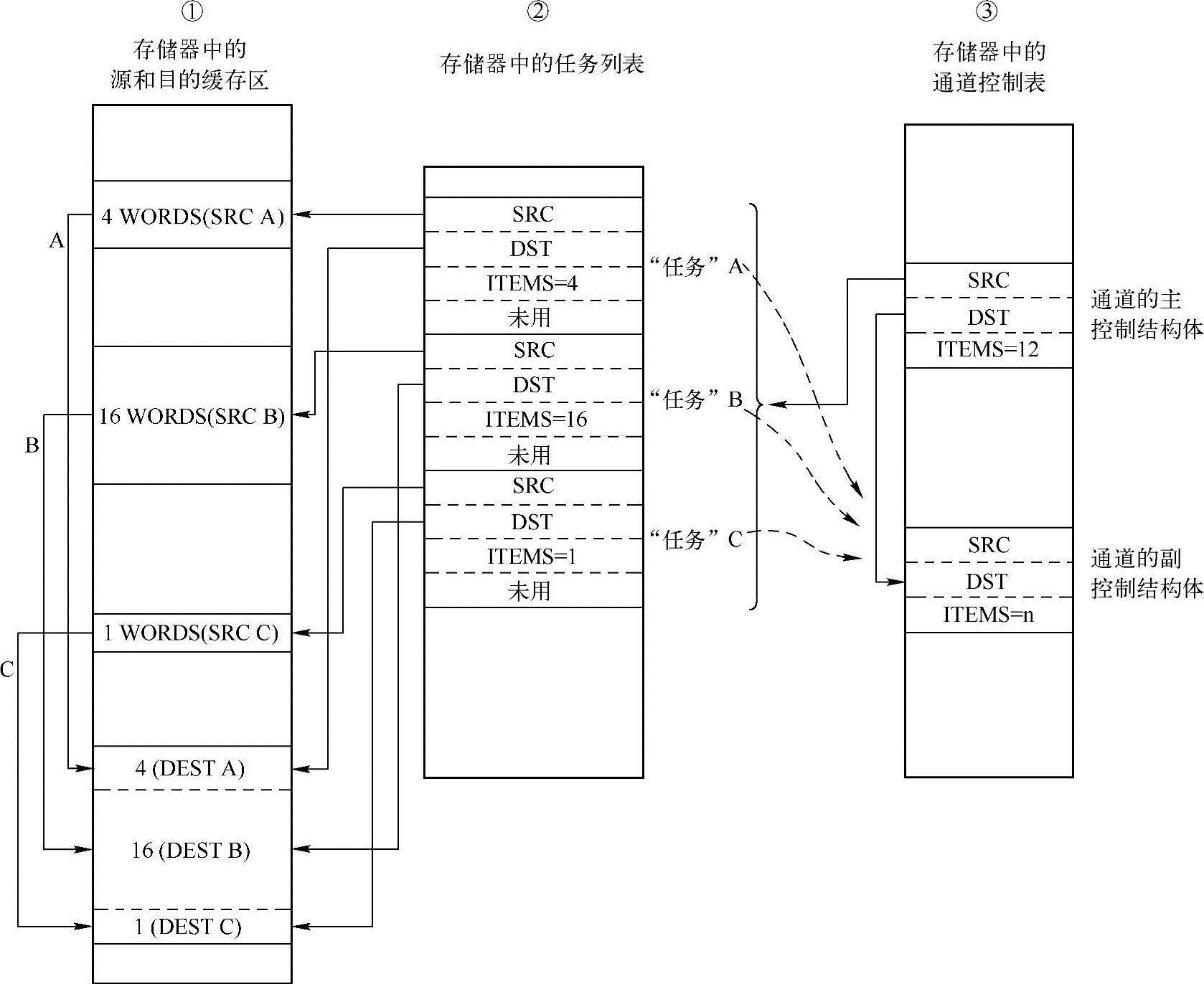

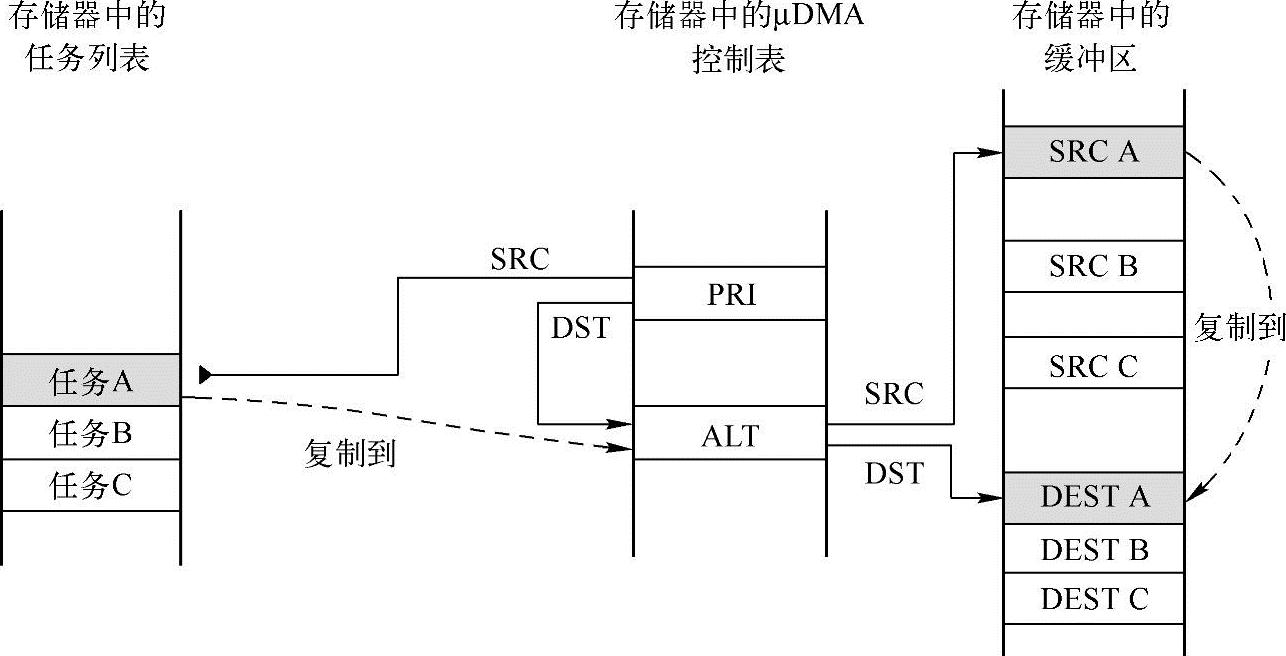

在存储器散聚模式下,主控制结构体是按内存中一个表的内容来配置副控制结构体的。该表由处理器软件创建,包含若干个控制结构体,每个控制结构体中又包含可实现特定传输的源末端指针、目的末端指针、控制字。在每个控制结构体的控制字中必须将传输模式设置为散聚模式。主传输流程依次将表中的控制结构体复制到副控制结构体中,然后执行。μDMA控制器就这样交替切换,即每次用主控制结构体从列表中将下一个待传输的流程配置复制到副控制结构体中,再切换到副控制结构体去执行相应的传输任务。在列表的最末一个控制结构体中,应将其控制字编程为自动传输模式。因此当执行到最后一个传输过程时为自动模式,μDMA控制器在操作完成后将停止该通道的运行。仅当最后一次传输过程也结束时,才会发出结束中断。若将控制表最后一个控制结构体重新指向列表的起始位置(或指向一个新的列表),将使整个列表处于循环状态。

可从如图13-3、图13-4所示的例子中看到存储器散聚模式的工作过程。

在图13-4中,使用通道的主控制结构体,μDMA将任务A的配置复制到通道的副控制结构体中,然后μDMA再将数据从源缓冲区A复制到目标缓冲区中。(仅以任务A为例,任务B与C工作过程相同)

7.传输个数及增量

μDMA控制器所支持的传输数据宽度为8位、16位或32位,对于任何传输,都必须保证源数据与目标数据的宽度相同。源地址与目标地址可以按字节、半字或字自动递增,也可设置为非自动递增。源地址增量与目标地址增量无关联,其设置仅要求保证其大于等于数据宽度即可。

图13-3 存储器散聚模式(创建及配置)

注:

1.应用程序需要将存储器中三个不同存储单元的若干个项目复制到一个缓冲区中并顺序组合。

2.应用程序在存储器中建立μDMA“任务列表”,表中包括3个μDMA控制“任务”指针与控制配置。

3.应用程序设置通道的主控制结构体,将任务逐个复制到副控制结构体中,然后由μDMA控制器执行。

图13-4 存储器散聚模式(μDMA复制序列)

8.外设接口

如果某个外设支持μDMA功能,则在它准备好数据传输时,可发出一个单次请求信号和/或一个突发请求信号。请求信号可通过DMA通道请求屏蔽置位寄存器(DMAREQMASKSET)使能,并通过DMA通道请求屏蔽清零位寄存器(DMAREQMASKCLR)来禁止。若某个通道的请求屏蔽位置位,则禁止该通道的μDMA请求信号。若μDMA通道已被正确配置和使能,则当外设发出请求信号时,μDMA控制器将启动传输过程。当μDMA传输结束时,μDMA控制器将会发出一个中断。注意:当使用μDMA与外设进行数据传输时,外设必须禁止所有NVIC中的中断。

9.软件请求

在32个μDMA通道中有一个专门用于软件启动的传输通道。当该通道μDMA传输完成时,有专用的中断予以指示。要正确使用软件启动的μDMA传输,应先行配置与使能传输过程,然后通过DMA通道软件请求寄存器(DMASWREQ)发出软件请求。注意,基于软件的μDMA传输应当采用自动传输模式。

通过DMASWREQ寄存器也可以启动任意通道的μDMA传输。若在某个外设的μDMA通道上使用软件启动请求,在传输完成时,结束中断将在该外设的中断向量处发生,而不是软件中断向量。只要某个外设不用μDMA做数据传输,则任何外设通道都可用作软件传输请求。

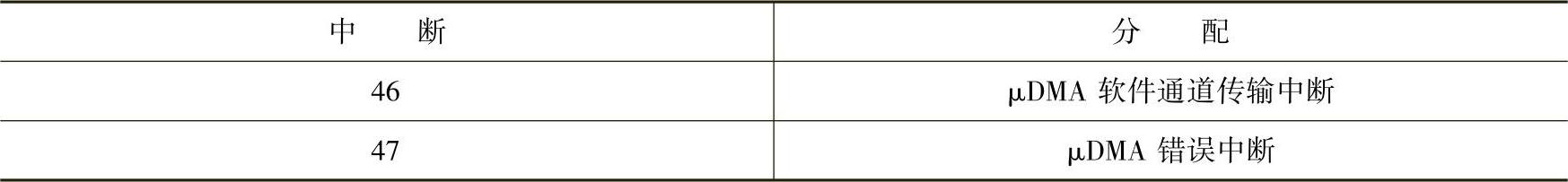

10.中断与错误

当某个μDMA传输过程结束时,μDMA控制器将在相应外设的中断向量处发出一个结束中断。因此,若某个外设使用μDMA传输数据时,并且使能了该外设的中断,则在中断处理函数中必须包含对μDMA传输结束时的中断处理。如果传输过程使用了软件μDMA通道,则结束中断将在专用软件μDMA中断向量上产生(见表13-5)。

表13-5 μDMA中断分配

当使能某外设的μDMA后,μDMA控制器将禁止该外设的普通传输中断传递到中断控制器中,但该中断的状态仍可在外设的中断寄存器中查询到。因此,当使用μDMA传输大量数据时,中断控制器并不会跟随数据流从外设频繁地接收中断,而是仅在数据传输结束时才会收到一个中断。注意,未屏蔽的外设错误中断仍会发送到中断控制器中。

当μDMA通道发出一个完成中断时,在DMA通道中断状态寄存器(DMACHIS)中对应该通道的CHIS位将置位。外设中断处理代码也可通过该寄存器来确定中断是由μDMA通道产生的,还是由外设中断寄存器上报的出错事件造成的。当中断处理程序激活后,μDMA控制器所产生的结束中断请求将会自动清除。

若μDMA控制器在尝试进行数据传输时遇到了总线或存储器保护错误时,将会自动关闭出错的μDMA通道,并在μDMA错误中断向量处发生中断。处理器可通过读取DMA总线错误清除寄存器(DMAERRCLR)来确定是否产生了错误中断。一旦产生错误则ERRCLR标志位将置位,可向ERRCLR位写1来清除错误状态。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。