1.时钟配置

PWM具有两个可选择的时钟源:

①系统时钟。

②预分频系统时钟。

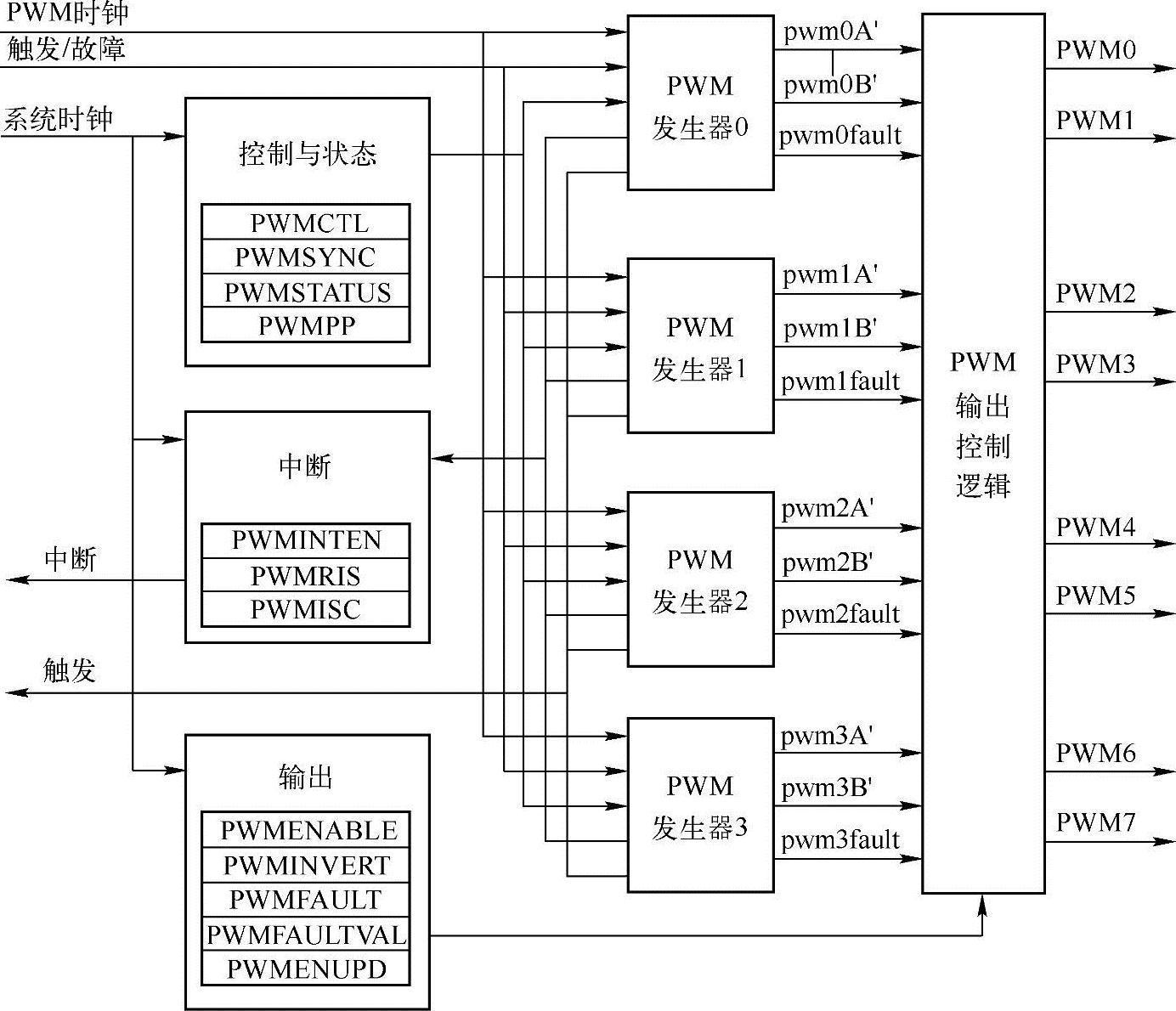

图12-1 PWM模块框图

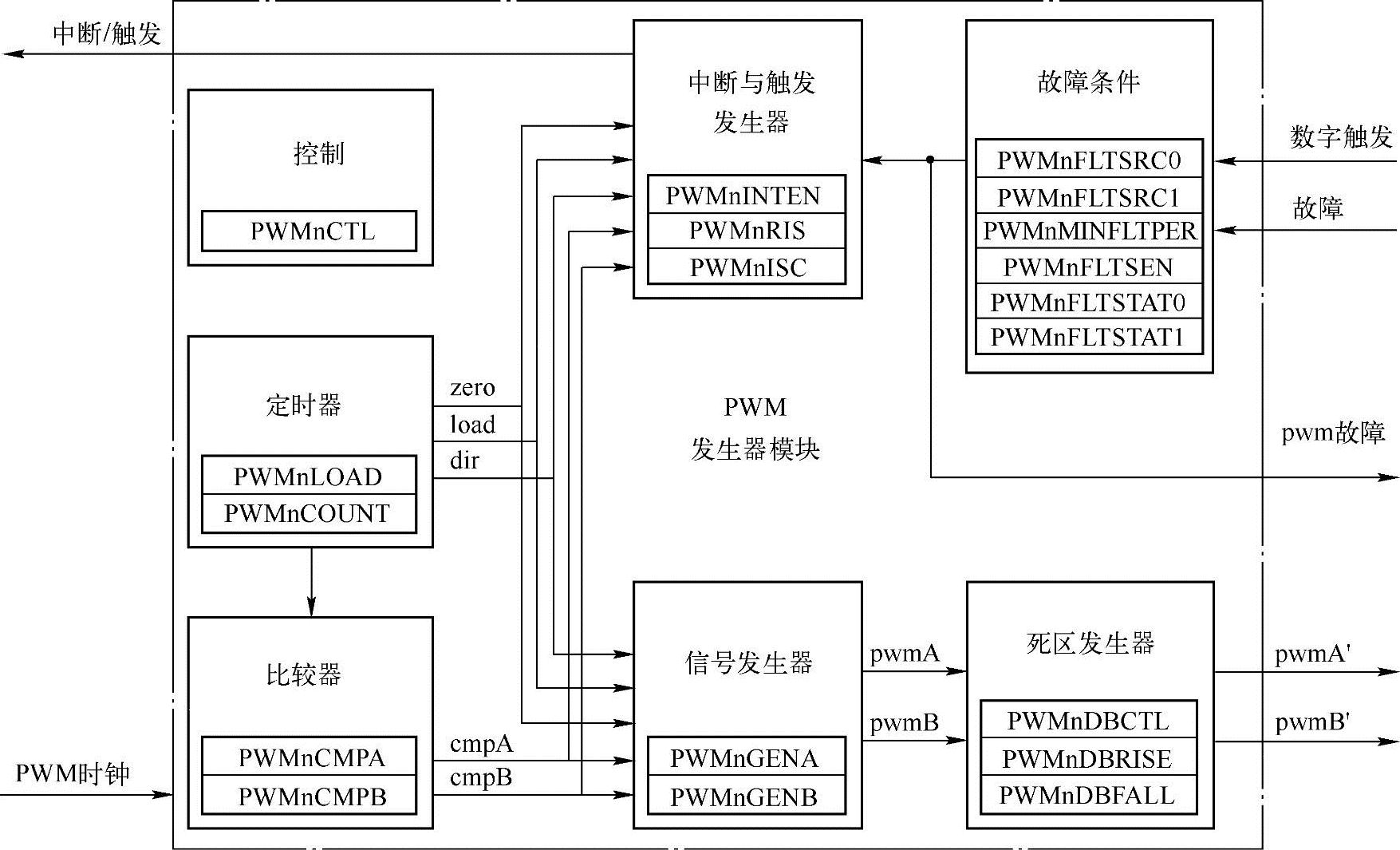

图12-2 PWM发生器模块框图

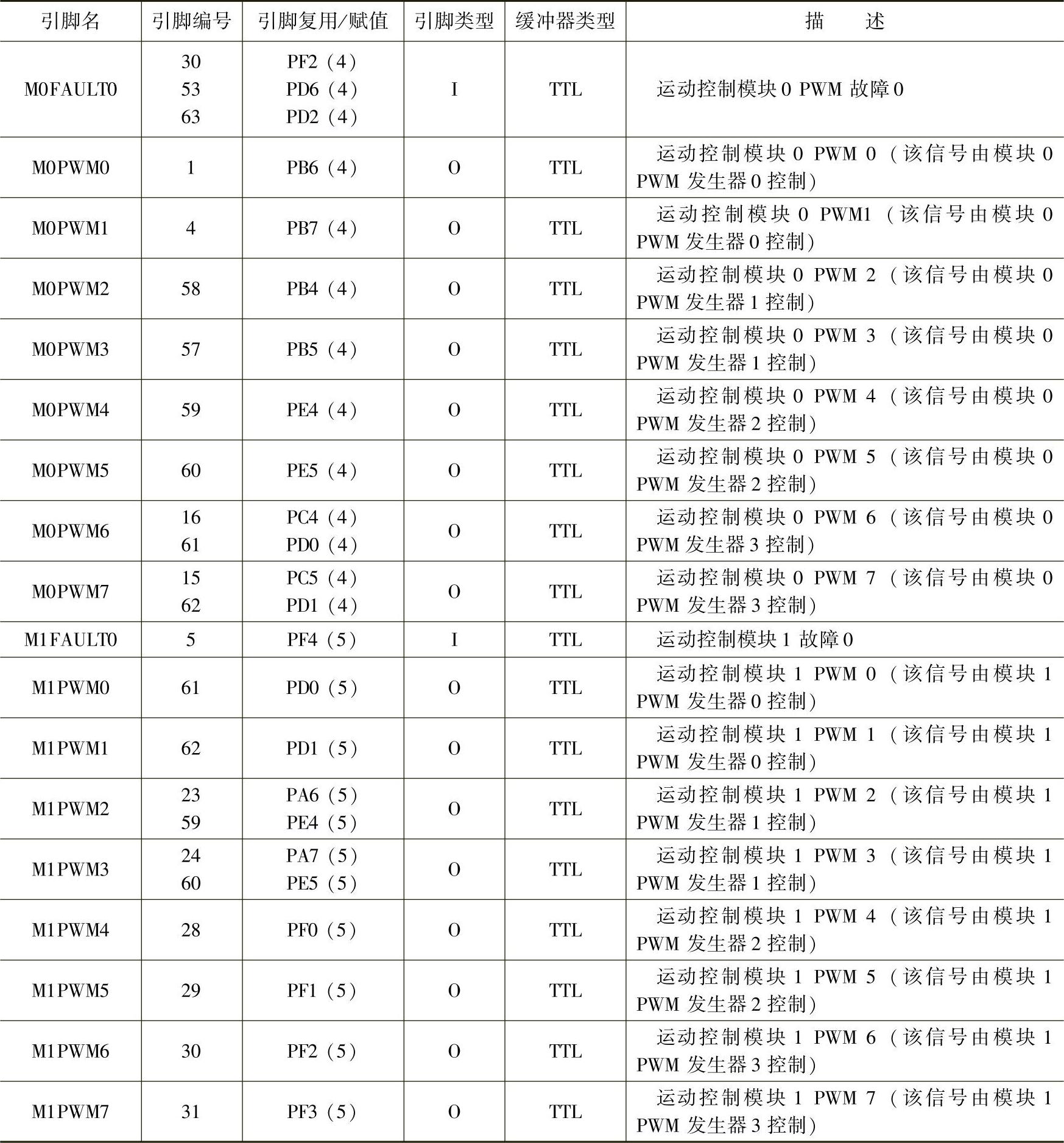

表12-1 PWM信号(64LQFP)

2.PWM定时器

每个PWM发生器中的定时器要么运行在递减模式,要么运行在先递增后递减模式。在递减模式中,定时器从装载值开始递减计数到零,然后返回到装载值,再递减计数。在先递增后递减模式中,定时器从零开始计数至装载值,然后递减到0,再递增到装载值,循环往复。递减计数模式用于产生左或右对齐的PWM信号,而先递增后递减模式用于产生中心对齐的PWM信号。

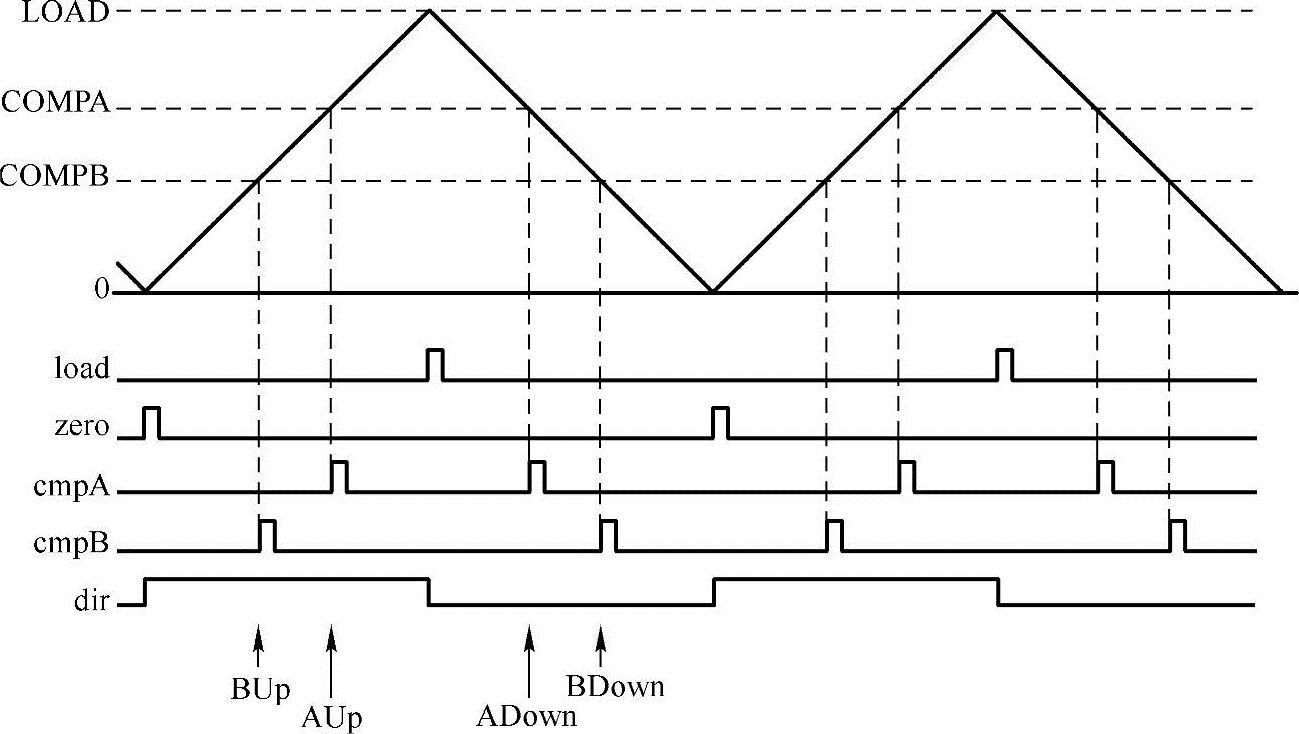

定时器输出PWM生成过程中所使用的三个信号如下:

①"dir"(方向信号)。在递减计数模式中始终为低,而在先递增后递减模式中,其电平在低、高之间切换。

②"zero"(零脉冲信号)。当计数器的计数值为零时,零脉冲信号将产生一个单时钟周期宽的高电平脉冲。

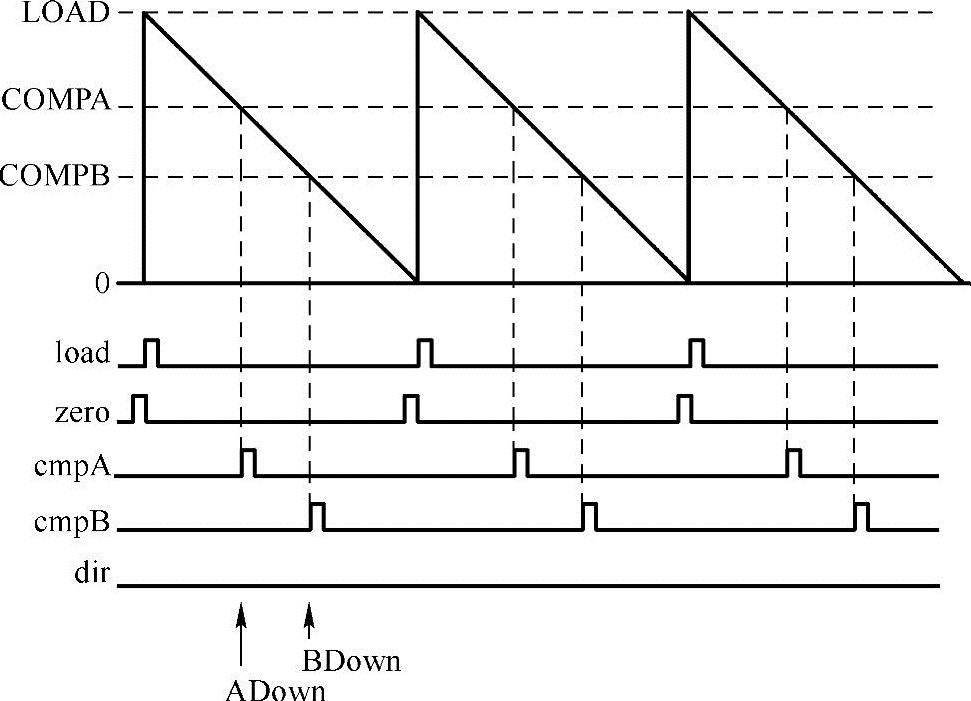

③"load"(装载脉冲)。当计数器的计数值等于装载值时,装载脉冲将产生一个单时钟周期宽高电平脉冲。(如图12-3、图12-4所示)。

注意:在递减计数模式中,零脉冲后面紧跟着装载脉冲。

3.PWM比较器

每个PWM发生器都有两个比较器,用于监控计数器的值;当比较器的值与计数器的值匹配时,比较器输出宽度为单时钟周期的高电平脉冲,即比较器输出一个宽度等于时钟周期的高电平脉冲,如图12-3和图12-4中“cmpA”与“cmpB”信号。在先递增后递减计数模式中,比较器在递增和递减计数时都需进行比较,因此必须采用计数器的方向信号来限定。这些限定脉冲将在产生PWM信号期间使用。如果比较器的值大于计数器的装载值,那么这个比较器将永远不会输出高电平脉冲,图12-3显示了在递减计数模式时的行为和这些脉冲的关系。图12-4给出了在先递增后递减计数模式下计数器的行为和这些脉冲之间的关系。

图12-3 递减计数模式

图12-4 先递增后递减计数模式

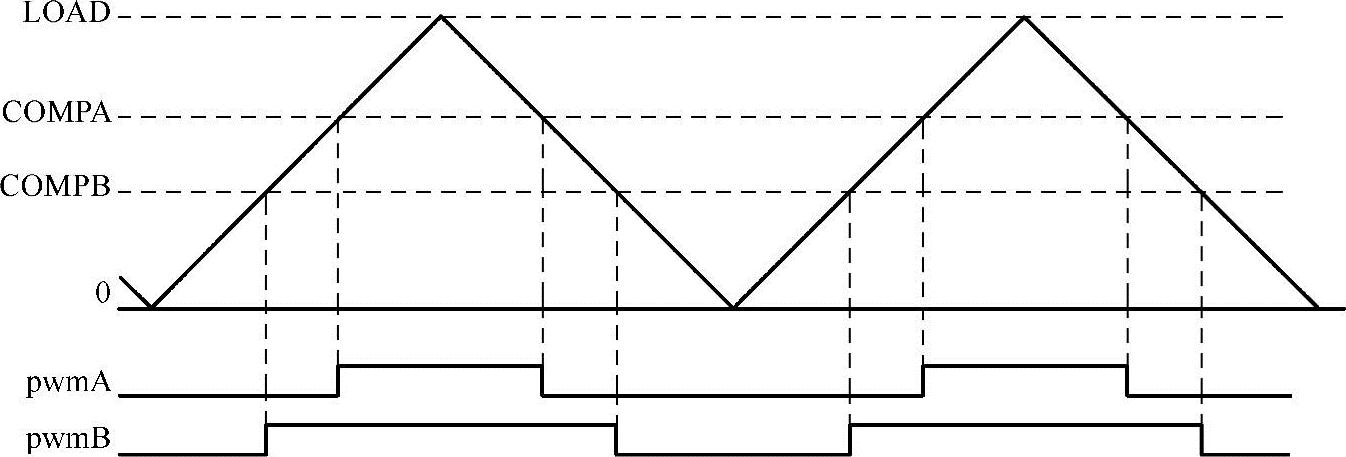

4.PWM信号发生器

PWM发生器捕获load、zero、cmpA和cmpB脉冲(由方向信号限定),产生两个PWM信号(pwmA和pwmB)。在递减计数模式中,有4个事件可影响PWM信号:零、装载、匹配A递减、匹配B递减。在先递增后递减计数模式中,有6个事件可影响PWM信号:零、装载、匹配A递减、匹配A递增、匹配B递减、匹配B递增。当匹配A或匹配B事件与零或装载事件一致时,它们可被忽略。如果匹配A与匹配B事件相吻合,则第一个信号PWMA仅根据匹配A事件产生,第二个信号pwmB仅根据匹配B事件产生。

每个影响PWM输出信号的事件都是可编程的:可被保留(忽略该事件)、可被翻转、可被驱动为低/高电平。这些操作可用于产生一对不同位置和占空比的PWM信号,且该对信号既可重叠也可不重叠。图12-5给出了在先递增后递减计数模式下产生的一对中心对齐、含有不同占空比的重叠PWM信号。

图12-5 先递增后递减模式PWM信号发生图例

从图12-5中可以看到,第一个PWM发生器被设置为当发生匹配A递增事件时将其驱动为高电平,发生匹配A递减事件时使其为低电平,并忽略其他4个事件。第二个发生器被设置为当发生匹配B递增事件时将其驱动为高电平,发生匹配B递减事件时使其为低电平,并忽略其他4个事件。通过改变比较器A的值可改变pwmA信号的占空比,同样改变比较器B的值也可改变pwmB信号的占空比。(https://www.xing528.com)

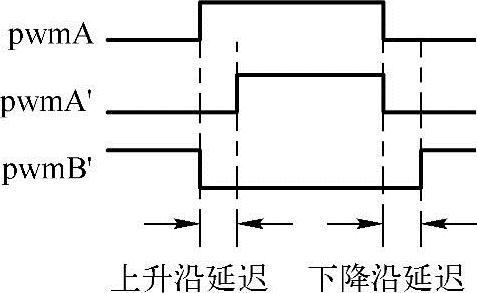

5.死区发生器

PWM发生器产生pwmA和pwmB两个PWM信号并传递给死区发生器。若禁止死区发生器,则PWM信号只简单地通过该模块得到pwmA′和pwmB′,而不会发生改变。如果使能死区发生器,将会丢弃pwmB信号,仅在pwmA信号基础上产生两个PWM信号。第一个输出PWM信号(pwmA′)为pwmA上升沿延迟可编程的信号。第二个输出PWM信号(pwmB′)与pwmA信号反相,为带延迟时间可编程的下降沿延迟信号如图12-6所示。

6.中断/ADC-触发选择器

每个PWM发生器捕获相同的4个(或6个)计数器事件来产生中断或ADC触发事件。可选择这些事件中的任一个或一组作为中断源,只要所选定的事件其中一个发生时都将产生中断。此外,也可选择相同事件、不同事件、一组相同事件、一组不同事件作为ADC的触发源,当这些选定的任何事件发生时同样会产生ADC触发脉冲。选择的事件允许在pwmA或pwmB信号内的特定位置产生中断或触发ADC转换。

图12-6 PWM死区发生器

7.同步方法

常用的PWM操作如下:

①异步:PWM发生器和它的两个输出信号可单独使用,且独立于其他PWM发生器。

②同步:PWM发生器和它的两个输出信号共享统一的时基与其他PWM发生器连接。如果多个PWM发生器都配置成了相同的计数器装载值,则同步可保证其也具有相同的计数值。有了这个特性,就可产生两个以上的PWMn信号,使这些信号的边沿之间包含某些已知的关系,并且模块中的其他状态也提供了一种维持共享时基和相互同步的机制。

若向PWM时间基准同步寄存器(PWMSYNC)中写入数据,可将PWM发生器中的计数器复位,以及将发生器相关的SYNCn位置位。并可在一次访问中置位所有需要的SYNCn位以同步多个PWM发生器。例如,若将PWMSYNC寄存器中的SYNC0和SYNC1位置1就可使PWM发生器0和PWM发生器1中的计数器同时复位。

8.故障状态

故障状态时必须向控制器发出停止正常PWM功能的信号,并置位MnPWMn信号到安全状态。两种基本情况将会引发故障状态:

①微控制器被中止且在运动控制中不能及时执行必要的计算。

②检测到外部错误或事件。

每个PWM发生器可用下面的输入来产生故障状态:

①MnFAULTn引脚有效。

②由调试器引发的控制器中止。

③ADC数字比较器的触发。

故障状态的计算是以PWM发生器为基础的。每个PWM发生器需配置必要的条件来指示已存在的故障状态,允许开发程序可独立和从属的控制。

2个故障输入引脚(MnFAULTn)可供选择。这些输入可用于和产生高/低电平有效的电路一起来指示一个错误状态。MnFAULTn引脚可使用PWMnFLTSEN寄存器单独编程来得到适当的逻辑意义。

PWM发生器的控制模式,包括故障状态处理,将在PWMnCTL寄存器中给出。该寄存器决定是输入信号还是MnFAULTn输入信号的组合,和/或使用数字比较器触发来产生一个故障状态。PWMnCTL寄存器也可以选择故障状态是维持与外界状态一样长,还是被锁存直到由软件清除故障状态为止。最后,这个寄存器也使能一个可用于扩展故障状态周期的计数器,以确保外部事件持续时间最短。该最小故障周期计数在PWMnMINFLTPER寄存器中指定。

PWMnFLTSTAT0和PWMnFLTSTAT1寄存器提供了与具体故障原因相关的状态。PWMINTEN寄存器可用于将PWM发生器故障状态提升为控制器中断。

9.输出控制块

在pwmA′与pwmB′作为MnPWMn信号到达引脚之前,输出控制块将负责对其进行最后的调整。通过PWM输出使能寄存器(PWMENABLE),可对实际到达引脚上的一组PWM信号进行修改。例如,此功能可用于执行单个寄存器的写操作来实现跟无刷直流电动机的通信(无需修改各个PWM发生器,只需对反馈控制回路的进行修改)。此外,通过PWM更新使能寄存器(PWMENUPD),可对PWMENABLE寄存器中的位更新进行配置来立即、局部,或全局同步到下一个同步更新。

故障状态期间,PWM输出信号MnPWMn,通常必须被驱动为安全值,使外部设备可以安全地控制。PWMFAULT寄存器指定在故障状态下是否继续驱动已产生的信号或在PWM-FAULTVAL寄存器中一个指定的编码。

每路PWM信号都有可配置的输出反向控制。即通过PWM输出反相寄存器(PWMINVE-RT)可使任何MnPWMn信号反相,使其从默认的高电平有效变成低电平有效。即使某值在PWMFAULT寄存器中使能并在PWMFAULTVAL寄存器中指定,仍可反相。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。