本小节将介绍SRAM、ROM、闪存和EEPROM存储器的功能。

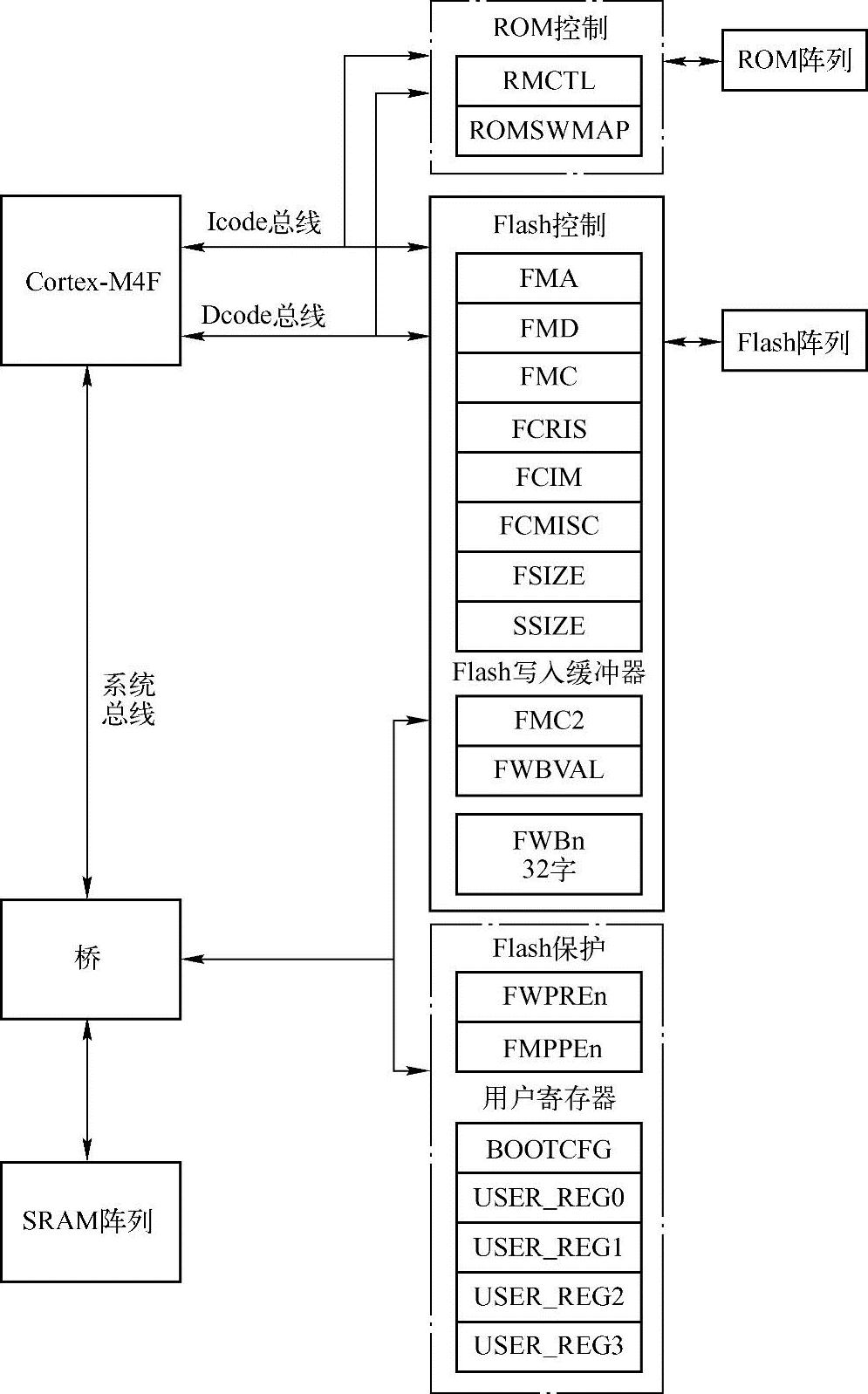

注意:μDMA控制器可以传送和接收片上SRAM中的数据。由于闪存和ROM位于单独的内部总线,μDMA控制器不能从闪存或ROM来传送数据。

1.SRAM

TM4C123GH6PM器件的内部SRAM位于器件存储器映射的地址为0x2000.0000。为了减少耗费在读-修改-写中的操作时间,ARM处理器提供了位带(bit-banding)技术。在已使能位带的处理器中,存储器映射中的某些区域(SRAM和外设空间)能够使用地址别名,在单个原子操作中单独访问各个位。位带的基地址为0x2200.0000。

计算位带别名的公式为

位带别名=位带基地址+(字节偏移量×32)+(位编号×4)

例如,如果欲修改地址0x2000.1000的第3位,则位带别名的计算为

0x2200.0000+(0x1000×32)+(3×4)=0x2202.000C

由计算出的位带别名,对地址0x2202.000C执行的读/写指令可仅直接操作地址0x2000.1000字节的第3位即可。

图10-1 内部存储器模块框图与控制逻辑

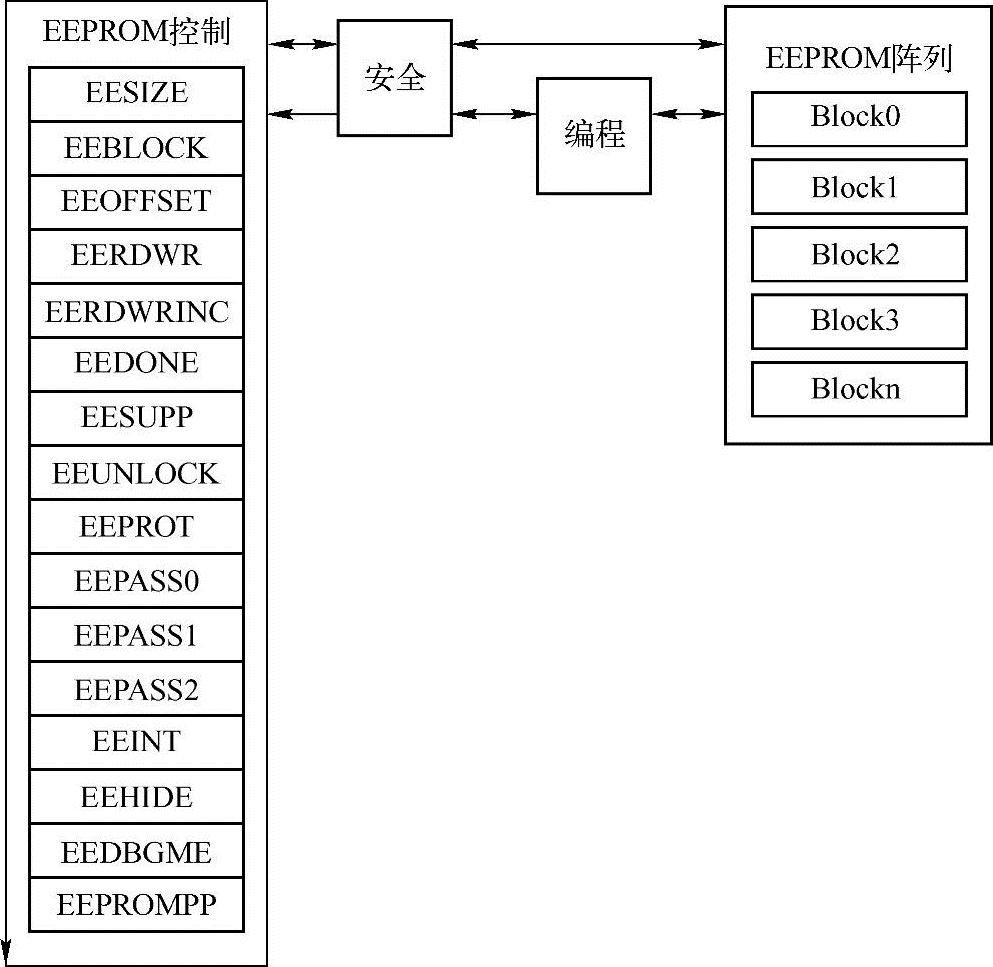

图10-2 EEPROM的模块框图和控制逻辑

2.ROM

TM4C123GH6PM器件的内部ROM位于器件存储器映射地址0x0100.0000处。

ROM包含以下组件:

①TivaWare引导加载程序和向量表。

②TivaWare外设驱动程序库(DriverLib)。

③高级加密标准(AES)密码表。

④循环冗余校验(CRC)错误检测功能。

引导加载程序是用来作为初始化程序的加载器(Flash为空时),以及初始化应用程序固件的更新机制(通过回调引导加载程序)。应用程序可以调用ROM中的外设驱动函数库(API)来降低闪存操作的要求,并释放Flash存储器空间,以便实现其他用途(例如,应用程序中的附加功能)。高级加密标准(AES)是美国政府使用的一种公开定义的加密标准。循环冗余校验(CRC)为验证技术,用于判断一个数据块的内容是否与先前检验相同。

(1)引导加载程序概述

TivaWare引导加载程序用来将代码下载到闪存设备,而不使用调试接口。当内核复位时,通过使能配置寄存器(BOOTCFG)中的A~H任意端口的GPIO信号,使用户有机会让内核直接执行ROM中的引导加载程序或闪存中的应用程序。

在复位时,将按以下顺序进行:

①读BOOTCFG寄存器。若EN位被清零,将执行ROM中的引导加载程序。

②在ROM的引导加载程序中,将指定的GPIO引脚状态与指定的极性进行比较。如果引脚状态符合指定的极性,则ROM将映射到地址0x0000.0000,并继续执行ROM的引导加载程序。

③若EN位被置位或引脚状态不符合指定的极性,数据将从地址0x0000.0004读取,如果在这个地址的数据是0xFFFF.FFFF,则ROM将映射到地址0x0000.0000,并继续执行ROM的引导加载程序。

④如果在地址0x0000.0004的数据值不是0xFFFF.FFFF,堆栈指针(SP)将从闪存的地址0x0000.0000处加载,而程序计数器(PC)则从地址0x0000.0004处装载。然后用户应用程序开始执行。

引导加载程序使用一个简单的包接口与设备进行同步通信。引导加载程序的速度由内部振荡器(PIOSC)的频率决定,因为它不会使能PLL。其可用于以下的串行接口:

①UART0。

②SSI0。

③I2C0。

④USB。

这里UART0、SSI0、I2C0接口使用相同的数据格式和通信协议。

注意:引导装载程序的Flash存储器驻留版本也支持CAN。

(2)TivaWare的外设驱动库

TivaWare外设驱动库包含driverlib/rom.h文件,它帮助调用ROM中的外设驱动库函数。每个函数的详细描述请参考“TM4C123GH6PMROMUser’sGuide”。更多有关调用ROM函数和使用driverlib/rom.h的详细信息,请参考“SW-TM4C-DRL-UG-2.0.1.11577”中的“使用ROM”。当使用不同的Tiva C系列设备时,在ROM中可能有不同的DriverLib函数子集,提供的DriverLib/rom_map.h头文件可增强其移植性。

其他API函数可用于图形和USB功能,但不会预装载到ROM中。TivaWare图形库提供了一组用于基本图形设置和小工具设置,为基于Tiva C系列微控制器具有图形显示功能的开发板创建图形用户界面,详细的信息请参考TI官方文献:SW-TM4C-GRL-UG-2.0.1.11577。TivaWareUSB库是一组数据类型和函数,可用于在装有Tiva C系列微处理器的开发板上创建USB设备、主机或OTG应用,详细的信息请参考TI官方文献:SW-TM4C-USBL-UG-2.0.1.11577。

(3)高级加密标准(AES)密码表

AES是一种强大的加密方法,它在硬件和软件方面都很快速且便于使用,仅需很少的存储空间即可。对于可预先安排密钥的应用程序,采用AES是比较理想的。ROM中提供了执行XySSLAES所需要的四个数据表:

①正向的S-box替换表。

②反向的S-box替换表。

③正向的多项式表。

④反向的多项式表。

(4)循环冗余检验(CRC)错误检测

CRC技术可用来确认接收的信息是否正确,用于确认解压后的数据与验证Flash存储器的内容是否更改,以及其他数据需要被确认的情况。

3.闪存(Flash)存储器

(1)闪存存储器概述

闪存API提供了一组用于处理片上闪存的函数。这些函数用来编程和擦除闪存、配置闪存保护,以及处理闪存中断。

当系统的时钟速度为40MHz或以下时,Flash存储器是单周期读取的。闪存是一系列大小为1KB可被单独擦除块的集合。擦除一个块会使该块的内容重置为全1。这些块可配对成一组可被单独保护的2KB块的集合,且可标记为只读或只执行,并提供不同级别的代码保护。只读块不能被擦除或者编程,以防止这些块的内容被修改。只执行块同样不能被擦除或者编程,并且只能由控制器指令机制读取,以防止这些块的内容被控制器或调试器读取。

(2)预取指缓冲器

闪存控制器有一个预取指缓冲器,当CPU频率大于40MHz时,它会自动开启。在该模式下,闪存将在二分之一系统时钟下工作。每个时钟周期,预取指缓冲器将获取两个32位字,这样在代码线性执行时取指不会处于等待状态。取指缓冲器包含一个分支推断机制,可辨认出分支,从而避免因读取下一对字而增加额外的等待状态。致使短循环分支常常保留在缓冲器中。因此,一些分支可无需等待便可执行,而其他分支需要一个单独的等待状态。

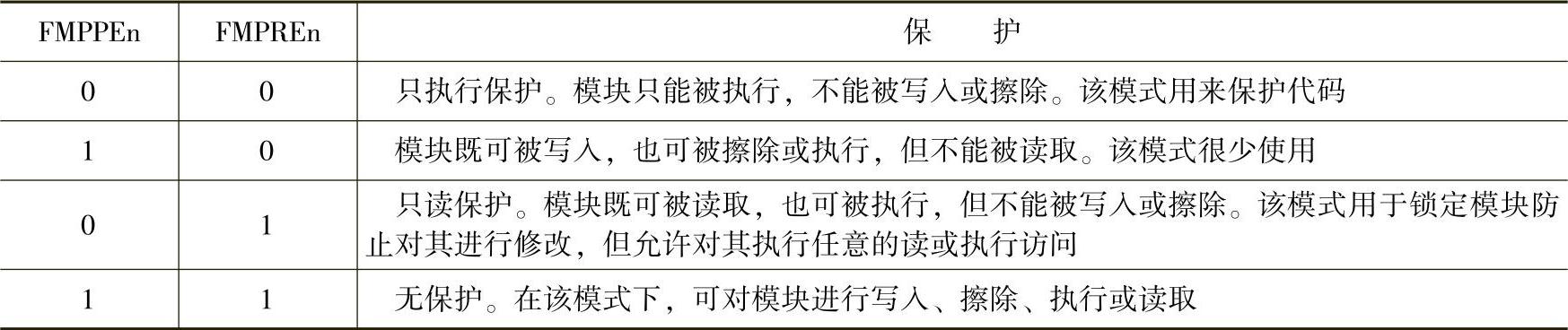

(3)闪存存储器保护

用户可以在四对32位宽存储器中使用两种闪存存储器保护形式,以2KB闪存存储器块为单位。FMPPEn和FMPREn寄存器的各个位控制各种保护形式的策略(每个块控制一种策略)。

①闪存存储器保护编程使能寄存器(FMPPEn):若某个位被置位,就可对相应的块进行编程(写入)或擦除。如果某个位被清零,则不能修改相应的块。

②闪存存储器保护读取使能寄存器(FMPREn):若某个位被置位,则软件或调试器就可对相应的块执行或读取。如果某个位被清零,则相应的块只能被执行,块的内容禁止被作为数据读取。

闪存存储器的保护模式见表10-1。

表10-1 闪存存储器的保护模式

(4)闪存编程

Tiva C设备为闪存编程提供了一个友好的用户接口。所有的擦除/编程操作都通过3个寄存器来处理:闪存地址(FMA)、闪存数据(FMD)和闪存控制(FMC)。(https://www.xing528.com)

注意:如果微控制器的调试功能未被激活而处于“锁死”状态,必须执行一段恢复序列来激活调试模块。请参考TI官方技术文档Tiva TM4C123GH6 PM Microcontroller DATA SHEET中的201页有关恢复锁定微控制器的内容。

在闪存操作(写、页擦除或整体擦除)期间,禁止访问闪存。作为结果,指令和按字取指将延迟到闪存操作完成。如果在闪存操作期间需要执行指令,则代码必须放置在SRAM上,并在SRAM上执行。

(5)中断

闪存控制器在检测到下列状态时会产生中断:

①编程中断。当编程或擦除动作完成时发出的信号。

②访问中断。当对受相应FMPPEn位保护的2KB块存储器尝试编程或擦除操作时发出的信号。

能触发控制器级中断的事件在闪存控制器屏蔽中断状态寄存器(FCMIS)中定义,将相应的MASK位置位可使能该中断。若未使用中断,则原始的中断状态将在闪存控制器原始中断状态寄存器(FCRIS)中可见。

对闪存控制器屏蔽中断的状态和清除寄存器(FCMISC)中相应的位写1将清除相应的中断(适用于FCMIS和FCRIS寄存器)。

(6)基本编程/擦除操作

1)对1个32位字进行编程的步骤:

①将源数据写入FMD寄存器。

②将目标地址写入FMA寄存器。

③将闪存写密钥和WRITE位的值写入到FMC寄存器中。根据BOOTCFG寄存器中KEY位的值,在进行闪存的写操作时,必须将值0xA442或0x71D5写入到WRKEY字段。

④查询FMC寄存器,直到WRITE位清零。

2)执行1KB页擦除的步骤:

①将页地址写入到FMA寄存器中。

②将闪存写密钥和ERASE位的值写入到FMC寄存器中。根据BOOTCFG寄存器中KEY位的值,在进行闪存的写操作时,必须将值0xA442或0x71D5写入到WRKEY字段。

③查询FMC寄存器直到ERASE位清零,或者用FCIM寄存器中的PMASK位使能编程中断。

2)执行整体闪存擦除的步骤:

①将闪存写密钥和MERASE位的值写入到FMC寄存器中。根据BOOTCFG寄存器中KEY位的值,在进行闪存的写操作时,必须将值0xA442或0x71D5写入到WRKEY字段。

②查询FMC寄存器直到MERASE位清零,或者用FCIM寄存器中的PMASK位来使能编程中断。

(7)32个字的闪存写缓存器

32字的写缓冲器提供了同时编程2个32位字的能力,可加快闪存写访问的速度,可在处理16字的同时对32字进行编程,需缓存的数据被写入到写缓冲器寄存器(FWBn)中。

这些寄存器在闪存中是以32字对齐的,则FWB0寄存器对应FMA中的地址(FMA的[6:0]位全为0)。FWB1寄存器对应FMA+0x4中的地址,以此类推。仅在上次缓存的闪存进行写入操作后,更新过的FWBn寄存器方能被写入。闪存写缓冲器有效寄存器(FWB-VAL)显示了从上次缓存闪存写操作后,哪些寄存器已被写入。该寄存器包含的位对应32个FWBn寄存器,其中FWBVAL的第[n]位对应FWBn。若FWBVAL寄存器中的某位被置位,则表明相应的FWBn寄存器已被更新过了。

采用单独被缓冲的闪存写入操作来编程32个字的步骤:

①将源数据写入到FWBn寄存器中。

②将目标地址写入到FMA寄存器中。该地址必须为一个32字对齐的地址(即FMA的[6:0]位为全0)。

③将闪存写入密钥和WRBUF位写入到FMC2寄存器中(即写入0xA442.0001)。

④查询FMC2寄存器,直到WRBUF位清零,或者等待发出PMIS中断信号。

(8)非易失性寄存器编程

下面将讨论如何更新闪存自身的寄存器。这些寄存器存在于主闪存阵列之外的单独空间中,它不受擦除或整体擦除的影响。写操作可将这些寄存器中的位由1变0。除了上电复位会将寄存器的内容复位为0xFFFF.FFFF外,其他复位都不会影响寄存器的值。在上电序列后,可用FMC寄存器中的COMT位来提交确认寄存器的值,之后寄存器的值将变为非易失而保持下去。在寄存器的内容被提交后,能恢复出厂默认值的唯一方法就是执行“恢复一个“锁定的”微控制器”中描述的方法(见TI文档Datasheet-TM4C123GH6PM的201页)。

该驱动包含在driverlib/flash.c中,driverlib/flash.h包含API的定义。

4.EEPROM

(1)EEPROM模块的特点

TM4C123GH6PM微控制器包括1个EEPROM模块,具有以下特点:

①可访问512个32位字的2KB内存。

②32个16字的块(64B)。

③每个2页面块可进行500K~15M次写操作。

④每个块的访问保护。

⑤整个外设的锁定保护选项与每个块的锁定保护相同,使用32~96位的解锁码。

⑥支持写入完成后产生中断,以避免轮询操作。

⑦内置平衡擦写。

(2)功能简述

EEPROM模块提供了一个定义良好的寄存器接口来支持随机读取或写入EEPROM,以及支持轮询或顺序访问EEPROM的机制。

一种保护机制允许锁定EEPROM块,以防止在某些情况下不必要的写入或者读取操作。密码模型允许应用程序锁定一个或多个EEPROM块来控制访问16字边界。

1)锁定和密码。可对EEPROM在模块级和块级进行锁定。由EEPROM的密码寄存器(EEPASSn)中的密码控制,该密码为一个32~96位之间的值,但不可全是1。其中,块0为主块,不仅用它的密码可对控制寄存器与其他的块进行保护,而且也可用块密码对每个块进行进一步的保护。

若块0设有密码,则在复位时整个模块都将被锁定。其锁定规则:在块0解锁以后,将使块1~块31可访问,而块0会继续受自己的保护位保护。任何块(包括块0)设置密码后,都可以根据是否锁定控制块来决定能否被访问。

复位时所有密码保护的块均会被锁定。欲解锁这些块,就必须将正确的密码写入EEP-ROM解锁寄存器(EEUNLOCK)中。写入密码时,应通过EEPASSn寄存器将其写入1~3遍来组成32位、64位或96位的注册密码。在EEUNLOCK寄存器中写入0xFFFF.FFFF可以重新锁定块或模块(0xFFFF.FFFF为无效密码)。

2)保护与访问控制。保护位为每个块提供了单独的读写控制,可实现的保护模式如下:

①没有密码:任何时间都可进行读/写操作,在无密码时,该模式为默认。

②没有密码:可以读取,但不能写入。

③有密码:可读取,只有在密码解锁后方可写入,在有密码时,该模式为默认。

④有密码:在锁定时只能读取,或只能写入。

⑤有密码:在锁定时只读,但不能写入。

另外,访问保护还可以通过处理器模式实现。这种配置允许仅管理员访问,或管理员与用户访问(默认模式)。其中,仅管理员访问模式还可以阻止μDMA与调试器的访问。

同时,主块还可以用来控制保护机制本身的访问保护。若块0的访问控制是仅管理员访问模式,则整个模块都可以用管理员模式访问。并且块0的保护级别为整个EEPROM设置了最低的保护级别。

3)中断控制。EEPROM模块允许在写入完成之后发出中断,而无需轮询。该中断可用于驱动应用程序的ISR,使ISR可写入更多的字或验证操作的完成。无论是由于错误还是成功编程或擦除操作所引起,该中断机制均可在EEDONE寄存器工作或停止时随时使用。EE-PROM中断用闪存中断向量给内核发信号,软件可通过检测闪存控制器屏蔽中断状态和清除寄存器(FCMISC)的第2位来确定中断源是否为EEPROM。

4)工作原理。EEPROM采用EEPROM类型单元的传统闪存块模型操作,但使用扇区擦除。另外,若需要,在复制页中的字时,允许500k+个擦除周期,即每个字均有一个最新版本。这样,写入操作就在新的位置创建了一个新版本的字,使其原先的值被抛弃。

每个扇区包含两个块,每个块包含一个活动副本和六个冗余副本的位置。将密码、保护位和控制数据都保存在页中。当页中保存最新字的空间不足时,就会启用一个复制缓冲区,使其复制每个块中的最新字,并将原来的页擦除,最终将复制缓冲区的内容复制回页中。这种机制可确保掉电时的数据不丢失,即使在操作期间。EEPROM机制也会跟踪所有的状态信息,提供全面的安全性和保护。尽管几率很小,但在某些环境下还是可能发生错误,比如,编程过程中电压过低等。

EEPROM详细的功能描述请参考Datasheet-TM4C123GH6PM的数据手册(见配套资源)。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。