1.数据控制

数据控制寄存器允许软件配置GPIO的操作模式。当数据寄存器捕获到输入数据时,数据方向寄存器将GPIO配置为输入;当数据寄存器通过端口输出数据时,数据方向寄存器将GPIO配置为输出。

(1)数据方向操作

GPIO方向寄存器(GPIODIR)用于将每个独立的引脚配置成输入或输出。当数据方向寄存器中的位被清零时,则配置为输入,使寄存器中的相应位捕获并储存GPIO端口的值;当数据方向寄存器中的位被置位时,则配置为输出,数据寄存器中的相应位便可驱动GPIO端口。

(2)数据寄存器的操作

为了提高软件的效率,可将地址总线上的[9∶2]位用作屏蔽位,对GPIO端口的数据寄存器(GPIODATA)中的各个位进行修改。采用这种方式使软件驱动程序仅用一条指令就可修改任意一个GPIO引脚,而不会影响其他引脚的状态。该方式与通过“读-修改-写”来操作GPIO引脚的传统做法不同。为了实现这种功能,GPIODATA寄存器覆盖了存储器映射中的256个单元。

在进行写入操作时,如果与数据位相关联的地址位被置位,则GPIODATA寄存器的值将相应地发生变化,如果地址位被清零,那么数据位将保持不变。

例如,将0xEB写入到地址GPIODATA+0x98处,其结果如图5-2所示。其中,u表示写入操作没有改变数据。

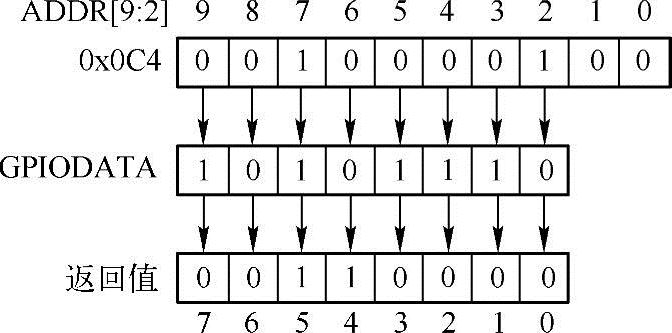

在进行读操作时,如果与数据位相关联的地址位被置位,那么就读取数据寄存器中的值;如果与数据位相关联的地址位被清零,则不管数据寄存器中的实际值是什么都读取0。例如,读取地址GPIODATA+0x0C4处的值,其结果如图5-3所示。

图5-2 GPIODATA写入示例

图5-3 GPIODATA读取示例

2.中断控制

每个GPIO端口的中断能力都由7个寄存器控制。这些寄存器可用于选择中断源、极性与边沿属性。当一个或多个输入产生中断时,只将其中的一个中断输出,发送到供所有GPIO端口使用的中断控制器中。对于边沿触发,为使其他中断可用,软件必须清除该中断;对于电平触发,只有保持外部电平的状态,才能使控制器识别中断的发生。

以下三个寄存器用来定义中断触发的边沿或测量:

①GPIO中断检测寄存器(GPIOIS)。

②GPIO中断双边沿寄存器(GPIOIBE)。(https://www.xing528.com)

③GPIO中断事件寄存器(GPIOIEV)。

通过GPIO中断屏蔽寄存器(GPIOIM)可使能/禁止中断。当产生中断条件时,可在GPIO原始中断状态寄存器(GPIORIS)和GPIO屏蔽后的中断状态寄存器(GPIOMIS)中观察到中断信号的状态。即GPIOMIS寄存器仅显示允许被传送到中断控制器的中断条件。GPIORIS寄存器则表示GPIO引脚满足的中断条件,但不一定发送到控制器中。

注意:往GPIO中断清零寄存器(GPIOICR)中的位写1可以清除相应的中断。在设置中断控制寄存器(GPIOIS、GPIOIBE或GPIOIEV)时,应该保持中断的屏蔽状态(GPIOIM清零),如果相应的位没有屏蔽,那么向中断控制寄存器中写入任何值都有可能产生伪中断。

(1)ADC触发源

任何GPIO引脚都可以使用GPIOADC控制寄存器(GPIOADCCTL)将其配置成ADC的一个外部触发。如果任一GPIO端口被配置成非屏蔽的中断引脚,当该端口产生一个中断时,就会发出一个外部触发信号到ADC。此时如果ADC事件复用选择寄存器(ADCEMUX)被配置为使用外部触发器,那么就会启动ADC转换。

(2)μDMA触发源

任何GPIO引脚都可以使用GPIODMA控制寄存器(GPIODMACTL)配置成μDMA的一个外部触发源。如果任一GPIO端口被配置为非屏蔽的中断引脚,当该端口产生一个中断,就会发出一个外部触发信号到μDMA。如果根据GPIO信号μDMA被配置成启动传输,那么就会启动传输。

3.模式控制

GPIO引脚既可以被软件控制也可以被硬件控制。大部分的引脚默认为软件控制,此时GPIODATA寄存器用来读写相应的引脚。当GPIO复用功能选择寄存器(GPIOAFSEL)使能硬件控制时,引脚状态将由它的复用(即外设)功能控制。

更多的引脚复用功能选择由GPIO端口控制寄存器(GPIOPCTL)提供,该寄存器可为每个GPIO选择其中一个外设功能。注意:如果一个引脚被用作ADC输入,那么GPIOAM-SEL寄存器中相应位必须被置位来禁止模拟隔离电路。

4.提交(Commit)控制

GPIO提交控制寄存器提供的保护层可防止对重要硬件外设的意外编程。该功能可保护4个JTAG/SWD引脚(PC[3:0])与NMI引脚(PD7和PF0)。向GPIO复用功能选择寄存器(GPIOAFSEL)、GPIO上拉电阻选择寄存器(GPIOPUR)、GPIO下拉电阻选择寄存器(GPIOPDR)与GPIO数字使能寄存器(GPIODEN)中受保护的位写入数据将不会被确认保存,除非GPIO锁定寄存器(GPIOLOCK)没有被锁定,同时GPIO提交寄存器(GPIOCR)中的相应位被置位。

5.引脚(Pad)控制

可根据应用程序的要求用软件来配置GPIO引脚。引脚控制寄存器包括GPIODR2R、GPIODR4R、GPIODR8R、GPIOODR、GPIOPUR、GPIOPDR、GPIOSLR与GPIODEN寄存器。这些寄存器控制着引脚的驱动电流大小、开漏配置、上/下拉电阻的选择、转换率(slew-rate)控制和数字输入使能等。如果在配置为开漏输出的GPIO端口上加上5V电压,其输出电压将取决于上拉电阻的大小,而没有配置的GPIO引脚将输出5V电压。

6.标识

复位时配置的标识寄存器允许软件将模块当作GPIO块进行检测和识别。标识寄存器包括GPIOPeriphID0~GPIOPeriphID7寄存器与GPIOPCellID0~GPIOPCellID3寄存器。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。