1.采样序列发生器

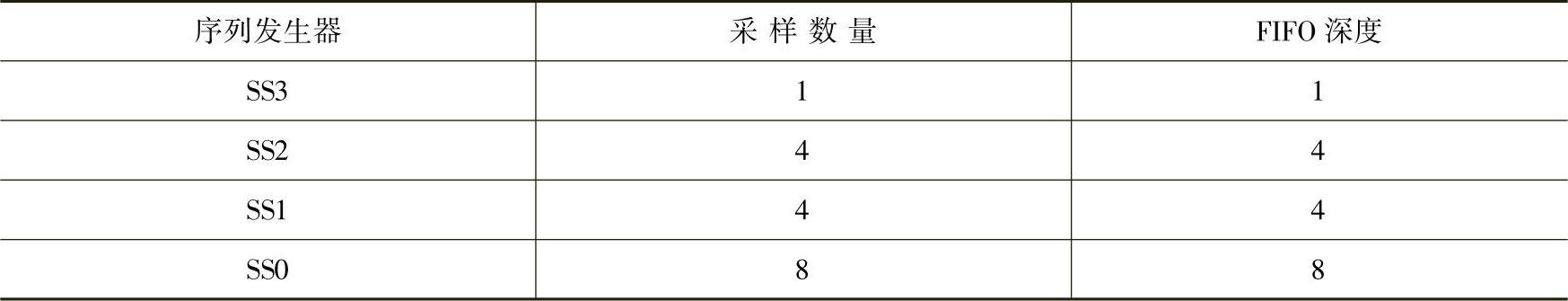

采样控制和数据采集都是由采样序列发生器(Sample Sequencer)处理的。所有序列发生器都是相同的,唯一的差别在于其能够捕获的样本数量与FIFO的深度(见表4-2)。捕捉到的每个采样都要存入FIFO中。在此实现中,每个FIFO入口均为一个32位的字,其低12位包含的是转换结果。

表4-2 序列发生器的采样数和FIFO深度

对于指定的采样序列,若以n代表其序号,则采样序列n中的每个采样动作分别以ADC采样序列输入多路复用器选择寄存器(ADCSSMUXn)与ADC采样序列控制寄存器(ADCSSCTLn)中的1个半字节来定义。该ADCSSMUXn用于选择输入引脚,而ADCSSCTLn包含采样控制位,这些控制位分别与参数(例如,温度传感器的选择、中断使能、序列末端和差分输入模式等)对应。采样序列发生器可以通过置位ADC来激活采样序列发生器寄存器(ADCACTSS)中的相应ASENn位进行使能,且可在使能之前进行配置。软件可通过置位ADC处理器采样序列使能寄存器(ADCPSSI)中的SSn位来使能采样。此外,通过配置ADCPSSI寄存器的GSYNC和SYNCWAIT位可同时使能多个ADC模块的多个采样序列。

2.模块控制

在控制逻辑单元中,除采样序列发生器之外的其余部分将负责执行以下任务:

①产生中断。

②DMA操作。

③采样序列按优先级执行。

④配置触发事件。

⑤配置比较器。

⑥采样相位控制。

⑦模块时钟。

大多数的ADC控制逻辑都是在16MHz的ADC时钟速率下运行的。当系统XTAL选定PLL时,硬件将自动配置内部的ADC分频系数,使之在16MHz频率进行操作。

(1)中断

采样序列发生器和数字比较器的寄存器配置可决定哪些事件会产生原始中断,但对于中断是否真的发送给中断控制器并没有控制权。ADC模块是否产生中断信号是由ADC中断屏蔽寄存器(ADCIM)中的MASK位决定的。中断状态可从两个位置查询:其一,ADC原始中断状态寄存器(ADCRIS)显示各个中断信号的原始状态;其二,ADC中断与清除寄存器(ADCISC)显示经ADCIM寄存器使能后的实际中断状态。通过向ADCISC对应的IN位写1来清除中断。注意,数字比较器中断不是通过本寄存器清除的,而是通过向ADC数字比较器中断状态与清除寄存器(ADCDCISC)的对应位写1来清除的。

(2)DMA操作

如果使用DMA,则每个采样序列发生器都能独立工作,无须微控制器干预或重置就可传输数据来提高效率。每个采样序列发生器均可向μDMA控制器中的相关专用通道发送请求,但ADC不支持单次传输请求。当采样序列的中断标志位置位时(ADCSSCTLn寄存器的IE位置位)将发出突发传输请求。而μDMA传输的仲裁大小必须是2的整数幂,且ADDSSCTLn寄存器的相关IE位必须置位。

(3)优先级

当同时出现多个采样事件(触发条件)时,可按ADC采样序列器优先级寄存器(ADC-SSPRI)所定义的优先级顺序依次执行。优先级的有效值为0~3,其中0代表最高优先级、3代表最低优先级。如果多个激活的采样序列具有相同的优先级,将导致转换结果数据不连续,因此软件必须确保当前激活的所有采样序列各自具有唯一的优先级。

(4)采样事件

每个采样序列发生器的采样触发条件均可通过ADC事件复用选择寄存器(ADCEMU X)来定义。触发事件源包括微控制器触发(默认值)、模拟比较器触发、由GPIOADC控制寄存器(GPIOADCCTL)指定的GPIO外部信号触发、通用定时器触发和连续采样触发。可通过将ADC处理器采样序列使能寄存器(ADCPSSI)中的SSx位置位来使能采样序列。在配置连续采样触发条件时务必慎重,若某个采样序列的优先级过高,可能导致其他低优先级采样序列始终无法运行。一般将使用连续采样模式的采样序列器设置为最低优先级,当输入口上的电压达到某一定值时,连续采样可与数字比较器配合使用来产生中断。

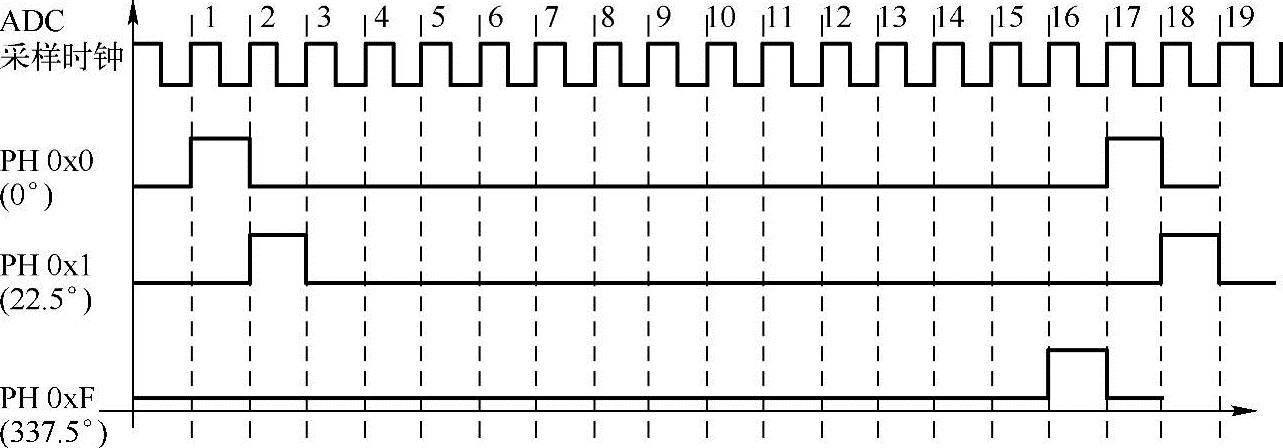

(5)采样相位控制

ADC0和ADC1可单独采用不同的触发源,也可采用相同的触发源;既可单独采用不同的模拟输入端,也可采用同一模拟输入端。若两个转换器以相同的采样率工作,其采样点既可以配置为同相,也可以配置为相互错开一定的相角。采样点延后的相位在0°到337.5°之间以22.5°递增,并通过ADC采样相位控制寄存器(ADCSPC)进行设置,如图4-3所示。

图4-3 采样相位

(6)模块时钟

该模块的16MHz时钟可由PLL分频输出、PIOSC或连接到MOSC的外部时钟源获得。当PLL处于工作状态时,ADC时钟默认值为PLL÷25。而PIOSC可用于使用ADC时钟配置寄存器(ADCCC)的模块时钟。若将PIOSC作为ADC的时钟,首先给PLL上电,然后在ADCCC寄存器中的CS位字段使能PIOSC,最后禁止PLL。当PLL被旁路时,连接到MOSC模块的时钟源必须为16MHz,否则只能将PIOSC作为时钟源。要使用MOSC时钟的ADC,首先给PLL上电,然后使能ADC模块时钟,再后禁用PLL并切换到MOSC系统时钟。如果PIOSC是ADC模块的时钟源,则ADC模块可以继续在深度睡眠模式下运行。

系统时钟必须≥ADC模块的时钟。使所有ADC模块共享相同的时钟源有助于在多个转换设备间同步数据采样。

3.硬件采样平均电路

使能硬件采样平均电路虽可获得更高的精度,但其代价是吞吐率会成比例地降低。硬件采样平均电路最高可将64次采样结果累加并计算出平均值,以平均值作为单次采样的数据写入序列发生器FIFO的1个单元中。由于是算术平均值,则吞吐率与求平均值的采样数目成反比。例如,若取16次采样进行平均值计算,那么吞吐率将降为1/16。

默认硬件采样平均电路是关闭的,转换器捕捉的所有数据将直接传送到序列发生器的FIFO中。进行平均计算的硬件由ADC采样平均控制寄存器(ADCSAC)进行控制。每个ADC模块只有一个平均电路,不论单端输入还是差分输入都将执行相同的求平均值操作。

如图4-4所示给出了一个范例。其中,ADCSAC寄存器设置为0x2以进行4×硬件过采样;IE1被置位以提供采样队列;当第2个平均值储存到FIFO后,会产生中断。

图4-4 硬件采样平均处理

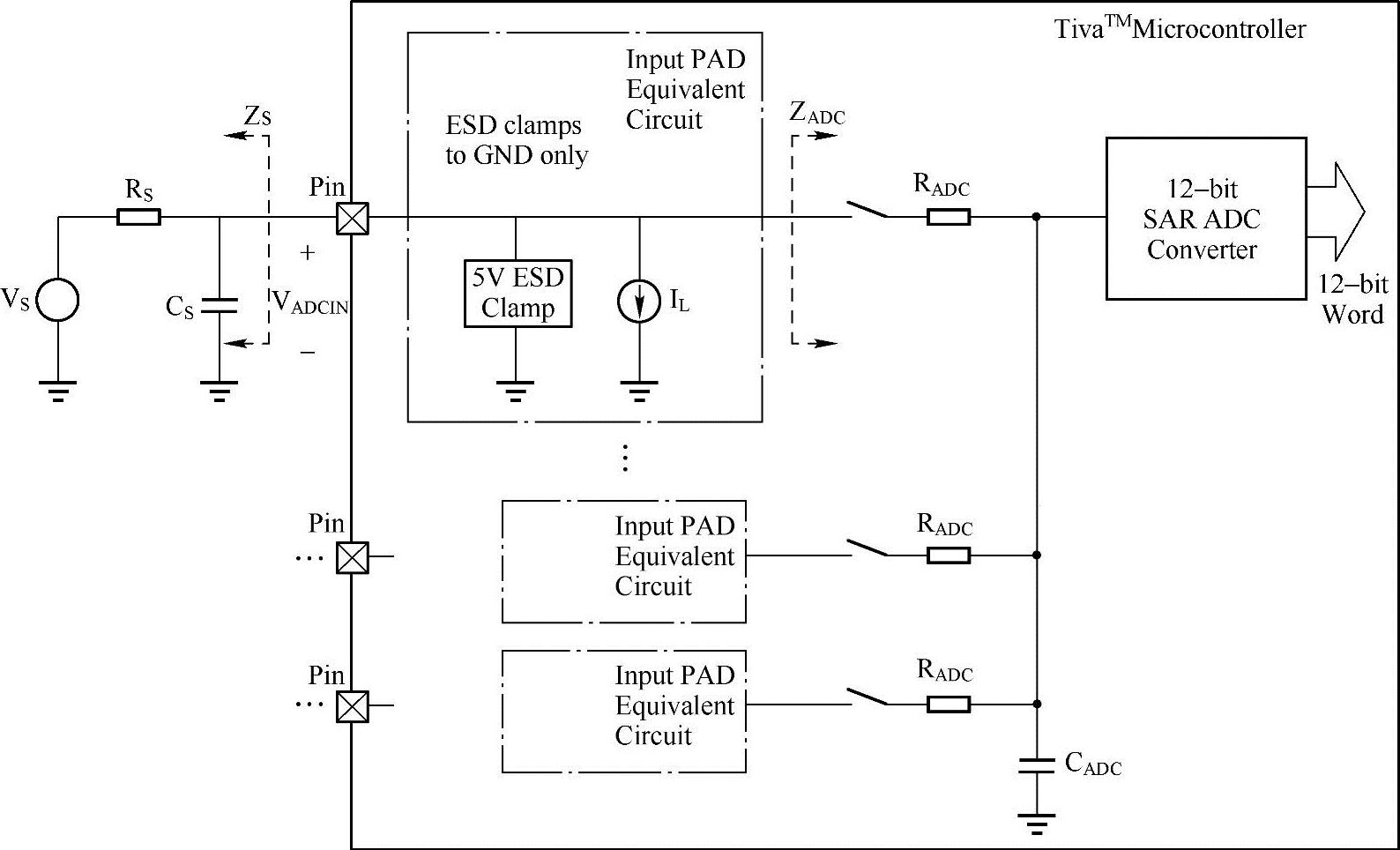

4.模数转换器(https://www.xing528.com)

模数转换器(ADC)模块采用逐次逼近寄存器(Successive Approximation Register(SAR))架构提供一个12位、低功耗、高精度的转换值。逐次逼近使用一个开关电容阵列,以实现采样和保持信号的双重功能,并提供12位的DAC操作。该ADC需要16MHz的时钟,这个时钟可以是PLL输出的分频值、PIOSC或连接到MOSC的一个16MHz时钟源。ADC输入等效电路框图如图4-5所示。

图4-5 ADC输入等效电路框图

ADC模块同时从3.3V模拟电源和1.2V数字电源取电。在不要求ADC转换精度时,可以将ADC时钟配置为低功耗。从自定义引脚上输入的模拟信号通过特殊的平衡输入通道连接到ADC,尽量降低输入信号的失真。

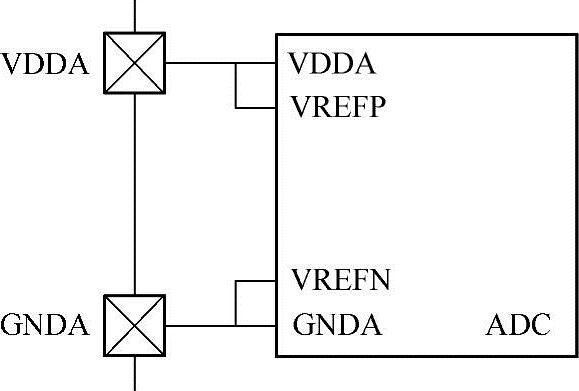

(1)基准电压

ADC使用内部信号VREFP和VREFN作为基准电压以产生一个选定模拟输入的转换值。VREFP、VREFN分别连接到VDDA和GNDA,如图4-6所示。

图4-6 ADC基准电压

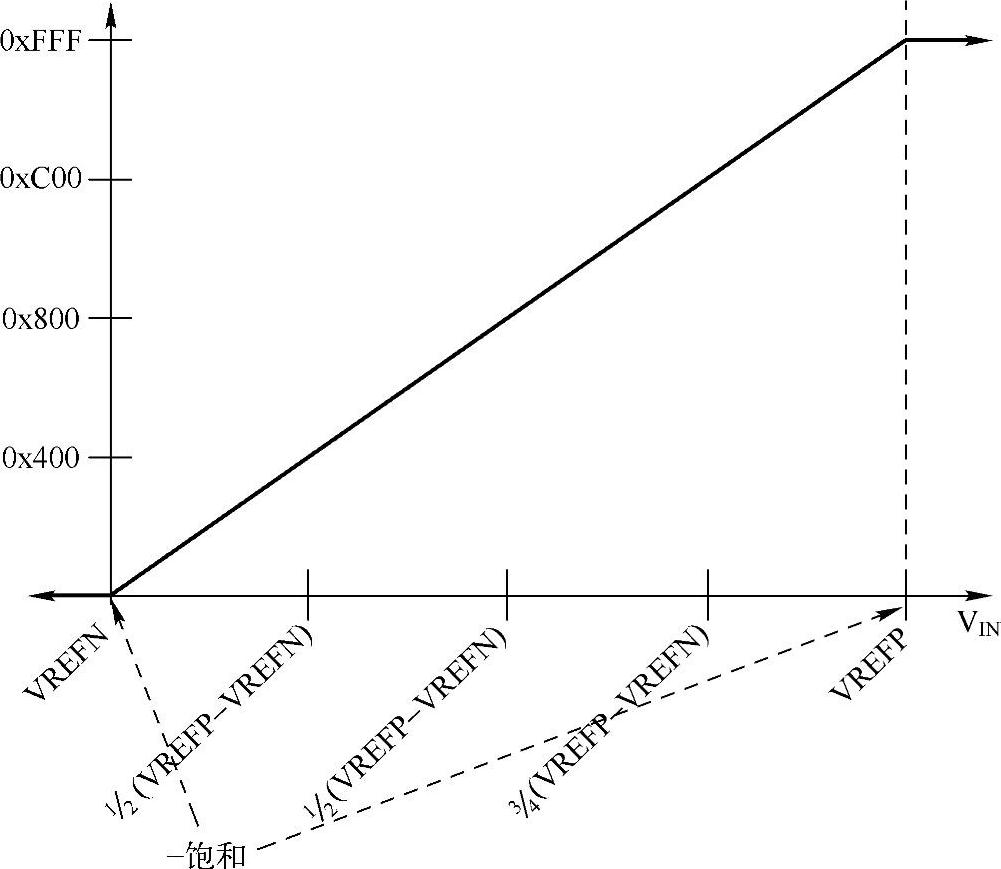

转换值的范围为0x000~0xFFF。在单端输入模式,0x000值对应的电平为VREFN;而0xFFF值对应的电平为VREFP。此配置的结果可用下列公式计算:

mV per ADC code=(VREFP-VREFN)/4096

尽管模拟输入引脚可以处理超出此范围的电压,但在欠电压及过电压时A-D转换结果将会饱和。图4-7所示为ADC与输入模拟电压的函数关系。

图4-7 ADC转换结果

(2)差分采样

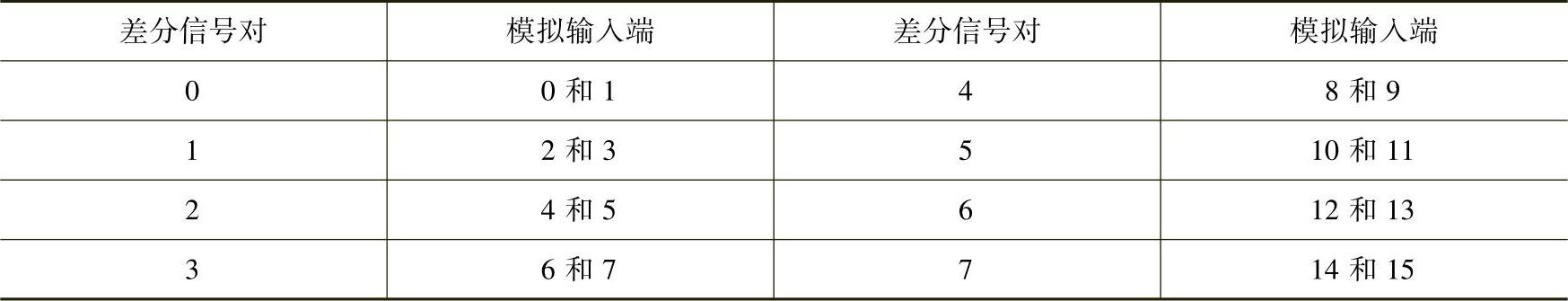

除了传统的单端采样,ADC模块还支持对两个模拟输入通道进行差分采样。差分采样可通过设定ADCSSCTL0寄存器中的Dn位来使能。若采样序列中某个采样动作配置为差分采样,必须通过ADCSSMUXn寄存器来选择输入的差分信号对。差分信号对0对模拟输入端0和1进行采样,差分信号对1对模拟输入端2和3进行采样,依此类推,见表4-3。

表4-3 差分采样对

注意:ADC不支持差分信号对的随机组合,如模拟输入端0和模拟输入端3无法作为一对差分信号输入。

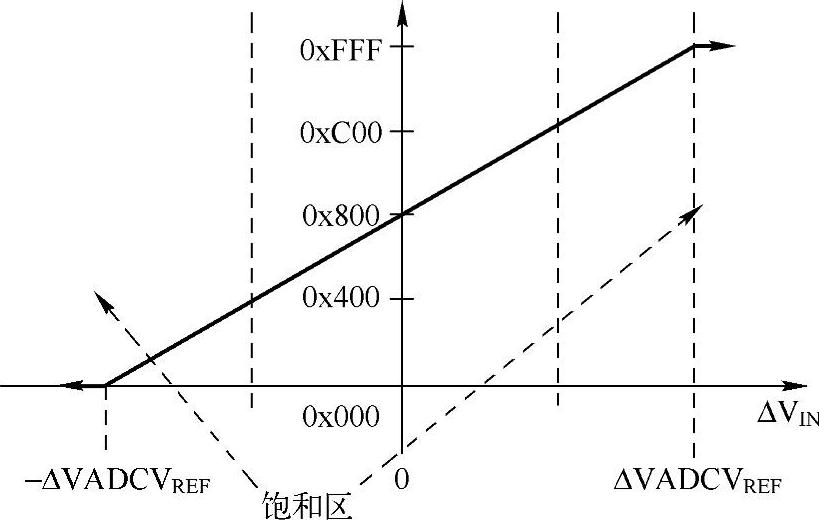

差分模式下采样电压是奇数通道与偶数通道电压的差值:

➢差分电压为ΔV=VIN_EVEN(偶数通道)-VIN_ODD(奇数通道)。

➢如果ΔV=0,则转换结果=Ox800。

➢如果ΔV>0,则转换结果>Ox800(取值范围为Ox800-OxFFF)。

➢如果ΔV<0,则转换结果<Ox800(取值范围为0-Ox800)。

对于转换准确度为ΔV∈{-ΔVADCVREF,ΔVADCVREF}

分辨率为

差分采样如图4-8所示。

5.内部温度传感器

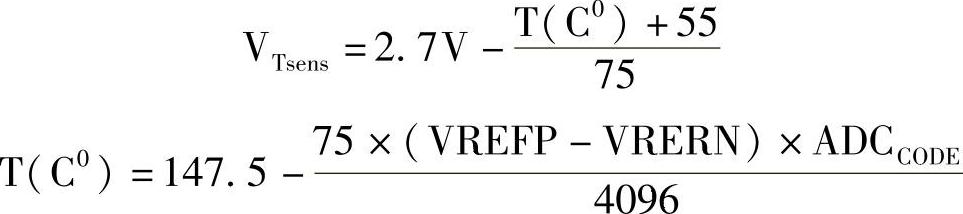

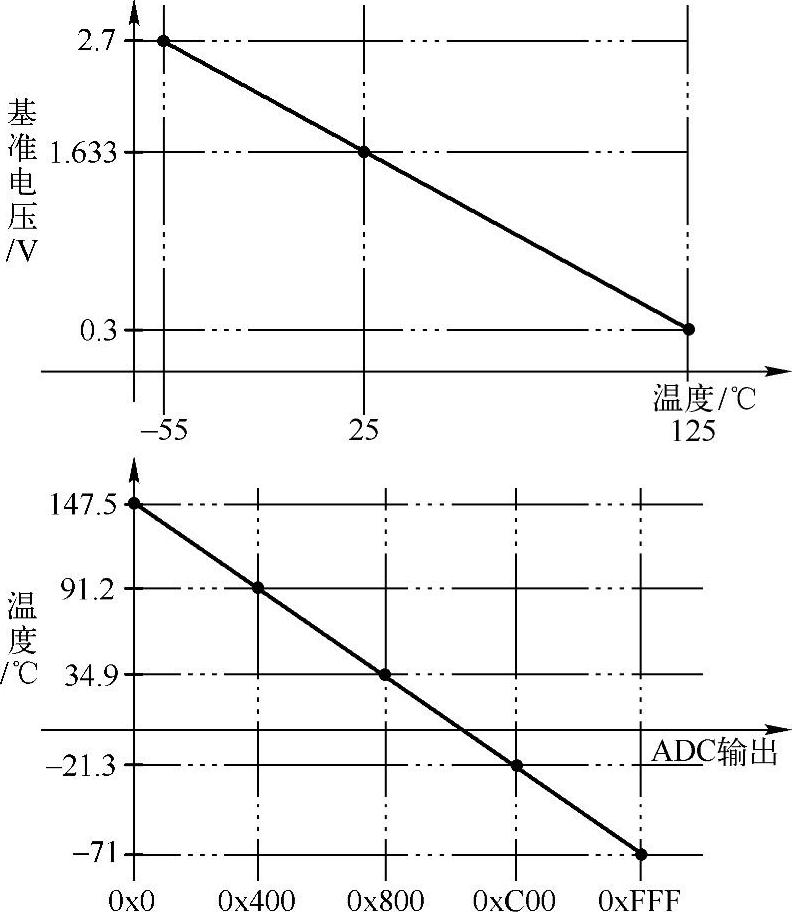

温度传感器的主要作用是当芯片温度过高或过低时向系统给予提示,保障芯片稳定工作。温度传感器没有单独的使能/禁止操作,因为它关系到带隙参考电压的产生,而带隙基准电压不仅提供给ADC模块、还需要提供给片内其他所有模拟模块,因此必须始终使能。内部温度传感器提供模拟温度读数以及基准电压VTsens(如图4-9所示),其大小可以通过下列公式计算:

其中,ADCCODE为ADC读数、最大ADC电压范围为VREFP-VREFN。

图4-8 差分采样

图4-9 内部温度传感器

6.数字比较器

ADC通常用于对外部信号采样并监控其数值的变动,确保其保持在给定的范围内。为了实现此监控过程的自动化、减少所需的处理器开销,每个ADC模块提供8个数字比较器。ADC转换结果可直接发送给数字比较器,与用户编程的门限进行比较。门限通过ADC数字比较器范围寄存器(ADCDCCMPn)配置。假如被监控的信号超出了容许的范围,则产生一个处理器中断及/或向PWM模块发送一个触发事件。用户可将数字比较器的4种工作模式(单次触发、持续触发、迟滞单次触发、迟滞持续触发)应用于3个相互独立的区域(低频段、中频段、高频段)中。Tiva C ADC详细的技术文档请参考TI的相关文献。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。