PCI(Peripheral Component Interconnect,外部设备互联)总线是由Intel、IBM、Compaq、HP、DEC等100多家公司于1992年6月共同推出的。PCI总线数据线和地址线复用,是一种高带宽、与处理器无关的高性能局部总线,它采用同步时序协议和集中式仲裁策略,支持多个设备,与CPU时钟频率同步,有严格的规范来保证其高度的可靠性和兼容性。PCI总线支持64位数据传输、多总线主控和线性突发方式,数据传输率达到132~246MB/s。PCI提供两种电源信号环境:5V、3.3V,并可进行两种环境的转换,其优良性能满足了图形图像传输与显示、高速网络传输等的要求,是目前最流行、应用最广泛的总线。

1.PCI的特点

PCI总线是一套整体的系统解决方案,在速度、效益、规范性、扩展性等方面都优于ISA、VESA等总线,其主要特点包括:

(1)线性突发传输模式

PCI支持突发的数据传输模式,即能在瞬间发送大量的数据,满足新型处理器高速缓冲存储器与内存之间的读/写。线性突发传输能够更有效地运行总线的带宽去传输数据,以减少不必要的寻址操作。

(2)支持总线主控方式和同步操作

挂接在PCI总线上的设备有“主控”和“从控”两类。总线主控是大多数总线的常见功能,PCI总线允许任何一个处理器或其他具有总线主控能力的设备接管总线,成为总线主控设备,以加速执行高吞吐量、高优先次序的任务。PCI允许微处理器和总线主控制器同时操作,微处理器内部的操作和总线操作可以同时进行。

(3)独立于处理器

PCI是一种独立于处理器的总线标准,与CPU结构无关,支持多种处理器,适用于多种不同的系统。在PCI总线构成的系统中,接口和外围设备的设计是针对PCI而不是CPU的,当CPU因为过时而更换时,接口和外围设备仍然可以正常使用。

(4)即插即用

PCI标准允许PCI局部总线扩展卡进行自动配置,支持即插即用的功能。总线的接口卡上都设有“配置寄存器”,当系统加电时,用程序来给这些设备分配端口地址等系统资源,为每个卡建立配置表,实现即插即用。

(5)适应性广

PCI局部总线不仅为PC提供合理的局部总线设计,也适用于便携式计算机和服务器等。支持3.3V的电源环境,延长电池寿命,为计算机小型化创造了良好的实现条件。PCI总线在开发时预留了足够的发展空间,支持64位地址/数据多路复用。PCI的64位延伸设计,可将系统的数据传输速率提高到264MB/s。

(6)良好的兼容性

PCI总线设计考虑了和其他总线的配合使用,通过“桥”芯片进行不同标准信号之间的转换。PCI总线能与ISA、EISA、VESA、MCA等标准兼容,实现多种总线共存。

2.PCI总线信号定义

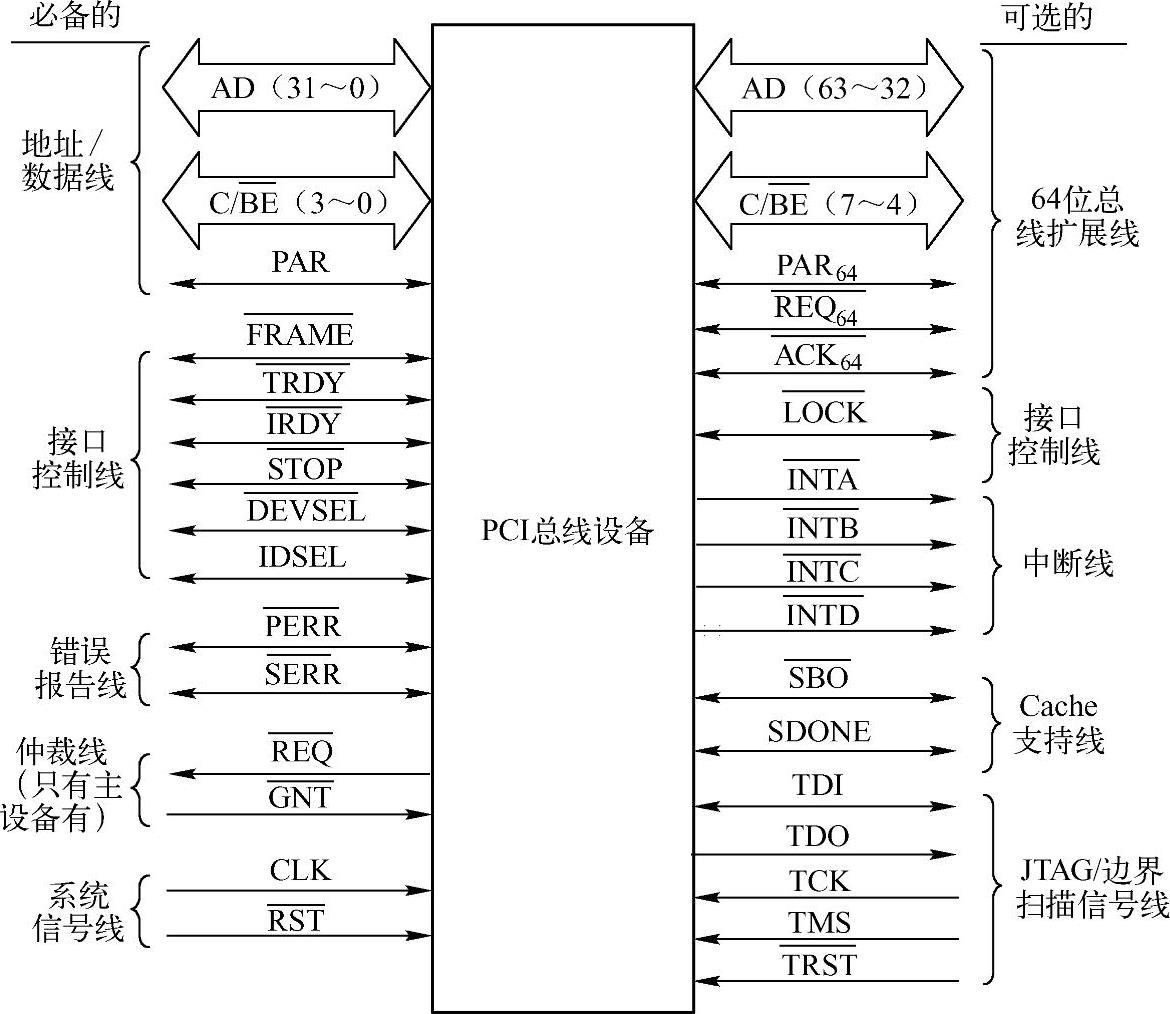

PCI总线的有些信号是必备的,有些信号是可选的,这是为进一步提高性能所需要的。图10-2所示为PCI总线信号定义。

(https://www.xing528.com)

(https://www.xing528.com)

图10-2 PCI总线信号定义

(1)必备信号

必备信号是32位PCI接口必不可少的,具体如下:

地址/数据线:AD31~AD0、 、PAR。

、PAR。

接口控制信号: 、

、 、

、 、

、 、

、 、IDSEL。

、IDSEL。

错误报告信号:PERR、SERR

裁决信号: 、

、 。

。

系统信号: 、CLK。

、CLK。

(2)可选信号

可选信号是PCI作为高性能接口使用而进行的功能和性能方面的扩展,具体如下:64位总线扩展信号:AD63~AD32、 、PAR64、

、PAR64、 、

、 。

。

中断信号: 、

、 、

、 、

、 。

。

支持高速缓存(Cache)信号: 、SDONE。

、SDONE。

边界扫描信号:TDI、TDO、TCK、TMS、 。

。

接口控制信号: 。

。

上述信号在插槽上的位置和定义见表10-2。PCI具有系统信号线、地址/数据线、接口控制线、中断信号线等一共188条引脚信号线。

表10-2 PCI总线信号定义

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。