模拟量通过A/D转换器转化为二进制码或BCD码表示的十进制数字量,转换器输出的二进制码或BCD码数字量与输入模拟量成比例。实现A/D转换的基本方法有十几种,常用的有计数法、逐次逼近法、双斜积分法和并行转换法。由于逐次逼近型A/D转换具有转换速度快、转换精度较高等优点,而且采用这种方法的ADC芯片成本较低,因此在计算机数据采集系统中获得了广泛的应用。为此,本节仅介绍逐次逼近型A/D转换器的原理和它们的使用。

逐次逼近型A/D转换器的转换原理是把输入电压Vi和一组从参考电压分层得到的量化电压进行比较,比较从最大的量化电压开始,由粗到细逐次进行,由每次比较的结果来确定相应的位是1还是0,不断地比较,不断地逼近,直到两者的差别小于允许的误差范围时即完成了一次转换。

图9-12是逐次逼近型A/D转换器结构框图,一般由电压比较器、D/A转换器、去码/留码控制逻辑、移位寄存器和输出锁存器等组成。它的工作过程是:当出现启动脉冲时,移位寄存器和输出锁存器全部清零,故D/A转换器输出也为零。当第一个时钟脉冲到达时,移位寄存器最高位被置1,这时D/A转换器输入为10000000,转换输出电压Eo为其满刻度的一半,它与输入电压进行比较,若Vi>Eo,则输出锁存器高位将1锁存(若Vi<Eo,则不锁存);移位寄存器右移1位,此时D/A转换器输入为11000000,它所转换的电压Eo再与输入电压Vi进行比较,若Vi>Eo,则输出锁存器将该位1锁存(否则不锁存);这时移位寄存器又右移1位。上述过程重复进行,直到移位寄存器右移溢出为止,这时右移脉冲就作为A/D转换结束信号EOC,锁存器锁存的结果就是A/D转换的结果。

图9-12 逐次逼近式A/D转换器结构框图

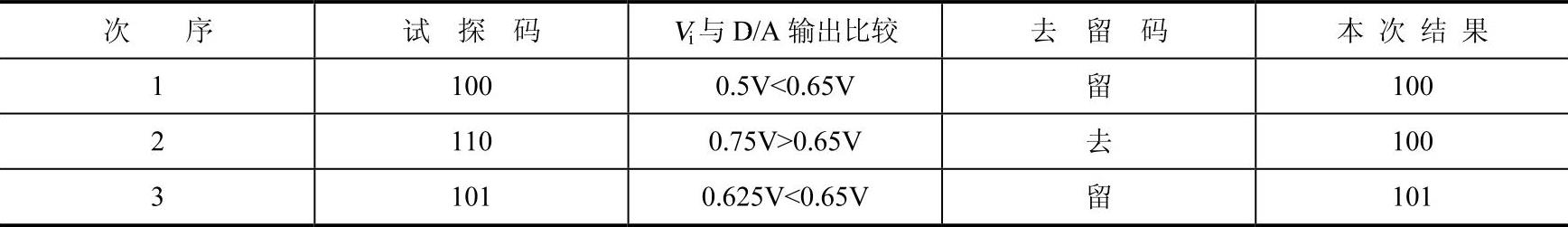

假设该A/D转换器所用D/A转换满量程为1.0V,满量程为1.0V时,A/D转换器输出为111。设输入电压为0.63V,则转换情况如下:

①当启动脉冲被接收后,在第一个时钟脉冲时间,移位寄存器最高位置1,其编码为100,D/A转换器将它转换成0.5V输出电压Eo,送到比较器N的“-”输入端,与Vi进行比较,因Vi>Eo,即0.63V>0.5V,去码/留码控制逻辑保留最高位的1,并送至输出锁存器锁存。(https://www.xing528.com)

②在第二个脉冲时间,移位寄存器右移,次高位变成1,由于上次比较后最高位保留了1,因此送到D/A转换器的代码为110,输出电压Eo=0.75V,比较结果因Vi<Eo,所以该位1不保留,即不锁存,而被置成0,故输出锁存器仍为100。

③在第三个脉冲时间,寄存器移位成最低位为1,送到D/A转换器的代码为101,输出电压Eo=0.625V,此时,Vi>Eo,故该位被保留,输出锁存器成为101。

④在第四个脉冲时间,移位寄存器右移溢出,输出的数据就是转换结果,此时控制逻辑产生EOC转换结束信号,至此转换完成。

整个比较过程见表9-1。

表9-13 位逐次逼近型A/D转换过程(VR=1.0V,Vi=0.63V)

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。