Intel 8259A是8086序列兼容的可编程中断控制器,它把中断识别、中断优先权判断、中断屏蔽、提供中断向量等功能集于一身,适用于各种不同的环境,具有很强的管理功能,其主要功能如下:

①NMOS工艺,单一+5V电源,无需外加时钟。

②一片8259A可管理8级优先级中断源,通过级联最多可以管理64级中断源。

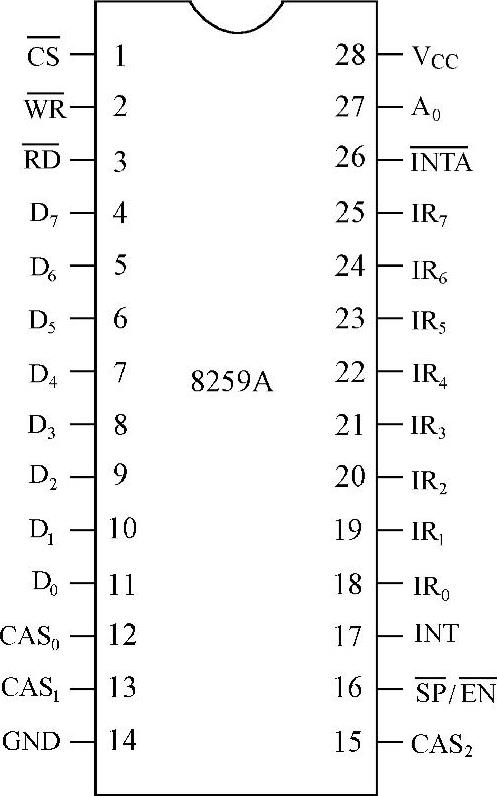

图7-6 8259A的引脚排列

③每一级中断源都可以通过编程进行屏蔽或开放。

④在中断响应周期,8259A提供相应的中断类型号。

⑤可以通过编程方式来选择8259A的各种工作方式。

1.8259A的外部引脚

Intel 8259A是双列直插式28脚的可编程中断控制芯片,它的引脚排列如图7-6所示。各引脚的功能如下: :片选输入端,低电平有效,一般通过地址译码逻辑电路与高位的地址总线相连。

:片选输入端,低电平有效,一般通过地址译码逻辑电路与高位的地址总线相连。 :写信号输入端,低电平有效,用来通知8259A从数据线上接收数据。一般这些数据就是CPU往8259A发送的命令字(ICW、OCW)。

:写信号输入端,低电平有效,用来通知8259A从数据线上接收数据。一般这些数据就是CPU往8259A发送的命令字(ICW、OCW)。 :读信号端,低电平有效,用来通知8259A将某个内部寄存器(IRR、ISR、IMR)的内容送到数据总线上。

:读信号端,低电平有效,用来通知8259A将某个内部寄存器(IRR、ISR、IMR)的内容送到数据总线上。

D0~D7:8位的双向三态数据引脚,在系统中它们与数据总线相连,实现与CPU的数据交换。在较大的系统中,一般使用总线驱动器与D0~D7相连,采用缓冲方式;在小系统中,一般数据总线直接与D0~D7相连,采用非缓冲方式。CPU通过I/O读命令由D0~D7将8259A中内部寄存器的内容送入CPU,通过I/O写命令由D0~D7实现对8259A进行编程。

CAS2~CAS0:级联总线端口,这三条引脚上的信号用来指出具体的从片。在多片8259A进行级联时,各片8259A的CAS2~CAS0分别互连起来,8259A作为主控制器时,该总线为输出,作为从控制器时,该总线为输入。 :从片/允许缓冲信号引脚,该引脚为双功能引脚。在非缓冲模式中,

:从片/允许缓冲信号引脚,该引脚为双功能引脚。在非缓冲模式中, 引脚作为输入引脚,用来决定本片8259A在系统中作从片还是作主片使用,

引脚作为输入引脚,用来决定本片8259A在系统中作从片还是作主片使用, 则作为主片,

则作为主片, 则作为从片。在缓冲模式中,

则作为从片。在缓冲模式中, 引脚作为输出引脚,控制收发器的接收或发送。

引脚作为输出引脚,控制收发器的接收或发送。

INT:一般与CPU的INTR引脚相连,用来向CPU发出中断请求信号。级联时从片上的INT端口与主片相连。

IR0~IR7:中断请求信号端口,8个引脚用来从外部设备接收中断请求,在多片8259A级联的复杂系统中,主片的IR0~IR7分别与各从片的INT端口相连,用来接收从片的中断请求。在边沿触发方式中,IR输入应由低到高,此后保持高电平,直到被响应。在电平触发方式中,IR输入应保持高电平。 :中断响应信号端口,用来接收CPU的中断应答信号。CPU通过该引脚通知8259A中断请求已被响应,使8259A将中断类型码送到数据总线上。

:中断响应信号端口,用来接收CPU的中断应答信号。CPU通过该引脚通知8259A中断请求已被响应,使8259A将中断类型码送到数据总线上。

A0:地址输入信号,用来指出当前8259A的哪个端口被访问。1片8259A对应两个端口地址,其中一个为偶地址,一个为奇地址,并且要求偶地址低于奇地址。在与8086系统相连时,可以将该引脚直接与地址总线上的A0相连。另外由于8086有16根数据线,而8259A只有8根,若要8086与8259A的所有数据传送都采用低8位,最简单的方法就是将该引脚直接与地址总线上的A1相连。这样,就可以用两个相邻的偶地址作为8259A的端口地址,保证了采用低8位。这时从CPU的角度看A0的值是固定的,而A1的值发生变化,分别对应两个端口。

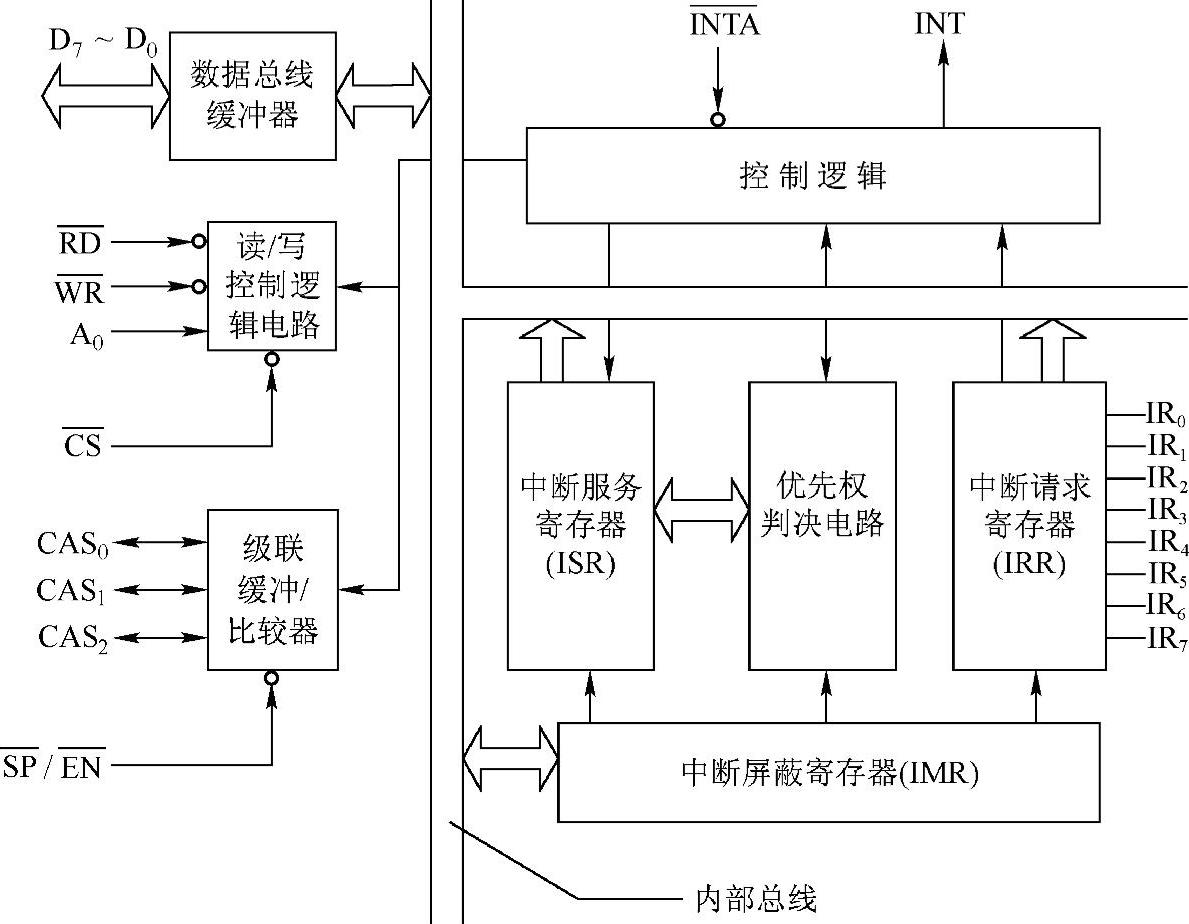

2.8259A的内部结构

8259A的内部结构如图7-7所示,主要由8个功能模块组成:中断请求寄存器IRR、中断屏蔽寄存器IMR、中断服务寄存器ISR、优先权判决电路PR、数据总线缓冲器、读/写控制逻辑电路、控制逻辑和级联缓冲/比较器。各部分的功能如下:

图7-78 259A的内部结构(https://www.xing528.com)

(1)中断请求寄存器(Interrupt Request Register,IRR)

IRR用来存放中断请求。某位为l表示相应的中断请求线IR有请求,为0表示该引脚无请求。将IRR某位置1的方式称为触发方式。有两种触发方式:边沿触发和电平触发,前者是利用IR线由低到高的跳变,后者要求IR线为高电平并保持到第一个中断响应信号INTA结束之前。在电平触发方式下,要求中断请求得到响应之后请求输入端必须及时撤除高电平。如果在CPU进入中断处理过程并且开放中断前未去掉高电平信号,则可能引起不应该发生的第二次中断。相比之下,边沿触发方式用起来要方便一些。触发方式由初始化命令字ICWl来设置。

(2)中断屏蔽寄存器(Interrupt Mask Register,IMR)

IMR存放着8个屏蔽位信息,某位为0表示对应的中断源未被屏蔽,为1表示对应的中断源被屏蔽。被屏蔽的中断源的请求不能参与中断判优,也就不可能向CPU提出中断请求。

(3)中断服务寄存器(In-Service Register,ISR)

ISR存放着当前正在服务的所有中断级。某位为1表示相应的中断正在服务中。ISR中可能有多位为l,这表明当前出现了中断嵌套。

(4)控制逻辑

控制逻辑含一组初始化命令寄存器和一组操作命令寄存器,按预置的工作方式(初始化命令字)或程序员的干预(操作命令字)来管理8259A的全部工作。

(5)优先权判决电路

优先权判决电路对保存在IRR中的各种中断请求以及IMR的内容进行判断,确定出最高优先级,如果当前没有正在服务的中断或者它比当前正在服务的级别高,则在CPU中断响应期间把它选通至ISR。简言之,在中断响应期间,优先权判决电路找出应该服务的中断,将ISR相应位置位。

(6)级联缓冲/比较器

级联是指使多片8259A连接起来,管理更多级中断。该功能部件在级联方式的主片-从片结构中用来存放和比较系统中各从片标识(ID)。

(7)数据总线缓冲器

数据总线缓冲器是8259A与系统数据总线的接口,它是双向三态缓冲器。所有CPU对8259A编程时的控制命令字都是通过它写入的;且8259A的状态信息以及中断响应期间的中断向量也是通过它提供给CPU。

作为一个能与系统数据总线直接相连的芯片,都应设置数据总线缓冲器。在该芯片被选中时提供与系统数据总线的传送通道;在该芯片未被选中时使芯片内部的数据线与系统数据总线“脱开”(呈现高阻抗),这样不影响CPU与其他芯片的联系。

(8)读/写控制逻辑电路

该电路接收CPU的读/写命令,完成命令字的写入和状态字的读出等操作。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。