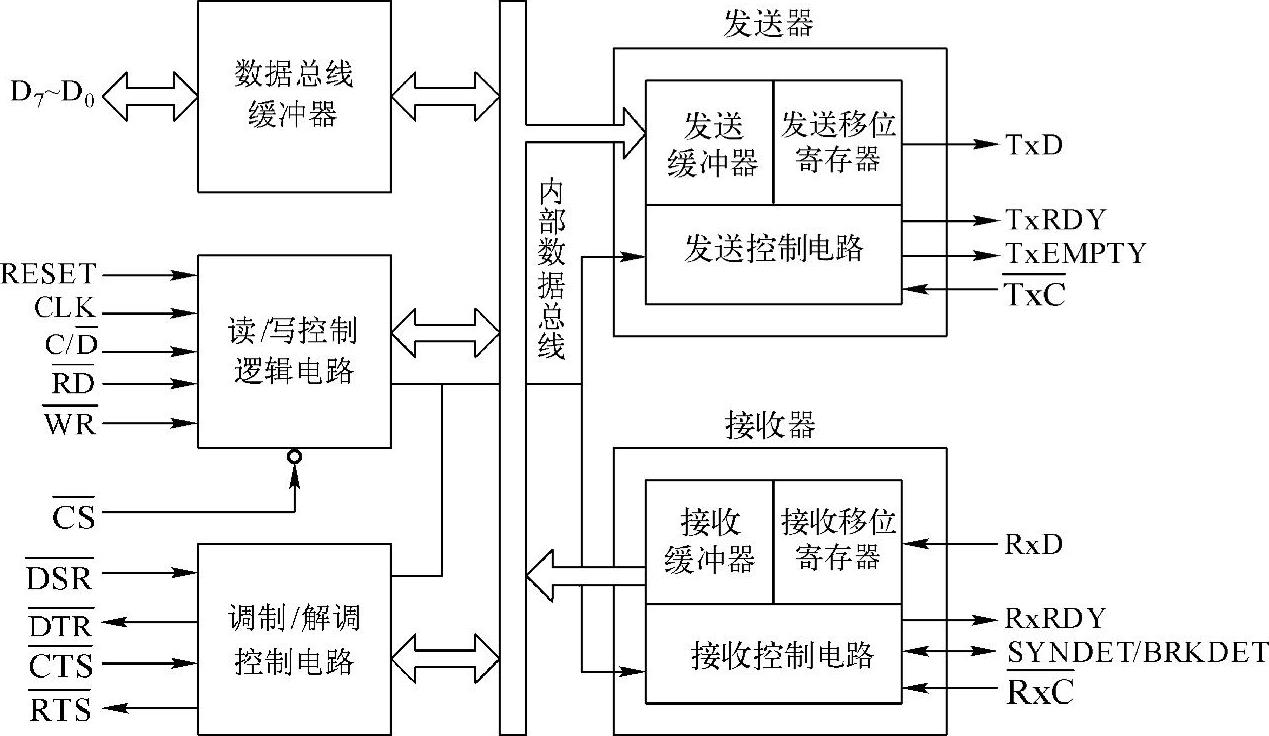

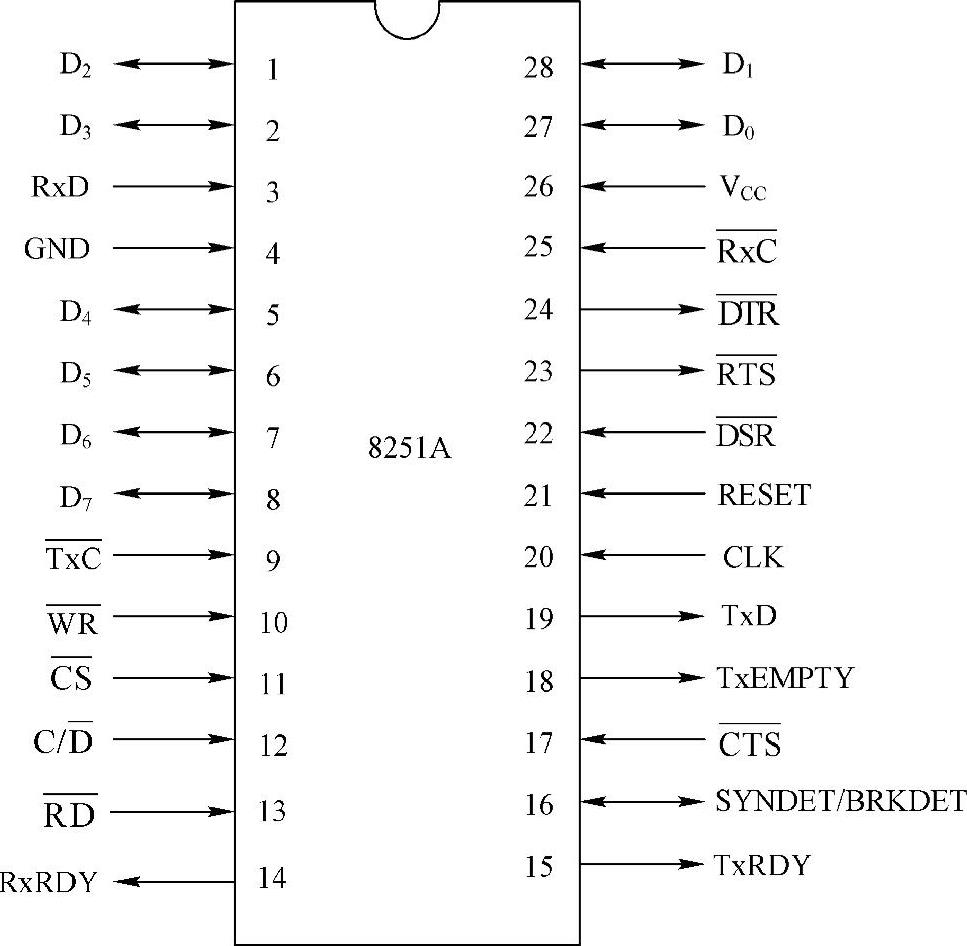

8251A由发送器、接收器、数据总线缓冲器、读/写控制逻辑电路及调制/解调控制电路等五部分组成。8251A的内部结构框图如图6-30所示,引脚图如图6-31所示。

图6-30 8251A的内部结构框图

1.发送器

825lA的发送器包括发送缓冲器、发送移位寄存器(并→串转换)及发送控制电路三部分。需发送的数据经内部总线锁存到发送缓冲器中。如果采用同步方式,则在发送数据之前,发送器将自动送出一个或两个同步字符(SYN),然后,移位寄存器把数据逐位串行输出。如果采用异步方式,则由发送控制电路在数据首尾加上起始位及停止位,然后从起始位开始,经移位寄存器从数据输出线TxD逐位串行输出。移位寄存器的输出速率由TxC引脚的时钟决定。

图6-31 8251A的引脚图

当发送器做好接收数据的准备时,由发送控制电路向CPU发出TxRDY有效信号,通知CPU可以向8251A输出数据。如果8251A与CPU之间采用中断方式传送数据,则TxRDY可作为向CPU发出的中断请求信号。

发送器的有关引脚信号如下:

TxD—数据发送线,输出串行数据。

TxRDY—发送器准备好信号,输出线,高电平有效。高电平表示8251A已初始化,或发送缓冲器中的数据已经送往移位寄存器,发送缓冲器可以接收新的并行数据。一旦CPU向8251A写入待发送字符后,TxRDY便变为低电平。

TxEMPTY—发送器空闲信号,输出线,高电平有效。该信号有效表示移位寄存器中的数据已经全部送出。发送缓冲器和发送移位寄存器构成发送器的双缓冲结构,因此在发送器发送串行数据的同时,可对之写入待发送数据。即在TxEMPTY为低电平期间,只要TxRDY为高电平,CPU就可以向8251A写入待发送数据。 —发送器时钟输入线。对于同步方式,

—发送器时钟输入线。对于同步方式, 的时钟频率等于发送数据的波特率。对于异步方式,波特率由软件定义,可以是TxC的1倍、1/16或1/64。1倍发送时,

的时钟频率等于发送数据的波特率。对于异步方式,波特率由软件定义,可以是TxC的1倍、1/16或1/64。1倍发送时, 输入时钟频率≤64kHz;1/16发送时,

输入时钟频率≤64kHz;1/16发送时, 输入时钟频率≤310kHz;1/64发送时,

输入时钟频率≤310kHz;1/64发送时, 输入时钟频率≤615kHz。

输入时钟频率≤615kHz。

2.接收器

8251A的接收器包括接收缓冲器、接收移位寄存器(串→并转换)及接收控制电路三部分。外部串行数据从RxD端逐位进入移位寄存器中。如果是同步方式,则要检测同步字符,确认已经达到同步,接收器才开始接收数据。如果是异步方式,则识别并删除起始位和停止位。当一组数据接收完毕时,便把移位寄存器中的数据并行送入接收缓冲器。这时,RxRDY引脚输出高电平,表示接收器已准备好数据,等待向CPU输出。接收缓冲器和接收移位寄存器构成接收器的双缓冲结构,在接收移位寄存器把已经接收完毕的数据送入接收缓冲器后,移位寄存器又可以马上接收新的串行数据。接收数据的速率由RxC端输入的时钟频率决定。

与接收器有关的引脚信号如下:

RxD—数据接收线,输入串行数据。

RxRDY—接收器准备好,输出线,高电平有效。该信号有效表示接收缓冲器已有数据等待向CPU输出。若采用中断方式进行串行通信,则RxRDY信号可用作向CPU发出的中断请求信号。当CPU读取接收缓冲器中的数据后,RxRDY便变为低电平。(https://www.xing528.com)

SYNDET/BRKDET—双功能引脚。对于内同步方式,当RxD端接收到指定的同步字符时,SYNDET输出高电平,表示接收器已达到同步。对于外同步方式,SYNDET是输入引脚,用于输入同步字符。对于异步方式,接收控制器检测串行线路是处于工作状态还是间断状态,当RxD端上连续收到8个“0”电平时,则BRKDET输出高电平,表示线路处于间断状态。 —接收器时钟输入线,作用与

—接收器时钟输入线,作用与 相似。一般情况下,接收器时钟应与发送方时钟一致。

相似。一般情况下,接收器时钟应与发送方时钟一致。

3.数据总线缓冲器

数据总线缓冲器是CPU与8251A之间信息交换的通道。它包含3个8位缓冲寄存器,其中两个分别用来存放8251A接收器所接收的数据和8251A的状态。CPU通过执行IN指令,可以从这两个寄存器中读取数据字或状态字。另一个缓冲寄存器存放CPU向8251A写入的数据或控制字。

与数据总线缓冲器有关的引脚为D7~D0,通常与系统数据总线相连。

4.读/写控制电路

读/写控制电路用来接收控制总线的控制信号,并向8251A内部各功能部件发出有关的控制信号,是8251A的内部控制器。

读/写控制电路接收的控制信号如下:

RESET—复位信号输入线,高电平有效。8251A复位后收发线路处于空闲状态。

CLK—时钟输入线,为8251A内部提供定时信号。允许输入的时钟频率范围为0.74~3.1MHz。对于同步方式,CLK必须大于发送时钟(TxC)和接收时钟(RxC)频率的30倍。

对于异步方式,CLK必须大于发送和接收时钟的4.5倍。 —片选信号输入线,低电平有效。

—片选信号输入线,低电平有效。 有效,表示该8251A芯片被选中,通常

有效,表示该8251A芯片被选中,通常 信号由端口地址译码器获得。

信号由端口地址译码器获得。 和

和 —读和写控制信号输入线,低电平有效。

—读和写控制信号输入线,低电平有效。 —控制/数据选择信号输入线。通常与CPU的A0引脚相连,与片选信号一起确定8251A的控制端口和数据端口地址。

—控制/数据选择信号输入线。通常与CPU的A0引脚相连,与片选信号一起确定8251A的控制端口和数据端口地址。

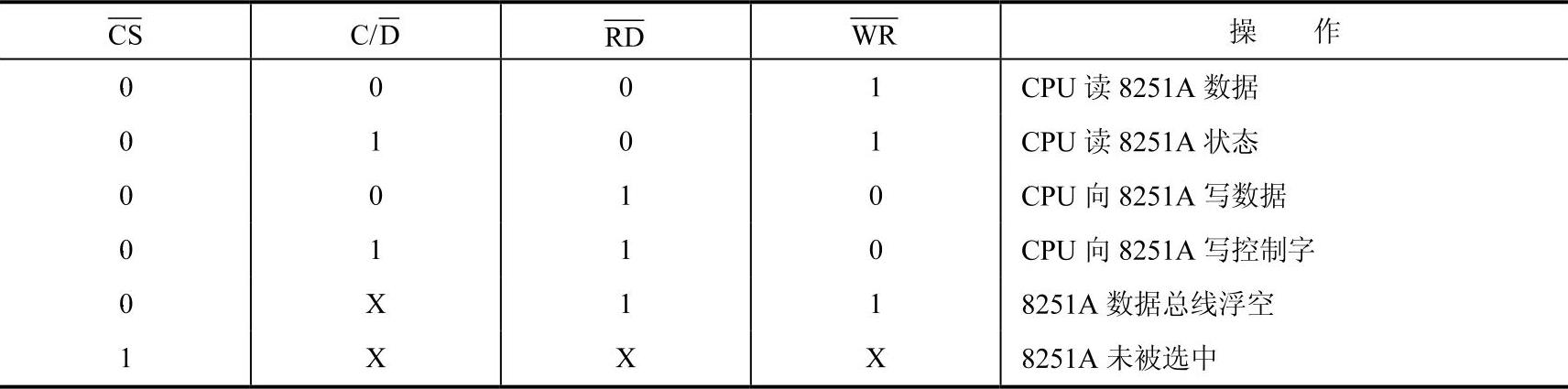

由 、

、 、

、 和

和 信号的组合可确定8251A的操作,见表6-5。

信号的组合可确定8251A的操作,见表6-5。

表6-5  、

、 、

、 和

和 信号的组合确定8251A操作

信号的组合确定8251A操作

5.调制解调控制电路

在进行远距离串行通信时,8251A输出的串行数据要经过调制器将数字信号转换成模拟信号,然后通过电话线路传送,接收端再通过解调器把模拟信号转换成数字信号送给8251A串行输入。为实现与调制解调器的连接,8251A提供了以下接口信号: —数据终端准备好,输出线,低电平有效。此信号有效表示CPU已准备好接收数据。

—数据终端准备好,输出线,低电平有效。此信号有效表示CPU已准备好接收数据。 —数据装置准备好,输入线,低电平有效。此信号有效表示调制解调器已准备好向8251A输出数据。

—数据装置准备好,输入线,低电平有效。此信号有效表示调制解调器已准备好向8251A输出数据。 是调制解调器对

是调制解调器对 的回答信号,CPU可以通过读8251A状态寄存器,检测其中的D

的回答信号,CPU可以通过读8251A状态寄存器,检测其中的D 位,DSR位为“1”,则表示

位,DSR位为“1”,则表示 信号有效。

信号有效。 —请求发送,输出线,低电平有效。此信号有效表示CPU已准备好发送数据,CPU可通过写8251A命令控制字,将RTS位置“1”,使RTS信号有效。

—请求发送,输出线,低电平有效。此信号有效表示CPU已准备好发送数据,CPU可通过写8251A命令控制字,将RTS位置“1”,使RTS信号有效。 —允许发送,输入线,低电平有效。此信号有效表示调制解调器已准备好接收来自CPU的数据。

—允许发送,输入线,低电平有效。此信号有效表示调制解调器已准备好接收来自CPU的数据。 是调制解调器对

是调制解调器对 的回答信号。只有在

的回答信号。只有在 有效,且控制字中的TxEN=1时,8251A的发送器才可发送数据。

有效,且控制字中的TxEN=1时,8251A的发送器才可发送数据。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。