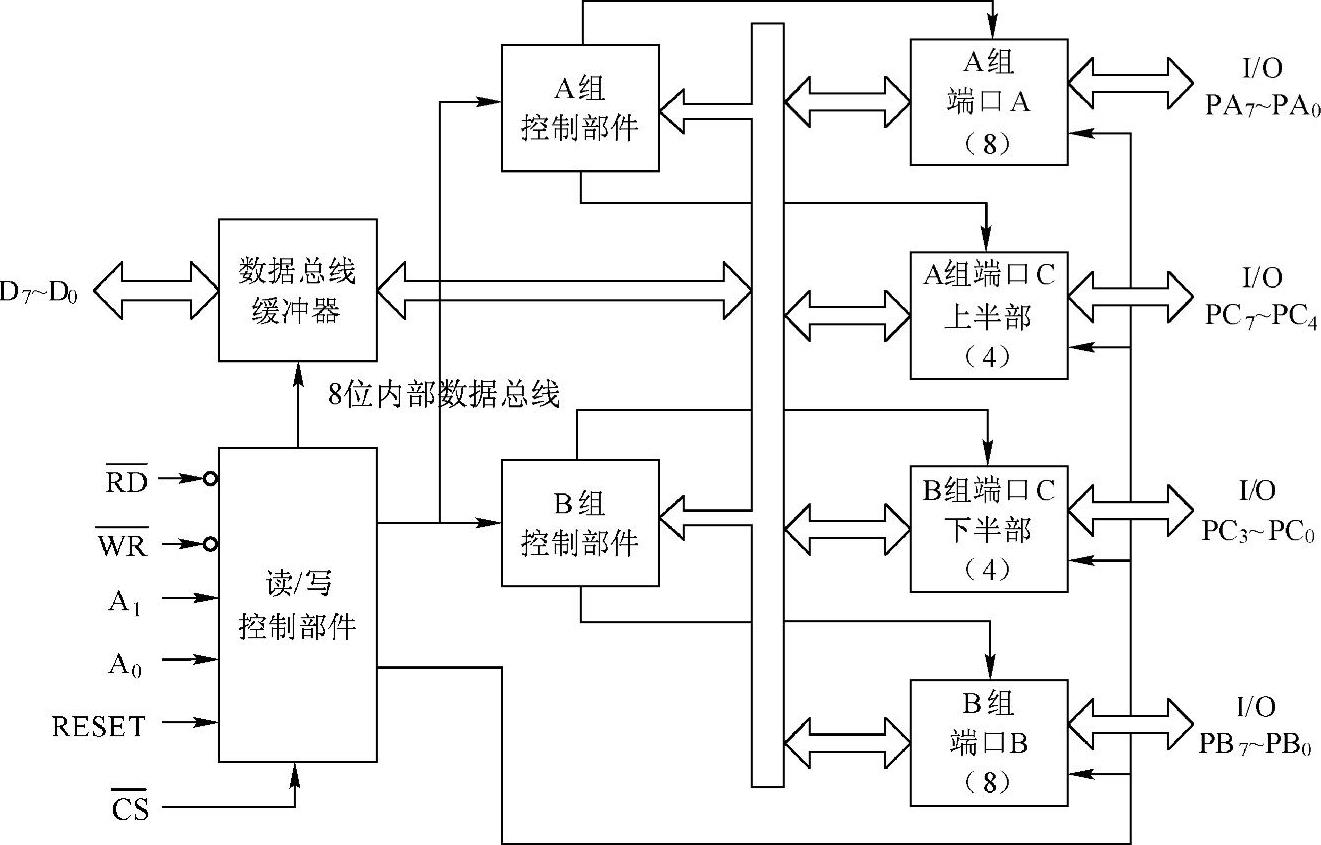

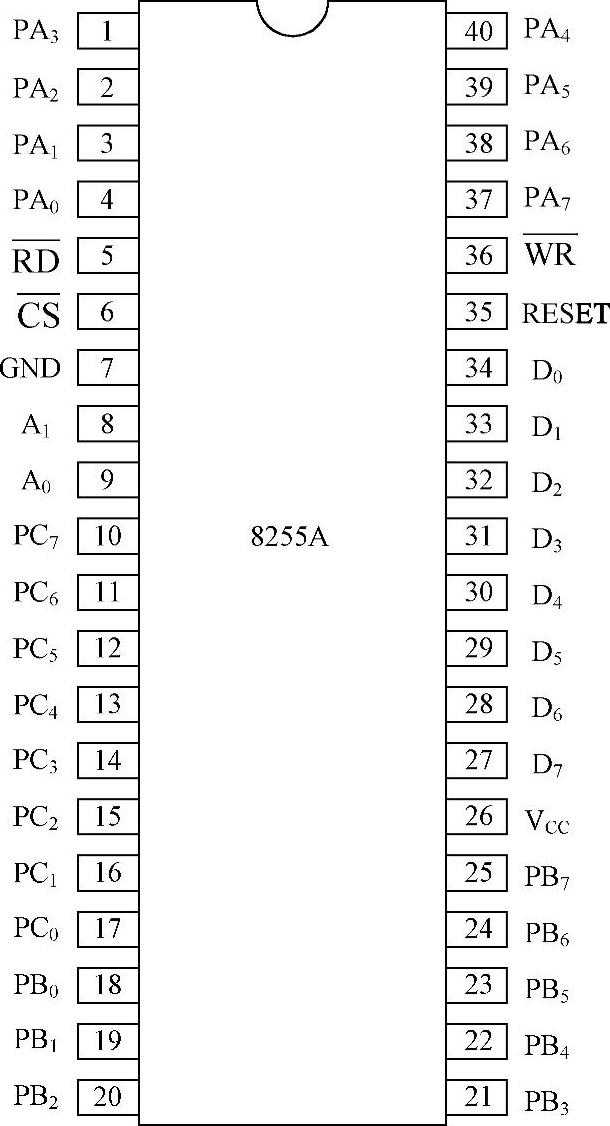

图6-14所示是8255A的内部结构框图。它由数据总线缓冲器、读/写控制逻辑、A和B组控制电路、数据端口等组成。图6-15所示是8255A的引脚分配图。

图6-14 8255A的内部结构框图

8位数据线D7~D0是双向三态总线,接至系统数据总线DB,在内部经数据总线缓冲电路后和各组控制寄存器及各端口数据寄存器连接。

两个低电平有效的信号 和

和 决定了CPU和8255A之间信息传递的方向。当

决定了CPU和8255A之间信息传递的方向。当 =0时,从8255A读至CPU;当

=0时,从8255A读至CPU;当 时,由CPU写入8255A。

时,由CPU写入8255A。

为片选信号,由系统地址线译码产生,低电平有效。地址信号A1、A0经片内译码产生4个有效地址,分别对应A、B、C三个独立的数据端口与一个公用的控制端口(内部控制寄存器)。在实际应用中,A1、A0通常接到系统地址总线的A1、A0。

为片选信号,由系统地址线译码产生,低电平有效。地址信号A1、A0经片内译码产生4个有效地址,分别对应A、B、C三个独立的数据端口与一个公用的控制端口(内部控制寄存器)。在实际应用中,A1、A0通常接到系统地址总线的A1、A0。

CPU对8255各端口进行读/写操作的信号关系见表6-3。

表6-3 8255A各端口读/写操作的信号(https://www.xing528.com)

RESET为复位信号,高电平有效。复位后,控制寄存器被清除,A、B、C三个端口全置成输入方式,且其锁存器也全清零,通常接系统复位RESET信号。

A、B、C三个端口各有8条端口I/O线,PA7~PA0、PB7~PB0及PC7~PC0。A口和B口类似,皆具有I/O锁存器和缓冲器。A、B、C三个端口作输出时,其输出锁存器的内容还可以由CPU用输入指令读回。在使用中,A、B、C三个端口可以当成三个独立的8位数据端口;也可以将A、B口当成8位数据端口,而C口各位作为它们与外设联络用的状态或控制信号,还可以将C口分成两部分,高4位和A口共同组成12位A组数据端口,低4位和B口共同组成12位B组数据端口。

图6-15 8255A的引脚分配图

控制寄存器用来接收对8255A编程写入的控制字,实现对A组和B组工作方式的控制。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。