8253各计数通道都有6种可供选择的工作方式。

1.方式0:计数结束中断方式

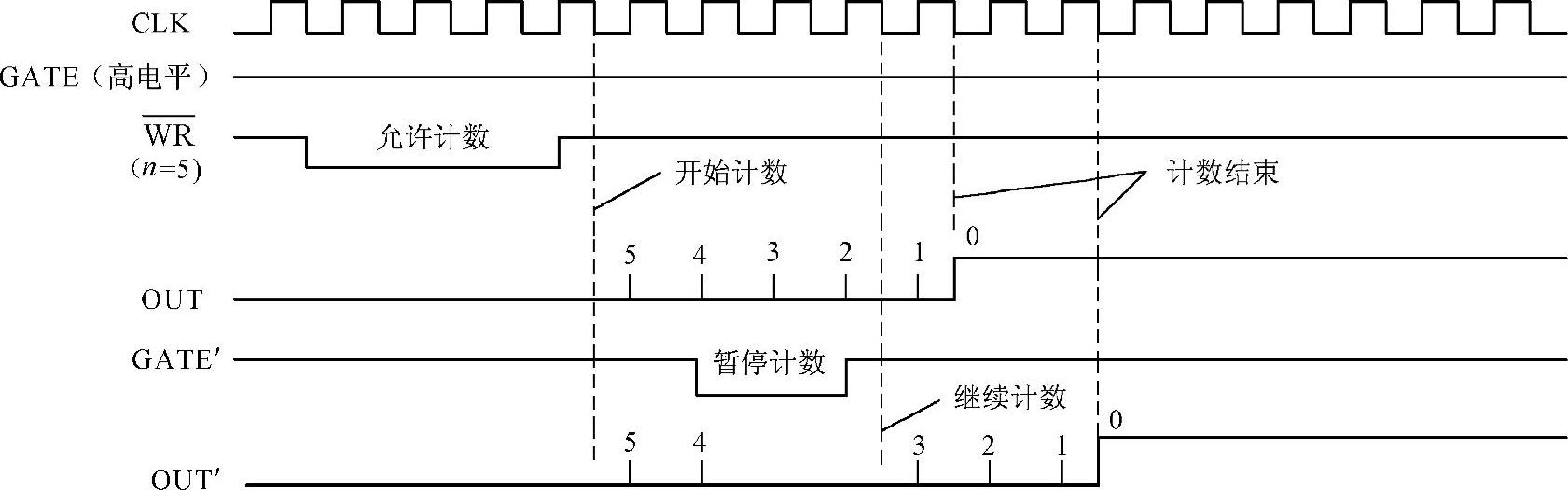

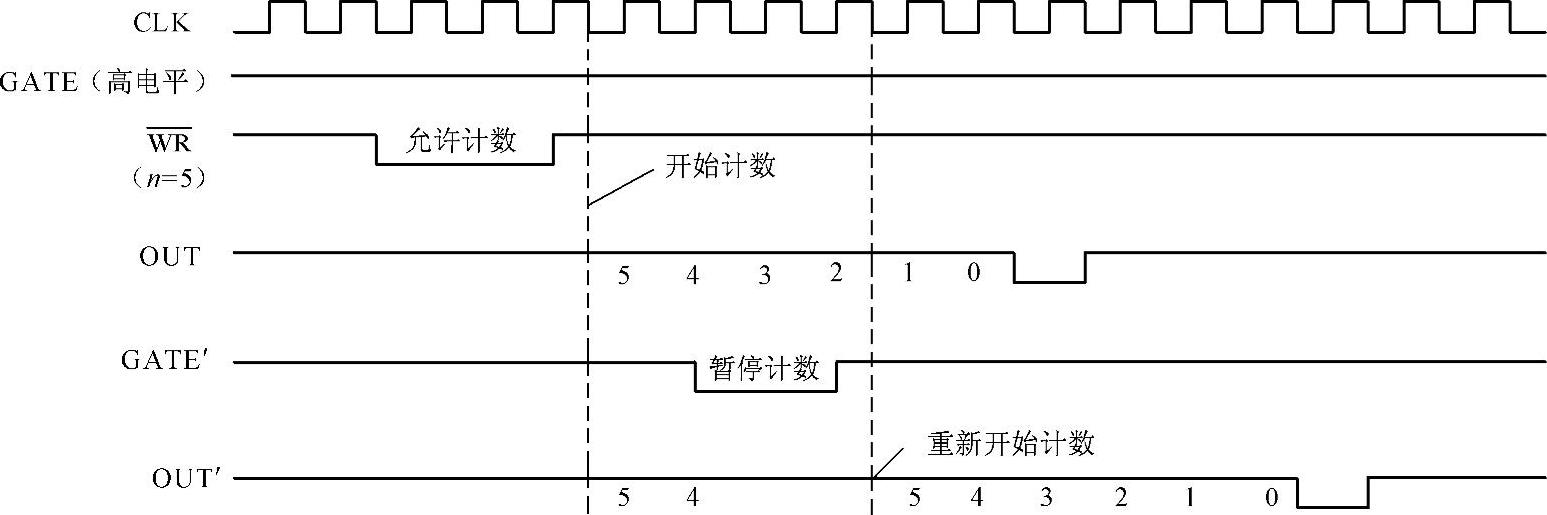

方式0的时序如图6-7所示。

图6-7 方式0的时序

当任一计数通道工作于方式0时,它具有如下特点:

①写入控制字后,OUT端输出低电平。当GATE为高电平,CPU写计数初值且装入CE后,CE即开始计数,在每个CLK脉冲的下降沿减1。当CE减至0时,OUT升为高电平。OUT高电平一直维持到写入新的控制字或写入新的计数值为止。

②计数初值一次有效,经一次CE减至0后,若需要继续定时或计数,则必须重新写入计数初值。

③GATE为低电平时,写入计数初值且装入CE后,并不计数,只有当GATE为高电平时才开始计数。设初值为n且后置GATE为高电平,则输出OUT在GATE为高电平后经n个CLK变为高电平。

④在计数过程中,GATE由高变低则停止计数,但不影响OUT的电平,当GATE变成高电平时,减1计数继续进行。

⑤在计数过程中,可以重新写入新的计数初值。重新写入初值且装入CE后,计数器按新的初值重新计数。

当计数器工作在方式0时,OUT由低变高的信号可供CPU查询或作为中断请求信号发送给CPU。

8253的内部操作是在CPU写计数初值的 信号上升沿将该计数初值送到CR中,在

信号上升沿将该计数初值送到CR中,在 信号上升沿之后的一个CLK脉冲将计数初值从CR中装入到计数执行部件CE中。这点不仅适用于方式0,也同样适用于其他工作方式。因此,就方式0而言,若计数初值为n,GATE为高电平,则从写入计数初值到CR至计数结束,OUT持续低电平的时间为n+1个CLK周期。

信号上升沿之后的一个CLK脉冲将计数初值从CR中装入到计数执行部件CE中。这点不仅适用于方式0,也同样适用于其他工作方式。因此,就方式0而言,若计数初值为n,GATE为高电平,则从写入计数初值到CR至计数结束,OUT持续低电平的时间为n+1个CLK周期。

2.方式1:可编程单稳态输出方式

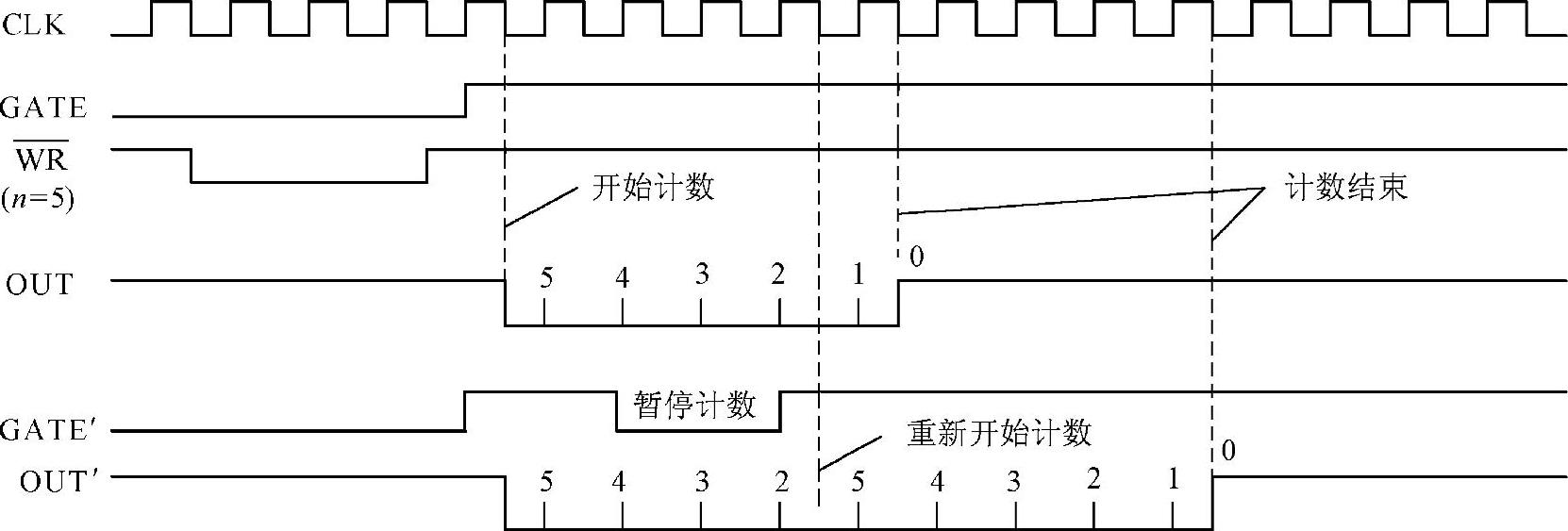

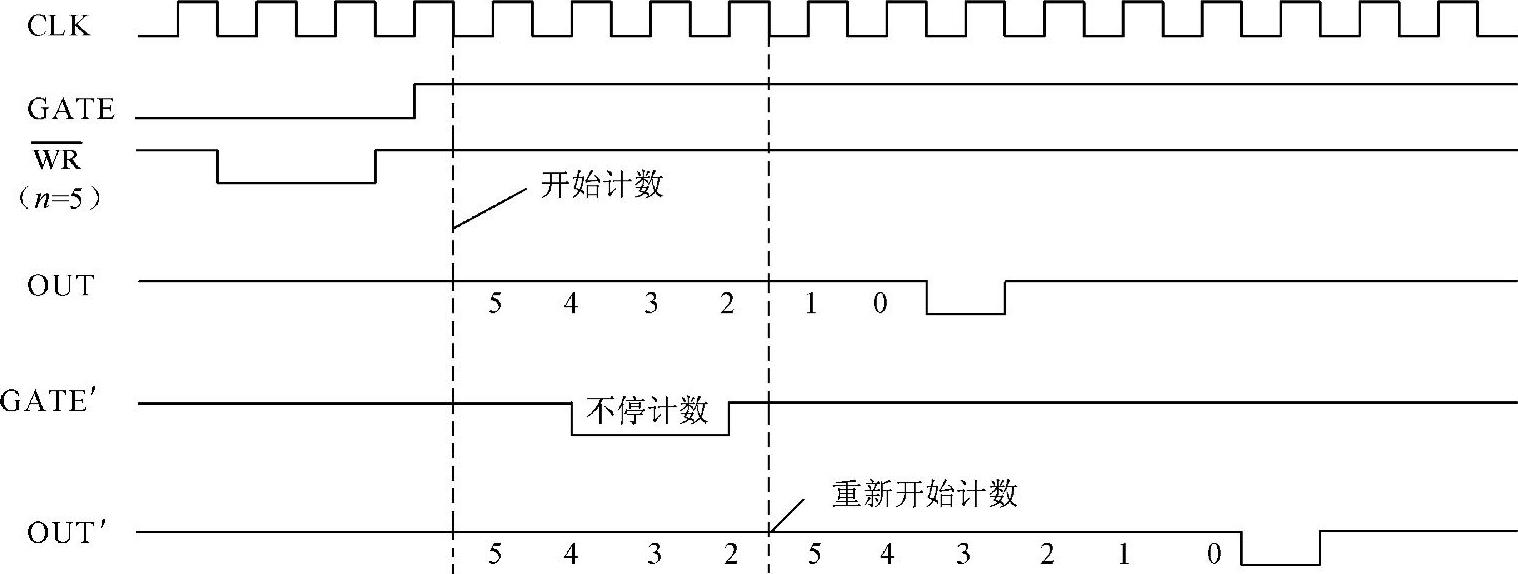

方式1的时序如图6-8所示。

当任一计数通道工作于方式1时,相当于一个可编程单稳态电路,触发电平为GATE。

该方式具有如下特点:

①写入控制字后,OUT端输出高电平。当CPU写计数值至CR后,无论GATE为高电平还是低电平,CR值都不装入CE。当GATE上升沿到来时,CR值装入CE并开始减1计数,OUT端输出低电平,产生单脉冲前沿,当CE计数到0时,OUT产生单脉冲后沿。可见,OUT端输出的是一个宽度为n个CLK的负脉冲。

图6-8 方式1的时序

②GATE触发重装初值。计数结束后若再次产生GATE上升沿,计数器会重新把CR值装入CE开始计数,直至计数值为0,OUT再次产生一个宽度为n个CLK的负脉冲。

③在计数过程中,GATE的下降沿不影响计数过程,GATE的上升沿则重新把CR值装入CE,使得从初值开始重新计数,故OUT负脉冲被加宽。

④在计数过程中,若将一个新的计数初值写入CR,当前计数不受影响,当下一个GATE上升沿到来时,按新初值进行减1计数。

3.方式2:频率发生器(又称分频器)

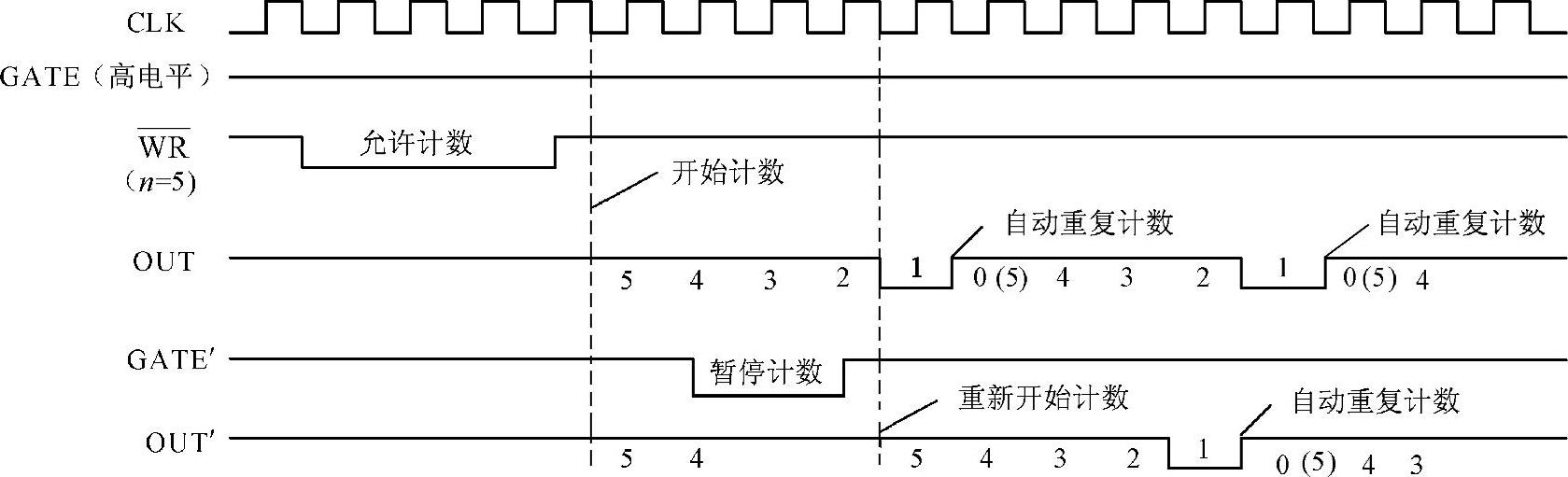

方式2的时序如图6-9所示。

图6-9 方式2的时序

当任一计数通道工作于方式2时,它具有如下特点:

①写入控制字后,OUT端输出高电平。当GATE为高电平,CPU写计数初值且装入CE后,CE开始减1计数。当减至1时,OUT端输出低电平;当完成计数到0时,OUT又变成高电平。产生计数到0负脉冲的同时,CR值再重新装入CE,开始一个新的计数过程。当初值为n时,OUT在n个CLK呈现一个输出周期。

②在计数过程中,若GATE变为低电平,则暂停减1计数,当GATE又变成高电平时,计数通道从初值开始重新计数。

③在计数过程中,重新写入新的计数初值,不会影响本次计数过程,在下一个计数周期开始按新的计数初值计数,即改变了分频系数。

4.方式3:方波发生器 (https://www.xing528.com)

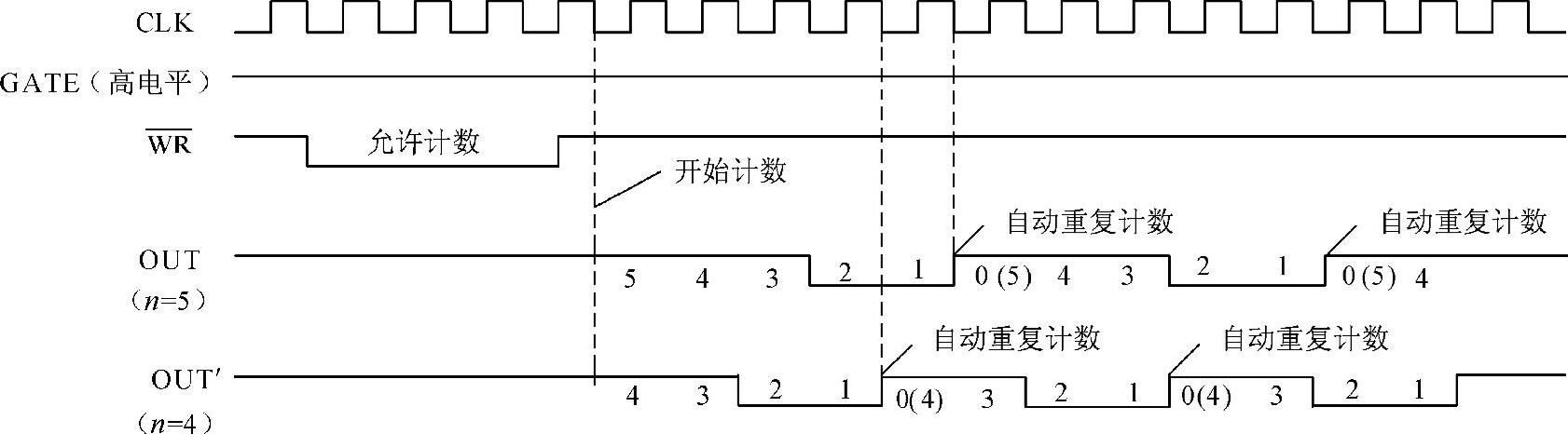

方式3的时序如图6-10所示。

图6-10 方式3的时序

当任一计数通道工作于方式3时,OUT输出的是方波或近似方波,它具有如下特点:

①写入控制字后,OUT端输出低电平。GATE变成高电平,CPU写计数初值并装入CE后,CE开始减1计数,装入CE后的CLK脉冲下降沿使OUT跳变为高电平。当计数到n/2(n为偶数)或(n+1)/2(n为奇数)时,OUT变成低电平,直到计数值为0,OUT又变成高电平,同时自动重装初值开始下一个周期的计数。即当初值为n时,OUT在n个周期呈现方波或近似方波的一个输出周期。

②在计数过程中,若GATE变为低电平,则暂停减1计数,当GATE又变成高电平时,计数器从初值开始重新计数。

③在计数过程中,重新写入新的计数初值,不会影响本次计数过程,在下一个计数周期开始按新的计数初值计数。

方式3的②、③两个特点同方式2的②、③。

5.方式4:软件触发方式

方式4的时序如图6-11所示。

图6-11 方式4的时序

当任一计数通道工作于方式4时,它具有如下特点:

①写入控制字后,OUT端输出高电平。当GATE为高电平,CPU写计数初值且装入CE后,CE开始减1计数。当减至0时,OUT端变为低电平,经过一个CLK后,OUT又变成高电平。即OUT在写入初值后经n+1个CLK负跳变,输出一个宽度为1个CLK的负脉冲。

②CPU写初值相当于一次软件的触发过程。当计数结束,OUT产生一个负脉冲后,只有CPU再次写初值,才可能重新触发计数。这点与方式0相同。

③在计数过程中,若GATE变为低电平,则暂停计数,当GATE又变成高电平时,计数器从初值开始重新计数。

④在计数过程中,若重新写入新的计数初值,则CR装入CE后开始按新的计数初值进行减1计数。

6.方式5:硬件触发方式

方式5的时序如图6-12所示。

图6-12 方式5的时序

当任一计数通道工作于方式5时,它具有如下特点:

①写入控制字后,OUT端输出高电平。当CPU写计数初值至CR后,无论GATE为高电平还是低电平,CR值都不装入CE,只有当GATE上升沿到来时,CR值才会装入CE,计数开始。当CE计数到0时,OUT端输出一个宽度为CLK的负脉冲。

②GATE触发可重复进行。若计数结束后再次产生GATE上升沿,则会重新把CR值装入CE开始计数。计数结束,再次产生一个宽度为CLK的负脉冲。

③在计数过程中,GATE的下降沿不影响计数过程,GATE的上升沿把初值从CR重新装入CE,使得从初值开始重新计数。

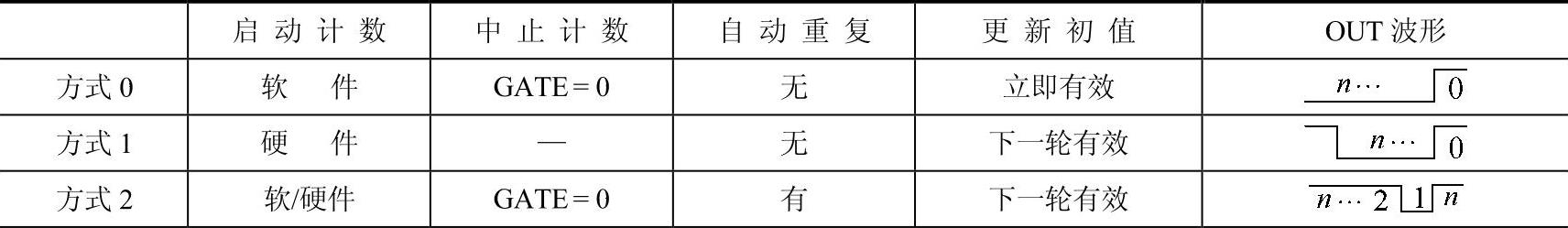

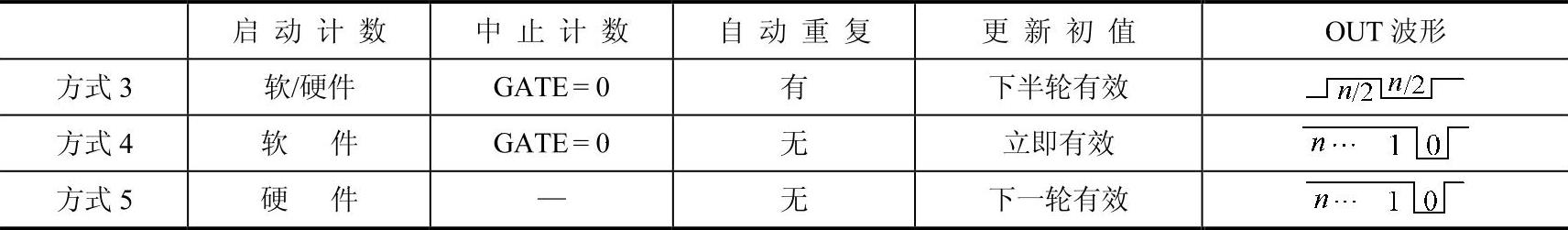

表6-2将8253计数器6种工作方式的特点作了简单比较,读者可结合前面的文字叙述加以理解。

表6-2 8253计数器工作方式一览表

(续)

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。