8086 CPU的操作是在时钟脉冲CLK的统一控制下按照一定的时间顺序来执行的。

①指令周期(Instruction Cycle)。一条指令从取出到执行结束所需的时间称为指令周期。不同指令的指令周期的长短是不同的,一个指令周期一般由几个总线周期组成。

②总线周期(Bus Cycle)。CPU通过存储器或I/O端口完成一个字节数据交换操作所需要的时间,称为一个总线周期。一个总线周期由几个T状态组成。

③时钟周期(Clock Cycle)。CPU的时钟频率的倒数,也称T状态。如8086的时钟频率为5MHz,其时钟周期为200ns。

在8086 CPU中,每个总线周期至少包含4个时钟周期(T1~T4)。一般情况下,在总线周期的T1状态传送地址,T2~T4状态传送数据。

8086 CPU的主要操作有:系统复位和启动、总线操作、最小模式下的总线保持、最大模式下的总线请求/允许等。下面介绍8086的几种操作时序。

1.系统的复位和启动

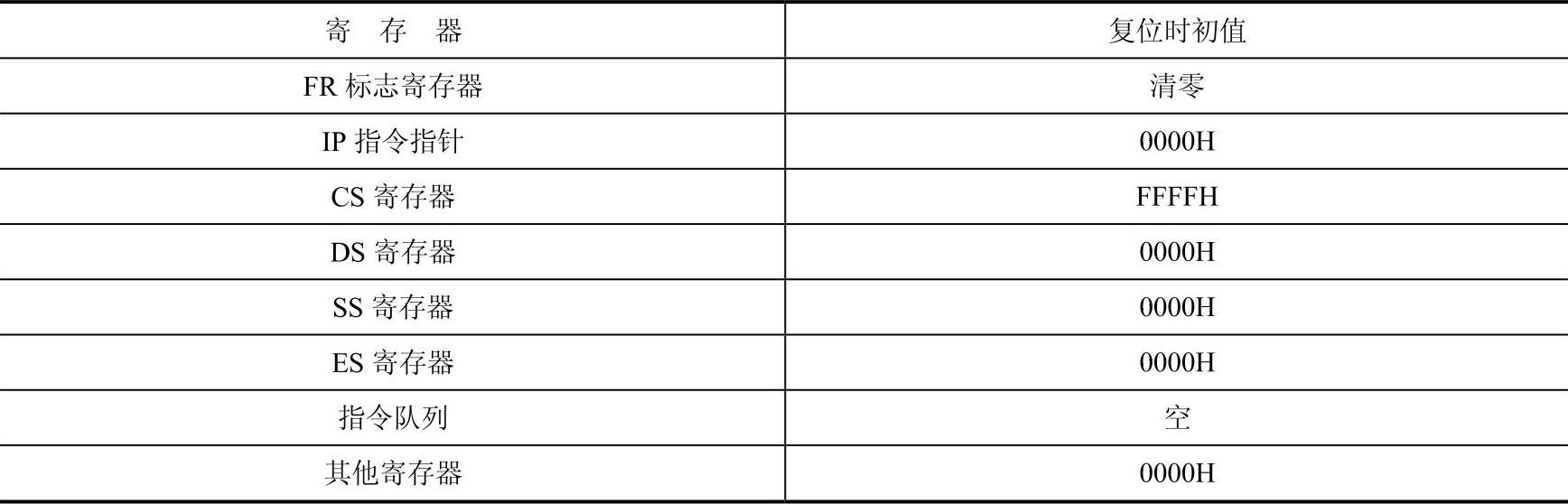

8086 CPU通过RESET引脚上的触发信号来执行系统复位和启动。当复位信号RESET至少持续4个时钟周期的高电平时,CPU结束当前操作,进入复位状态,并初始化内部寄存器,见表2-8。在复位后再重新启动,系统从FFFF0H开始执行指令。因此,一般在FFFF0H处存放一条无条件转移指令,转移到系统程序的入口处。这样,系统一旦启动,便自动进入系统程序。

表2-8 复位时寄存器初值

在复位时,由于标志寄存器被清零,其中断标志位也都被清零,屏蔽了所有从INTR引脚进入的可屏蔽中断请求。因而,系统程序在复位后,需要应用开中断指令STI来设置中断允许标志。

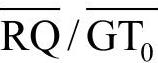

从图2-12可看出,在RESET变成高电平后,经过一个时钟周期,所有三态输出线被设置成高阻,并一直维持高阻状态,直到RESET信号回到低电平为止。置成高阻状态的三态输出线包括:AD15~AD0、A19/S6~A16/S3、 、

、 、

、 、

、 、

、 、

、 和INTA。另外有几条控制线在复位之后处于无效状态,但不浮空,它们是ALE、HLDA、

和INTA。另外有几条控制线在复位之后处于无效状态,但不浮空,它们是ALE、HLDA、 、

、 、QS0、QS1。

、QS0、QS1。

图2-12 8086复位操作的时序

2.最小模式系统的总线操作时序

8086 CPU为了要与存储器及I/O端口交换数据,需要对总线进行操作。按照数据传输方向,总线操作可分为总线读操作和总线写操作。总线读操作是CPU从存储器或I/O端口读取数据;总线写操作是CPU将数据写入存储器或I/O端口。

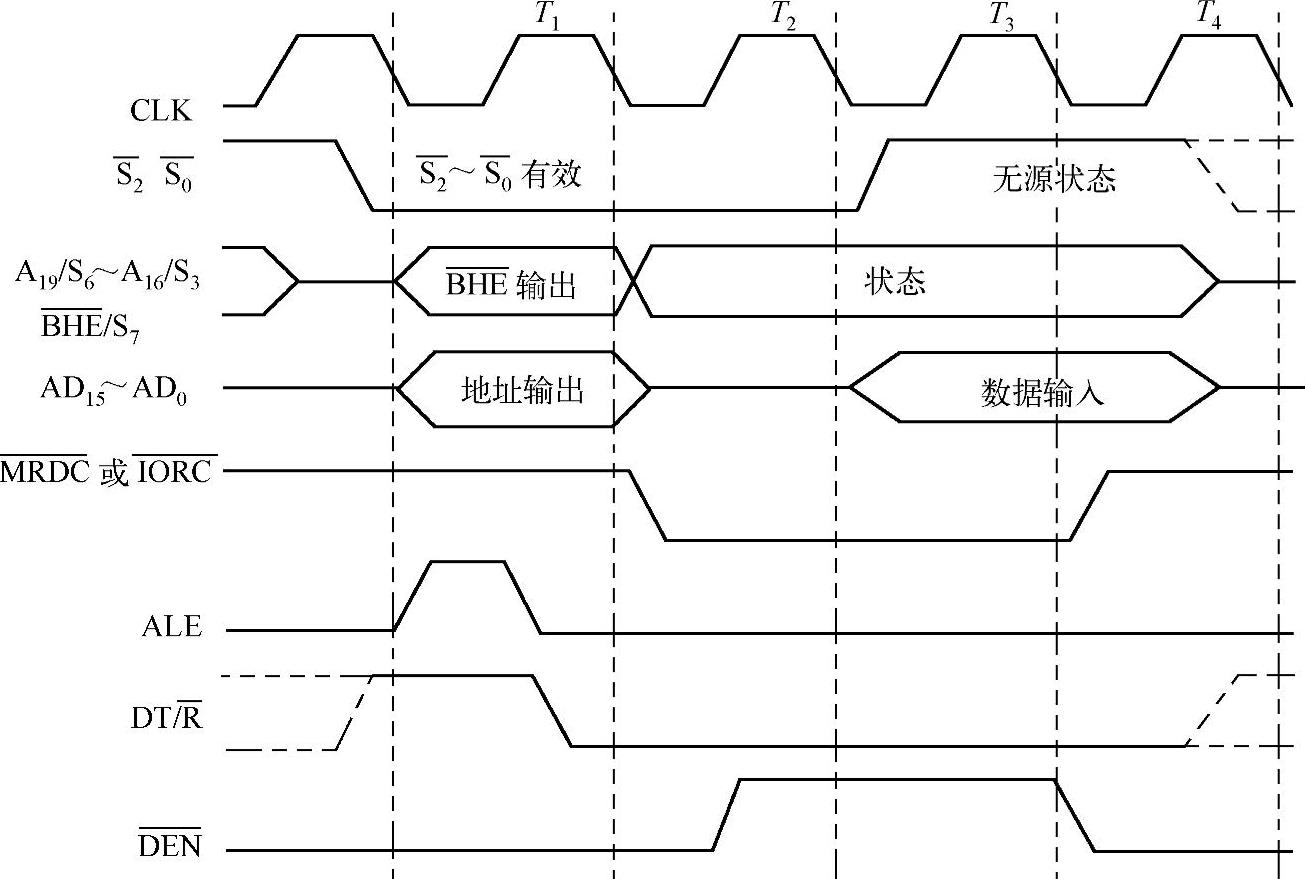

(1)总线读操作时序

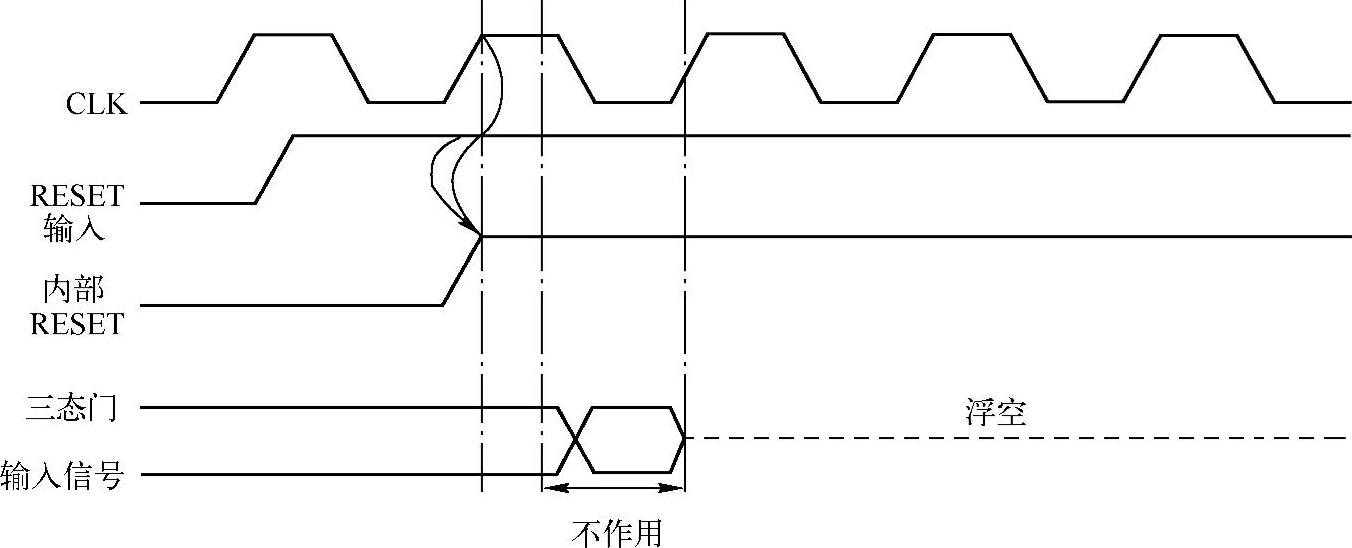

图2-13 8086最小模式读总线周期的时序

8086 CPU最小模式下的读周期时序如图2-13所示。一个最基本的总线读周期包含4个 状态,即T1、T2、T3、T4。在存储器和外设速度较慢时,要在T3之后插入一个或几个等待状态TW。

①T1状态。首先, 信号有效,指定CPU是读内存还是读I/O端口,其有效电平一直保持到整个总线周期结束。其次,CPU通过多路复用总线送出20位地址信号,高4位地址从A19/S6~A16/S3(地址/状态线)送出,低16位地址从AD15~AD0(地址/数据线)送出,指出操作对象的地址。同时,ALE有效,用作锁存器8282的选通信号,使地址锁存。在T1状态结束时,

信号有效,指定CPU是读内存还是读I/O端口,其有效电平一直保持到整个总线周期结束。其次,CPU通过多路复用总线送出20位地址信号,高4位地址从A19/S6~A16/S3(地址/状态线)送出,低16位地址从AD15~AD0(地址/数据线)送出,指出操作对象的地址。同时,ALE有效,用作锁存器8282的选通信号,使地址锁存。在T1状态结束时, 信号、地址信号均已有效。

信号、地址信号均已有效。 信号有效,作为奇地址存储体的选通信号,奇地址存储体中的信息总是通过高8位数据线传输的。系统中配有数据总线收发器8286时,T1状态使

信号有效,作为奇地址存储体的选通信号,奇地址存储体中的信息总是通过高8位数据线传输的。系统中配有数据总线收发器8286时,T1状态使 端输出低电平,表示本总线周期为读周期,用

端输出低电平,表示本总线周期为读周期,用 去控制8286接收数据。

去控制8286接收数据。

②T2状态。高4位地址/状态线A19/S6~A16/S3输出状态信息S6~S3,指出当前段寄存器及中断允许情况;低位地址/数据线AD15~AD0进入高阻状态,为读取数据作准备。 变成高电平,未赋予实际意义。

变成高电平,未赋予实际意义。 信号有效,表示要对存储器和I/O端口进行读操作,但只选通地址有效的存储单元和I/O端口,使之能读出数据。

信号有效,表示要对存储器和I/O端口进行读操作,但只选通地址有效的存储单元和I/O端口,使之能读出数据。 有效,总线收发器可以传输数据。

有效,总线收发器可以传输数据。

③T3状态。T3状态开始,若READY信号为低电平,表明存储器或外设速度较慢,则CPU在T3和T4状态之间再插入一个或几个TW状态。当READY信号为高电平时,CPU读取数据。在 的控制下,内存单元或I/O端口的数据通过数据收发器8286送到数据总线AD15~AD0上。S4、S3组合表明了当前访问的段寄存器。

的控制下,内存单元或I/O端口的数据通过数据收发器8286送到数据总线AD15~AD0上。S4、S3组合表明了当前访问的段寄存器。

④T4状态。CPU在T4状态和前一个状态交界的下降沿处采样数据。在T4状态的后半周期,数据从数据总线上撤除,各控制信号和状态信号线进入无效状态, 无效,总线收发器不工作,一个读总线周期结束。

无效,总线收发器不工作,一个读总线周期结束。

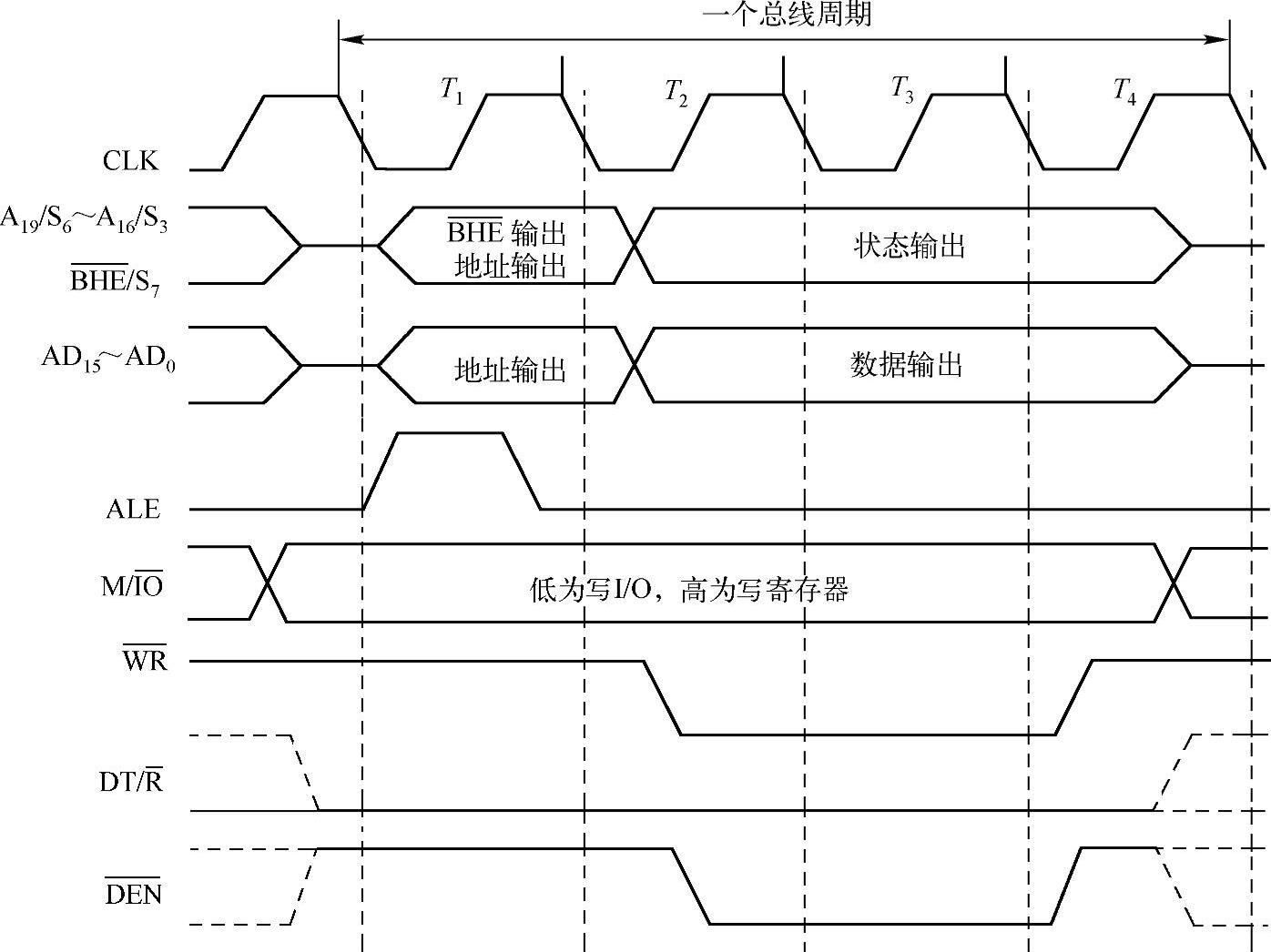

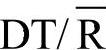

(2)总线写操作时序

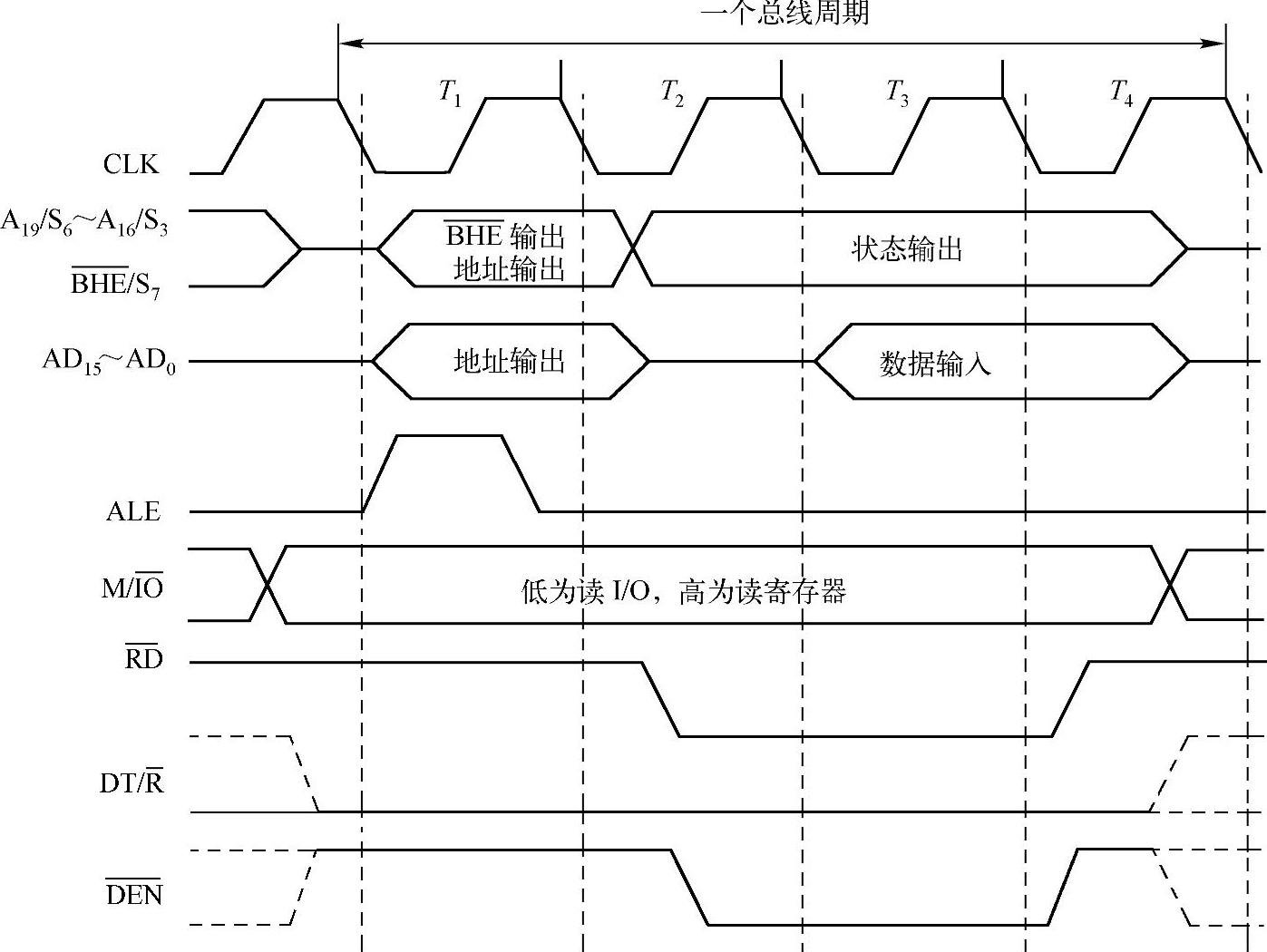

总线写操作时序是CPU往存储器或I/O端口写入数据的时序,和读操作一样,也包含4个状态。当存储器和外设的读/写速度比较慢时,在T3和T4状态之间,自动插入一个或几个用于等待的TW状态。8086最小模式写总线周期的时序如图2-14所示。

8086 CPU写总线周期时序与读总线周期时序有许多相同之处。

在T1状态, 信号有效,指定CPU是写内存还是写I/O端口,其有效电平一直保持到整个总线周期结束。CPU通过多路复用总线送出20位地址信号,地址锁存信号ALE有效,选存储体信号

信号有效,指定CPU是写内存还是写I/O端口,其有效电平一直保持到整个总线周期结束。CPU通过多路复用总线送出20位地址信号,地址锁存信号ALE有效,选存储体信号 有效,

有效, 变高电平,表示本总线周期为写周期。

变高电平,表示本总线周期为写周期。

在T2状态,地址撤销,S6~S3状态信号输出,数据从CPU送到数据总线AD15~AD0, 写信号有效;

写信号有效; 信号有效,作为数据总线收发器8286的选通信号。

信号有效,作为数据总线收发器8286的选通信号。

在T3状态,CPU采样READY线,若READY信号无效,插入一个到几个TW状态,到READY信号有效,存储器或I/O设备从数据总线上取走数据。(https://www.xing528.com)

在T4状态,从数据总线上撤销数据,各控制信号和状态信号变成无效; 信号变成高电平,总线收发器不工作。

信号变成高电平,总线收发器不工作。

下面对写总线周期与读总线周期时序不同之处加以说明:

①在T1状态, 为高电平,表示为写周期存储单元或I/O端口。

为高电平,表示为写周期存储单元或I/O端口。

图2-14 8086最小模式写总线周期的时序

②在T2状态,CPU向地址/数据总线AD15~AD0发送数据,信号保持到T4状态的中间,存储器或外设准备好即可从数据总线取走数据。

③写信号 在T2状态有效,维持到T4状态,写存储器或I/O端口。

在T2状态有效,维持到T4状态,写存储器或I/O端口。

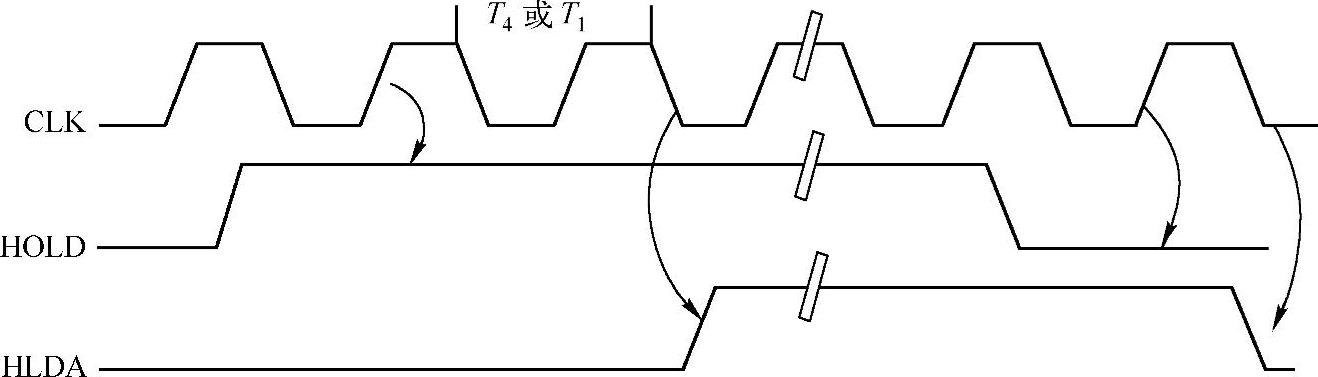

(3)最小模式下的总线请求信号与总线响应信号(见图2-15)

图2-15 总线请求和总线响应时序

在最小模式下,由CPU的HOLD引脚和HLDA引脚分别作为总线请求信号的输入引脚和总线响应信号的输出引脚。CPU之外的总线模块为了获得对总线的控制,需向CPU发出HOLD请求信号,等待CPU的应答。CPU在每个时钟周期的上升沿,检测HOLD引脚的信号,若为高电平,并且允许让出总线,则在总线周期的T4状态或者空闲状态T1之后的下一个时钟周期,CPU发出总线响应HLDA信号,让出总线,直到HOLD信号为低电平。CPU让出总线控制权后,地址线、数据线及控制信号 、

、 、

、 、

、 、

、 、

、 处于浮空状态,CPU和数据总线、地址总线以及控制总线中的上述控制信号断开联系。但ALE信号不浮空。

处于浮空状态,CPU和数据总线、地址总线以及控制总线中的上述控制信号断开联系。但ALE信号不浮空。

3.最大模式系统基本操作时序

(1)总线读操作时序

最大模式下,8086的总线读操作在逻辑上和最小模式下的读操作一样,但分析时序时,最大模式下要考虑CPU和总线控制器两者产生的信号。图2-16所示为最大模式下的读时序。

图2-16 8086 CPU最大模式下的总线读操作时序

①在T1状态,CPU通过AD15~AD0发出地址的低16位,高4位通过A19/S6~A16/S3发出,ALE有效,锁存地址。此外,总线控制器提供数据传输方向控制信号 。在T1状态,

。在T1状态, 进入低电平,总线周期执行读操作,一直维持到T4为止。

进入低电平,总线周期执行读操作,一直维持到T4为止。

②在T2状态,CPU输出状态S7~S3;在T2状态的时钟上升沿处, 低电平有效,根据

低电平有效,根据 、

、 、

、 的电平组合(参见表2-7)发出读信号

的电平组合(参见表2-7)发出读信号 或者

或者 ,送到存储器或I/O端口,去执行存储器读操作或I/O端口读操作,一直维持有效电平到T4。此外,地址/数据线为高阻状态,为输入数据作准备。

,送到存储器或I/O端口,去执行存储器读操作或I/O端口读操作,一直维持有效电平到T4。此外,地址/数据线为高阻状态,为输入数据作准备。

③在T3状态,存储单元或者I/O端口将数据送到数据总线上,CPU通过AD15~AD0接收数据, 、

、 、

、 全部进入高电平的无源状态,从T3一直维持到T4。和最小模式下的总线读操作类似,如果在T3状态开始时,READY仍为低电平无效,则在T3状态和T4状态之间插入一个或几个TW状态。

全部进入高电平的无源状态,从T3一直维持到T4。和最小模式下的总线读操作类似,如果在T3状态开始时,READY仍为低电平无效,则在T3状态和T4状态之间插入一个或几个TW状态。

④在T4状态,数据从总线上消失,状态信号引脚S7~S3进入高阻状态,而 、

、 、

、 则按照下一个总线周期的操作类型变化。

则按照下一个总线周期的操作类型变化。

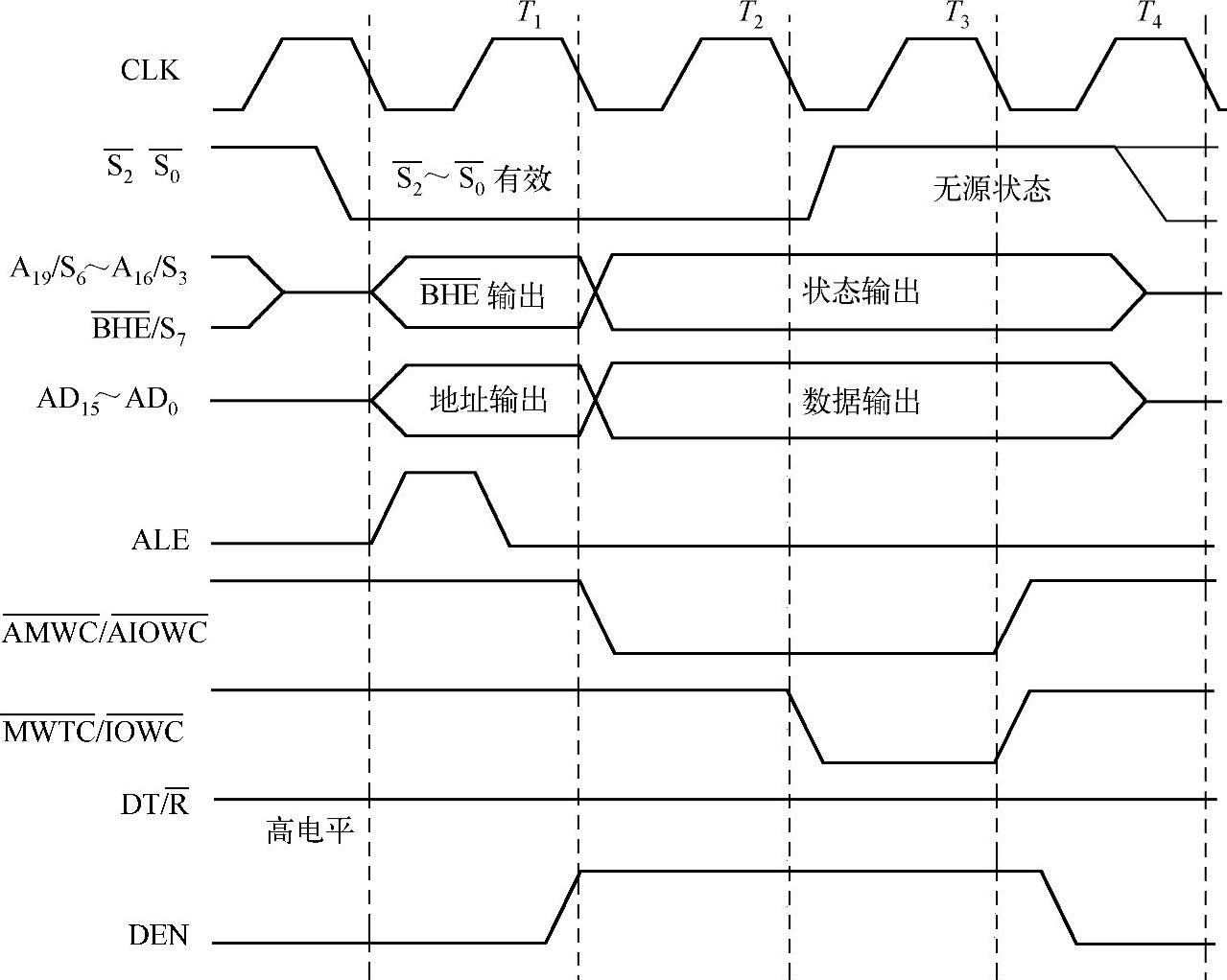

(2)总线写操作时序

最大模式下,CPU通过总线控制器为存储器或I/O端口提供了两组信号:一组是普通的存储器写信号 和普通的输入/输出端口写信号

和普通的输入/输出端口写信号 ;另一组是提前的存储器写信号

;另一组是提前的存储器写信号 和提前的输入/输出端口写信号

和提前的输入/输出端口写信号 。提前的写信号比普通的写信号提前一个时钟周期开始起作用。图2-17是最大模式下的总线写操作时序。

。提前的写信号比普通的写信号提前一个时钟周期开始起作用。图2-17是最大模式下的总线写操作时序。

①在T1状态,CPU通过AD15~AD0发出地址的低16位,高4位通过A19/S6~A16/S3发出,ALE有效,锁存地址。CPU还使数据总线高8位有效信号 进入有效电平。在T1状态,DT/R输出高电平,表示本总线周期进行写操作。

进入有效电平。在T1状态,DT/R输出高电平,表示本总线周期进行写操作。

图2-17 8086 CPU最大模式下的总线写操作时序

②在T2状态,CPU把数据送到数据总线上。总线控制器使DEN输出高电平,数据总线收发器得到允许。在DEN输出高电平的同时,提前的存储器写信号A 或者提前的I/O端口写信号

或者提前的I/O端口写信号 也为低电平,并且一直维持到T4。

也为低电平,并且一直维持到T4。

③在T3状态。总线控制器使存储器写信号MWTC或I/O端口写信号IOWC成为低电平,并且一直维持到T4,可见,两个提前的写信号 和A

和A 比

比 和

和 提前了整整一个时钟周期,这样,一些较慢的I/O端口或者存储器芯片就可以得到一个额外的时钟周期进行写操作。在T3状态,

提前了整整一个时钟周期,这样,一些较慢的I/O端口或者存储器芯片就可以得到一个额外的时钟周期进行写操作。在T3状态, 、

、 、

、 全部进入高电平,总线进入无源状态,从而为启动下一个总线周期做好准备。当READY信号滞后T3状态时,也会在T3状态和T4状态之间插入一个或几个TW。

全部进入高电平,总线进入无源状态,从而为启动下一个总线周期做好准备。当READY信号滞后T3状态时,也会在T3状态和T4状态之间插入一个或几个TW。

④在T4状态,写信号A 、

、 、

、 、

、 都被撤销,

都被撤销, 、

、 、

、 则按照下一个总线周期的操作类型产生变化。数据总线收发器允许信号DEN也变为低电平,使数据总线收发器停止工作。其他引脚处于高阻状态。

则按照下一个总线周期的操作类型产生变化。数据总线收发器允许信号DEN也变为低电平,使数据总线收发器停止工作。其他引脚处于高阻状态。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。