1.存储器地址空间和数据存储格式

(1)存储器地址空间

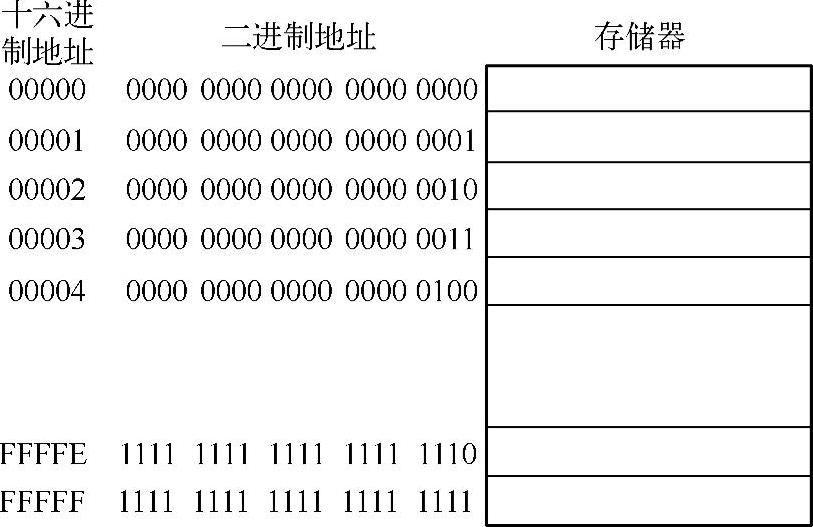

8086 CPU具有20条地址总线,可寻址的存储空间容量为1MB,地址范围为0~220−1(16进制表示为00000H~FFFFFH),如图2-4所示。

在8086存储器中,允许字从任何地址开始存放。从偶地址开始存放的字,称为规则字或对准字,从奇地址开始存放的字,称为非规则字或非对准字。规则字的存取可在一个总线周期内完成,非规则字的存取需要两个总线周期。

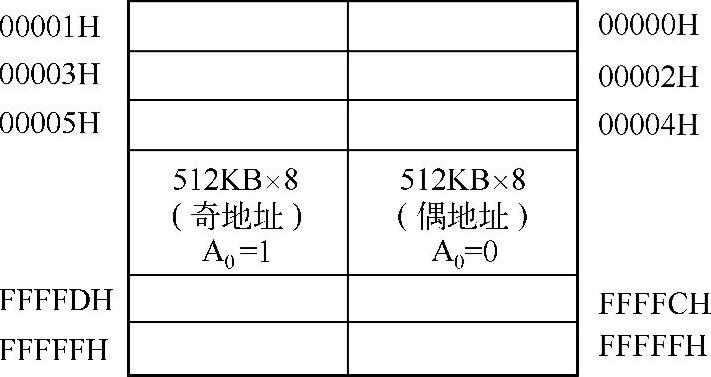

8086系统将其内存储器分成两个512KB存储体,如图2-5所示。一部分叫偶存储体,其中内存单元的地址码都是偶数,如00000H、00002H等,该存储体的数据总线对应接数据总线的低8位;另一部分叫奇存储体,其中内存单元的地址码都是奇数,如00001H、00003H等,该存储体的数据总线对应接CPU数据总线的高8位。每个存储体有19条地址线,两个存储体的全部地址线对应与CPU的19条地址总线A19~A1相连。CPU的地址线A0作为偶存储体的片选信号,当A0=0时,表示访问偶地址存储体;当A0=1时,表示访问奇地址存储体。8086专门设置了—个高位有效控制信号 ,

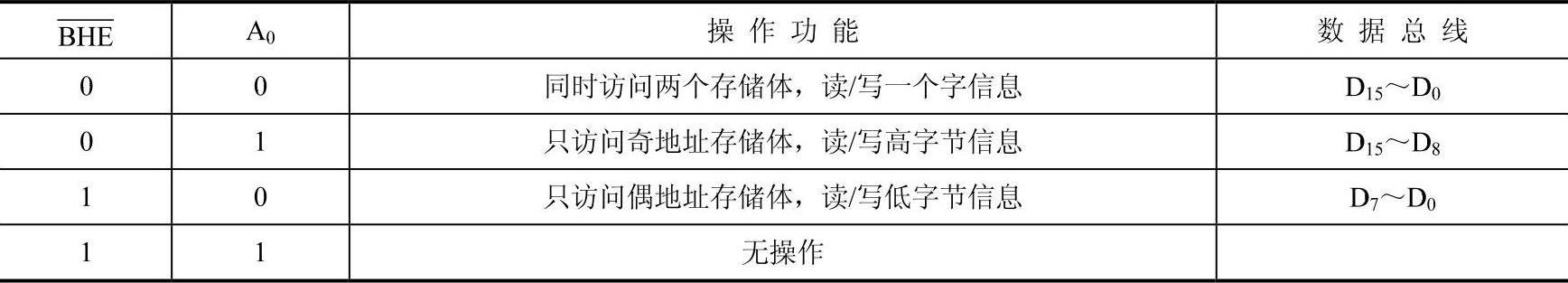

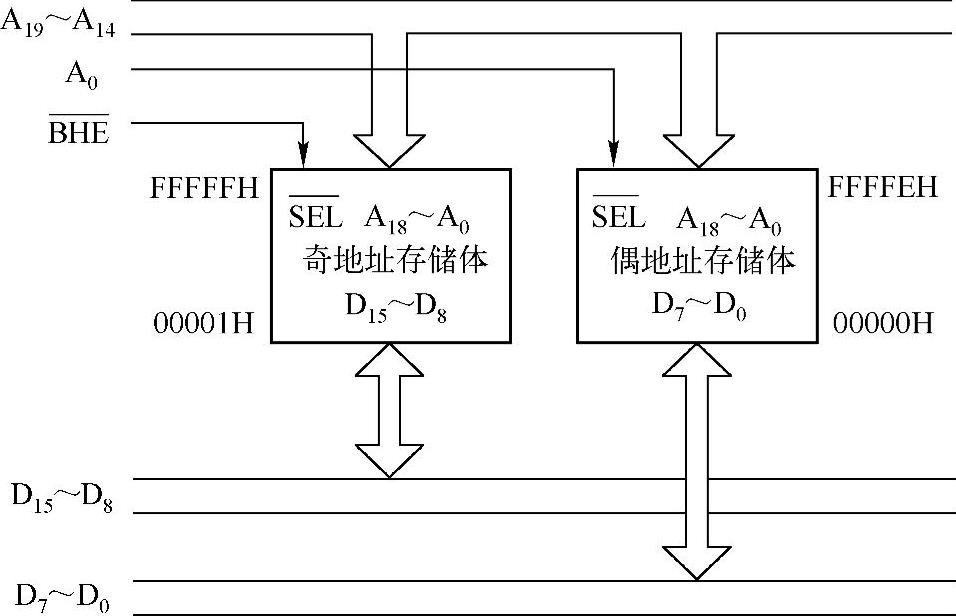

, 和A0(AD0)不同组合状态所代表的含义见表2-3。两个存储体与CPU总线之间的连接及8086存储器结构如图2-6所示。

和A0(AD0)不同组合状态所代表的含义见表2-3。两个存储体与CPU总线之间的连接及8086存储器结构如图2-6所示。

图2-4 8086 CPU的存储器组织图

图2-5 8086 CPU存储器的两个512KB存储体

表2-3 BHE和A0代码组合对应的存取操作

图2-6 8086 CPU与存储器的连接图

8086的奇地址存储体的片选端 受控于B

受控于B 信号,偶地址存储体的片选端SEL受控于地址线A0。

信号,偶地址存储体的片选端SEL受控于地址线A0。

(2)数据存储格式

8086有16根数据线,可以进行l6位或8位运算。存储器内按字节进行组织,两个相邻的字节为一个字,一个字中的每个字节都有一个字节地址,若存放的数据以字节为单位,则数据在存储器中按顺序排列存放;若存放的数据为一个字,则将其低字节存于低地址,高字节存于高地址,并以低地址作为该字的地址。字和字节中各位的编号方法是最低位为0,即D0;字节的最高位编号为7,即D7;字的最高位编号为15,即D15。

8086读或写一个字节的指令,需要—个总线周期。访问一个偶地址字的指令,用D15~D0的16条数据总线可一次访问成功,即需要一个总线周期。而访问一个奇地址字的指令,则需要两个总线周期。第一总线周期用D15~D8访问奇存储体的低字节,第二总线周期用D7~D0访问偶存储体的高字节。故为了提高对数据字的访问速度,应将数据字的低字节放在偶存储体中,使数据字的地址码为偶数。

2.存储器的分段

8086 CPU有20条地址线,能寻址外部存储空间为1MB,8086 CPU内部所有的六个寄存器均为16位,用任一16位地址寄存器给外部存储器提供地址,只能提供64KB的寻址空间,达不到1MB地址的寻址范围。这六个16位地址寄存器分别为BX、BP、SI、DI、SP、IP。

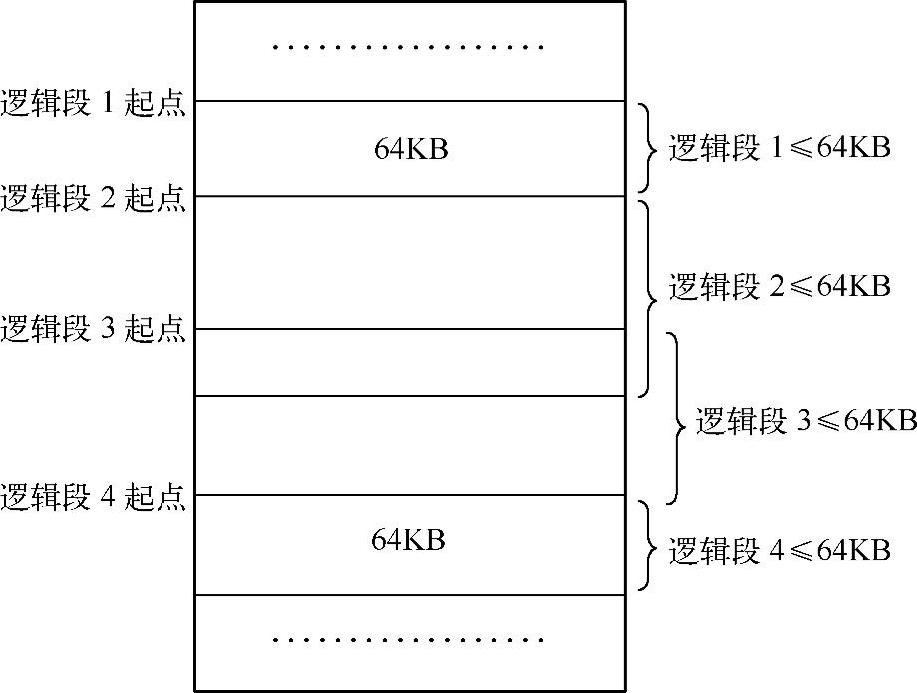

为了使8086 CPU能寻址到外部存储器1MB空间,把整个存储空间分出许多逻辑段,每段不超过64KB。段与段能连续排列,也能部分重叠,或完全重叠,或断续排列,段数没有限制。一个存储单元可以只属于某一段,也可以属于多个互相重叠的段,最终将寻址范围扩大到1MB。图2-7所示为一种存储空间分段的示意图。

在1MB的存储空间中,每个存储单元的实际地址编码称为该单元的物理地址,用PA表示。一个段的起始地址的高16位自然数为其段地址。在段内的每个存储单元,可以用相对于本段的起始地址的偏移量来表示,这个偏移量称为段内偏移地址,也称为有效地址EA。

(https://www.xing528.com)

(https://www.xing528.com)

图2-7 8086存储空间分段示意图

3.存储器地址

8086在访问存储器时管理1MB的内存空间,其20根地址线都有效,在访问外设时管理64KB的I/O端口空间,仅16根地址线有效。在把1MB的存储空间分成若干个逻辑段以后,对一个段内的任意存储单元,可用两部分地址来描述,一部分为段地址,另一部分为段内偏移地址EA,段地址和段内偏移地址都是无符号的16位二进制数,常用4位十六进制数表示。这种方法表示的存储器单元的地址称为逻辑地址。逻辑地址的表示格式为“段地址:偏移地址”。一个存储单元用逻辑地址表示后,CPU对该单元的寻址就应提供两部分地址:段地址和段内有效地址。段地址和段内有效地址分别由以下段寄存器提供。

CS—提供当前代码(程序)段的段地址。

DS—提供当前数据(程序)段的段地址。

ES—提供当前附加数据段的段地址。

SS—提供当前堆栈段的段地址。

BX、BP、SI、DI—CPU对存储器进行数据读/写操作时,寻址方式向存储器提供段内偏移地址。

SP—堆栈操作时,提供堆栈段的段内偏移地址。

IP—CPU取指令时,提供所取指令代码所在单元的偏移地址。

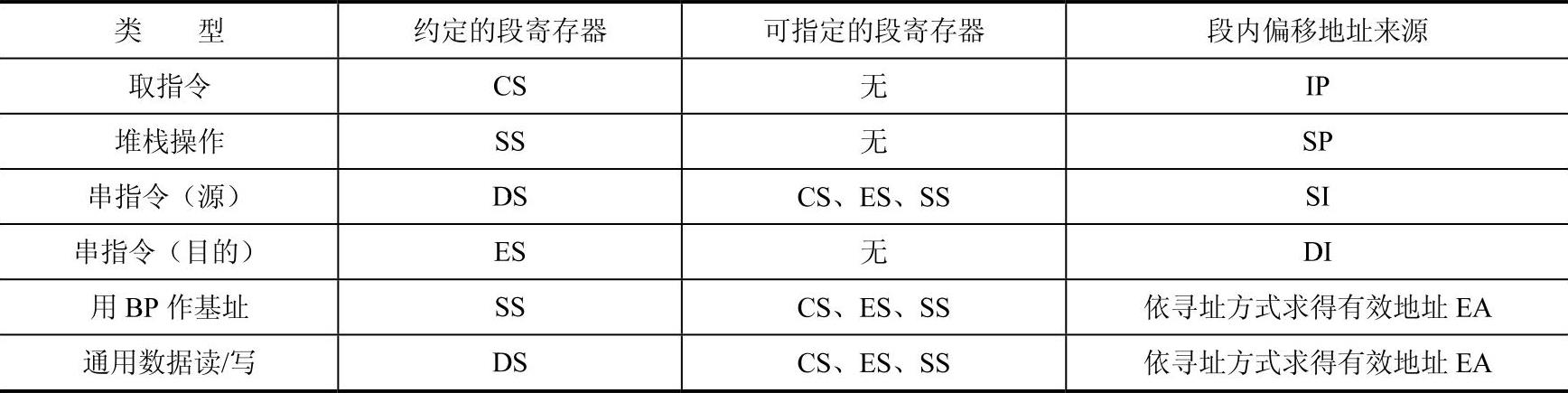

当访问存储单元时,由于操作数的类型不同,逻辑地址的来源也不一样,其关系见表2-4。

表2-4 操作类型的段基地址和偏移地址的来源关系

其中,可指定段地址是由指令加一字节的段超越前缀来实现,如果用默认段地址寄存器则无此前缀。如指令“MOV AX,[SI]”表示使用默认段地址DS,“MOV AX,ES:[SI]”表示使用指定段地址ES。

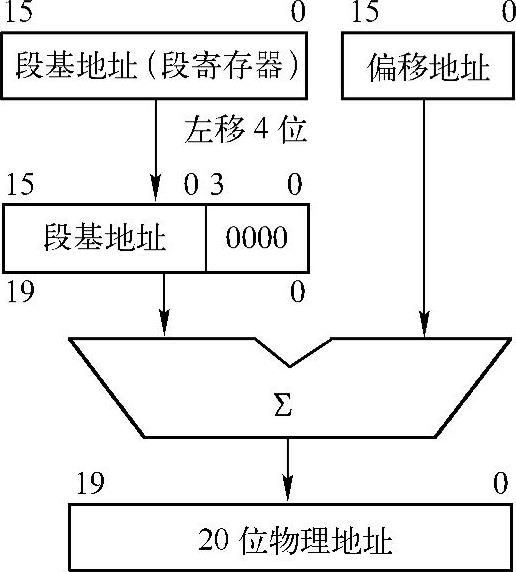

逻辑地址到物理地址的转换由BIU中的20位的地址加法器自动完成,如图2-8所示。实际上物理地址是段基地址左移4位加偏移地址形成的,其计算公式为 物理地址(PA)=段基地址×10H+偏移地址(有效地址EA)

(2-1)

例2-1 设(CS)=7648H,(IP)=423H,求其物理地址。

解:(CS)=7648H为段基地址,(IP)=423H为段内有效地址,根据式(2-1),得物理地址(PA)=7648H×10H+423H=76480H+423H=768A3H

所以,求得的物理地址:PA=768A3H。

图2-8 物理地址生成示意图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。