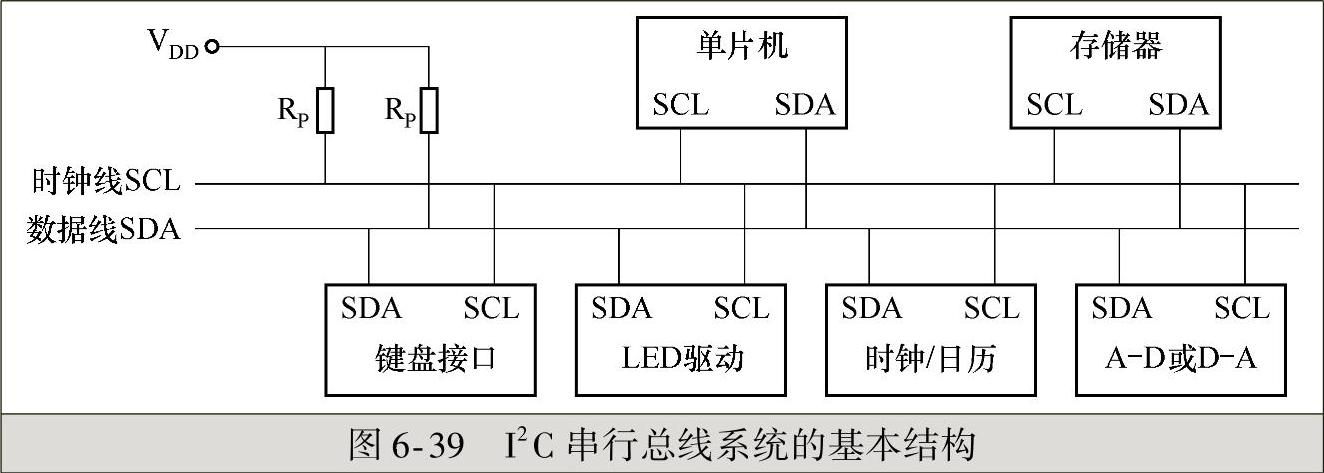

I2C总线(Inter IC BUS),是Philips公司推出的使用广泛、很有发展前途的芯片间串行数据传输总线,采用两线制实现全双工同步数据传送。I2C总线只有两条信号线,一条是数据线SDA(Serial Data Line),另一条是时钟线SCL(Serial Clock Line)。两条线均双向传送,所有连到I2C上器件的数据线都接到SDA线上,各器件时钟线均接到SCL线上。I2C系统基本结构如图6-39所示。I2C总线单片机直接与I2C接口的各种扩展器件(如存储器、I/O芯片、A-D、D-A、键盘、显示器、日历/时钟)连接。I2C总线已成为广泛应用的工业标准之一。

图6-39 I2C串行总线系统的基本结构

I2C总线是一个多主机总线,总线上可以有一个或多个主机(或称主控制器件),总线运行由主机控制。主机是指启动数据的传送(发起始信号)、发出时钟信号、发出终止信号的器件。通常,主机由单片机或其他微处理器担任。被主机访问的器件叫作从机(或称从器件),它可以是其他单片机,或者其他外围芯片,如A-D、D-A、LED或LCD驱动、串行存储器芯片。

I2C总线支持多主和主从两种工作方式。多主方式下,I2C总线上可以有多个主机,I2C总线需通过硬件和软件仲裁来确定主机对总线的控制权。主从工作方式时,系统中只有一个主机,总线上的其他器件均为从机(具有I2C总线接口),只有主机能对从机进行读写访问,因此,不存在总线的竞争等问题。在主从方式下,I2C总线的时序可以模拟,I2C总线的使用不受主机是否具有I2C总线接口的制约。

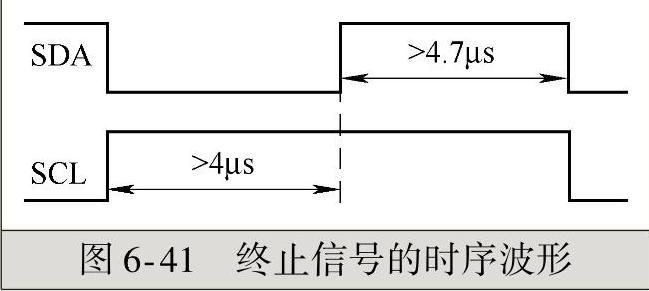

MCS-51系列单片机本身不具有I2C总线接口,可以用其I/O口线模拟I2C总线。常见I2C器件的标识码见表6-15。

表6-15 常见I2C器件的标识码

1 单片机的I2C总线扩展的设计

MCS-51系列单片机没有I2C总线接口,只能采用虚拟I2C总线方式,并且只能用于主从系统。虚拟I2C总线接口利用MCS-51单片机的I/O口线作为数据线SDA和时钟线SCL,通过软件延时实现I2C总线传输数据的时序要求。

(1)I2C总线数据传送的模拟

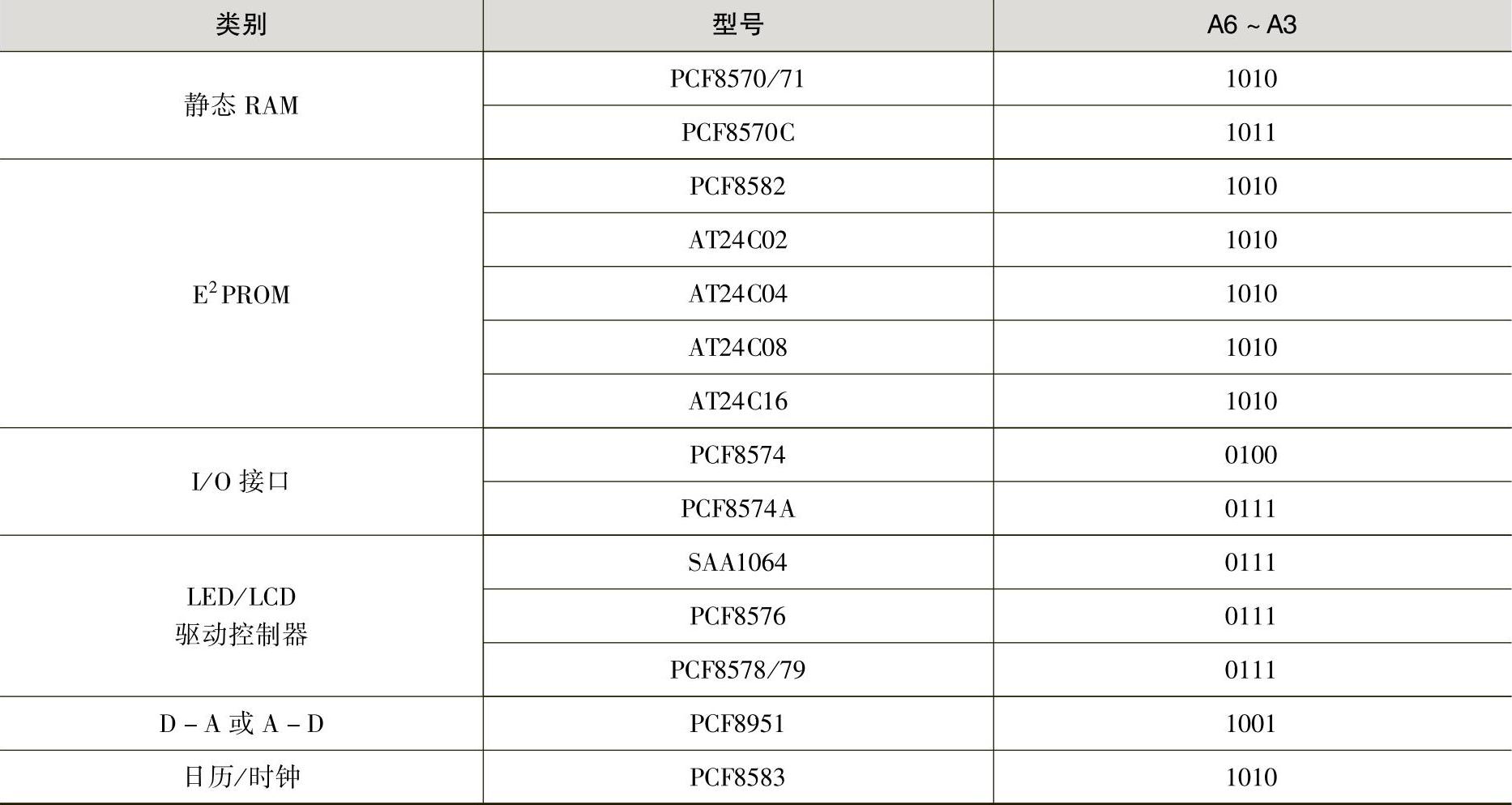

1)起始信号S:对一个新的起始信号,要求起始前总线空闲时间大于4.7μs,而对一个重复的起始信号,要求建立时间也需大于4.7μs。如图6-40所示的起始信号的时序波形在SCL高电平期间SDA发生负跳变,该时序波形适用于数据模拟传送中任何情况下的起始操作。起始信号到第1个时钟脉冲的时间间隔应大于4.0μs。系统晶振频率为6MHz,机器周期为2μs。

图6-40 起始信号的时序波形

START:SETB SDA;SDA=1

SETB SCL;SCL=1

NOP;SDA=1保持>4.7μs

NOP

CLR SDA;SDA=0

NOP;保持4μs

NOP

CLR SCL;SCL=0

RET

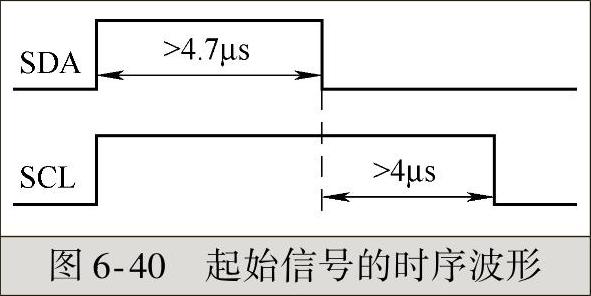

2)终止信号P:在SCL高期间SDA发生正跳变,终止信号P的波形如图6-41所示。

STOP:CLR SDA;SDA=0

SETB SCL;SCL=1

NOP;终止信号建立时间>4μs

NOP

SETB SDA;SDA=1,保持>4.7μs

NOP

NOP

图6-41 终止信号的时序波形

CLR SCL;SCL=0

CLR SDA;SDA=0

RET

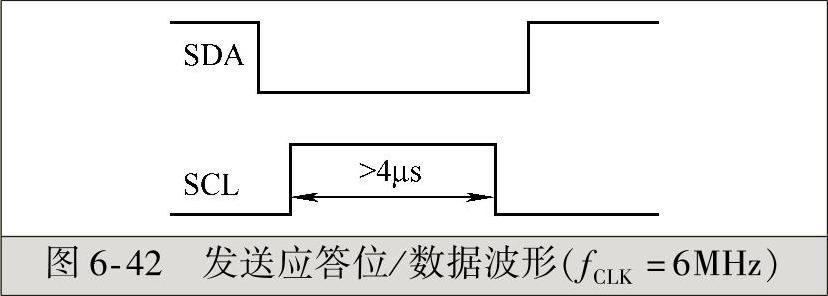

3)发送应答位/数据0:在SDA低电平期间SCL发生一个正脉冲,波形如图6-42所示。

图6-42 发送应答位/数据波形(fCLK=6MHz)

ACK:CLR SDA;SDA=0

SETB SCL;SCL=1

NOP;4μs

NOP

CLR SCL;SCL=0

SETB SDA;SDA=1

RET

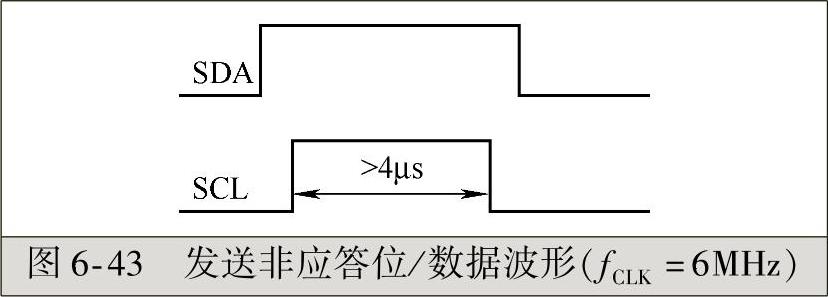

4)发送非应答位/数据1:在SDA高电平期间SCL发生一个正脉冲,时序波形如图6-43所示。

图6-43 发送非应答位/数据波形(fCLK=6MHz)

NACK:SETB SDA;SDA=1(https://www.xing528.com)

SETB SCL;SCL=1

NOP;两条NOP指令为4μs

NOP

CLR SCL;SCL=0

CLR SDA;SDA=0

RET

(2)I2C总线模拟通用子程序

I2C总线操作中除基本的起始信号、终止信号、发送应答位/数据0和发送非应答位/数据1外,还需要有应答位检查、发送1字节、接收1字节。

1)应答位检查子程序:在应答位检查子程序CACK中,设置了标志位F0,当检查到正常应答位时,F0=0,否则F0=1。

CACK:SETB P1.2;SDA为输入线,SDA=1

SETB P1.3;SCL=1,使SDA引脚上的数据有效

CLR F0;预设F0=0

MOV C,P1.2;读入SDA线的状态

JNC CEND;应答正常,转CEND

SETB F0;当SDA=1时,应答不正常,F0=1

CEND:CLR P1.3;当SDA=0时,子程序结束,使SCL=0

RET

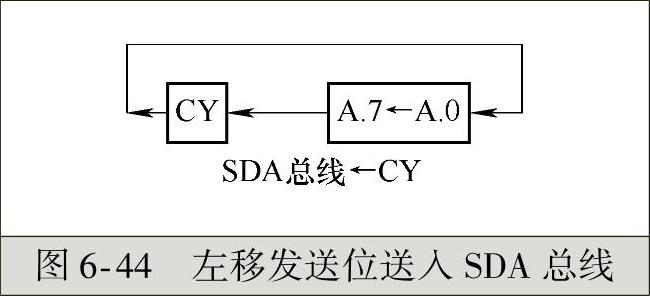

2)发送1字节数据子程序:模拟I2 C数据线SDA发送1字节数据的子程序,调用本子程序前,先将欲发送的数据送入累加器A中,如图6-44所示。

图6-44 左移发送位送入SDA总线

W1BYTE:MOV R6,#08H;8位数据长度送入R6中

WLP:RLC A;A左移,发送位进入C

MOV P1.2,C;将发送位送入SDA总线

SETB P1.3;SCL=1,使SDA引脚上的数据有效

NOP

NOP

CLR P1.3;仅当SCL=0时,SDA线上数据变化

DJNZ R6,WLP

RET

3)接收1字节数据子程序:模拟从I2 C的数据线SDA读取1字节数据的子程序,并存入R2中。

R1BYTE:MOV R6,#08H;8位数据长度送入R6中

RLP:SETB SDA;置SDA数据线为输入方式

SETB SCL;当SCL=1时,使SDA数据线上的数据有效

MOV C,SDA;读入SDA引脚状态

MOV A,R2

RLC A;将C读入A

MOV R2,A;将A存入R2

CLR SCL;当SCL=0时,SDA线上数据变化

DJNZ R6,RLP;8位接收完吗?未完,继续接收数据

RET;接收完,返回

2 数据传送格式使用注意事项

1)无论何种数据传送格式,寻址字节都由主机发出,数据字节的传送方向则遵循寻址字节中的方向位规定。

2)寻址字节只表明了从机的地址及数据传送方向。从机内部的n个数据地址,由器件设计者在该器件的I2C总线数据操作格式中,指定第一个数据字节作为器件内的单元地址指针,且设置地址自动加减功能,以减少从机地址的寻址操作。

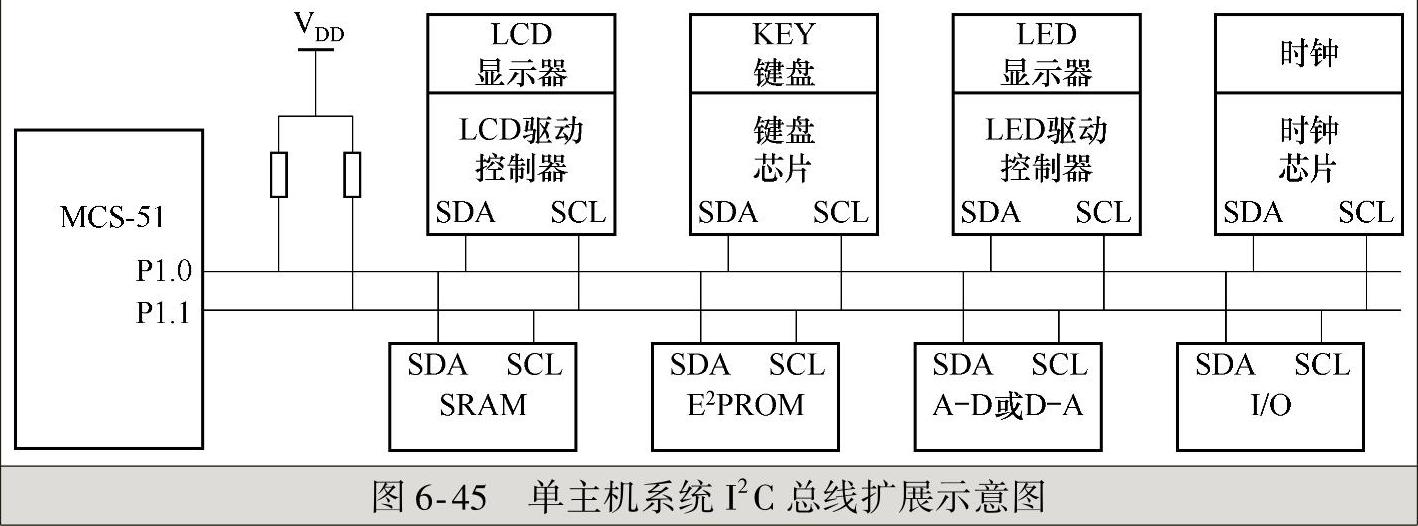

图6-45 单主机系统I2C总线扩展示意图

3)每个字节传送都必须有应答信号相随。

4)从机在接收到起始信号后都必须释放数据总线,使其处于高电平,以便主机发送从机地址。

单主机系统I2C总线扩展示意图如图6-45所示。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。