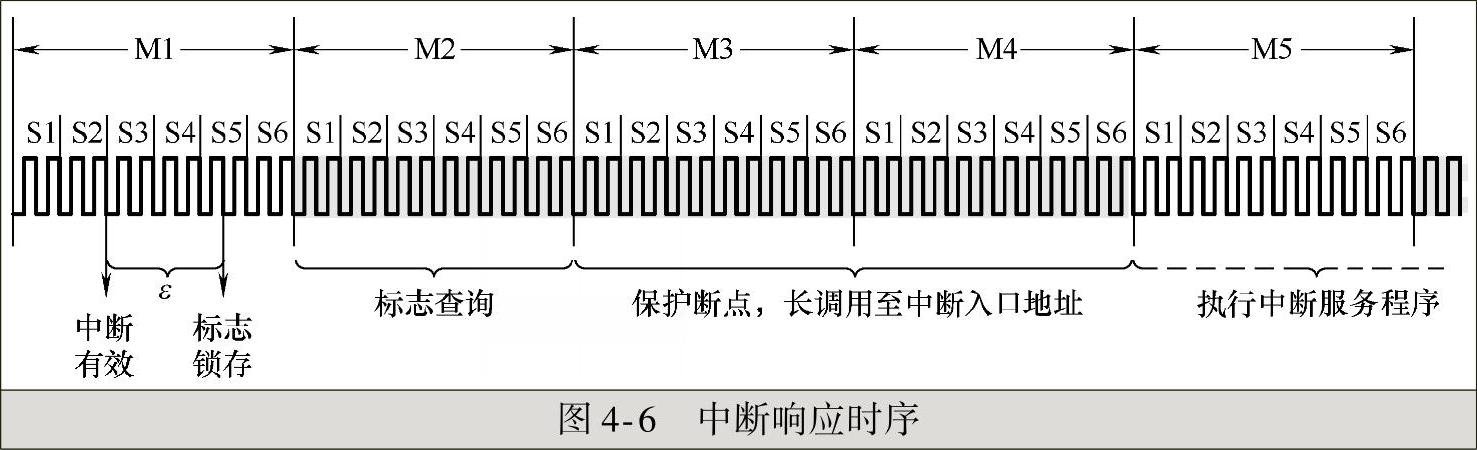

中断响应时间指的是从中断源发出中断请求,到CPU响应中断需要经历的时间。中断响应时序如图4-6所示。在单片机的实时控制系统中,为了满足控制速度的要求,需要明确知道CPU响应中断所需的时间。

图4-6 中断响应时序

中断响应(从标志置1到进入相应的中断服务)至少需要3个完整的机器周期。在一个单一中断系统中,MCS-51的CPU响应外部中断时间需要3~8个机器周期。

假定某中断在图4-6中M1周期的S5P2前生效,在S5P2期间,其中断请求被CPU查询到,并将相应的标志位置1。若下一个机器周期M2恰好是当前指令的最后一个机器周期,且该指令不是RET、RETI或访问IE、IP的指令,CPU便可以在后面的两个机器周期M3和M4里执行硬件LCALL指令,在M5周期将转入相应中断入口地址执行中断服务程序。

可见,MCS-51的中断响应时间(从中断标志位置1到进入相应的中断服务程序)至少需要3个完整的机器周期。(https://www.xing528.com)

若发生如下情况,就要增加中断响应等待时间:

1)若标志查询周期不是正在执行指令的最后机器周期,需增加1~3个机器周期,因为MCS-51指令系统中,执行时间最长的乘法、除法指令(MUL和DIV)也只需要4个机器周期。

2)若标志查询周期恰逢CPU执行RET、RETI或访问IE、IP指令,而这类指令之后又紧跟着MUL或DIV指令,则需多用1个机器周期完成正在执行的指令,再加上执行MUL或DIV指令需用4个机器周期。所以在这种情况下,需要附加的等待时间不会超过5个机器周期。

由此可见,对于没有嵌套的单级中断,响应时间为3~8个机器周期。若CPU正在响应同级或高级中断,则所需要的附加等待时间取决于正在执行的中断服务程序的长短,中断响应时间不确定。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。