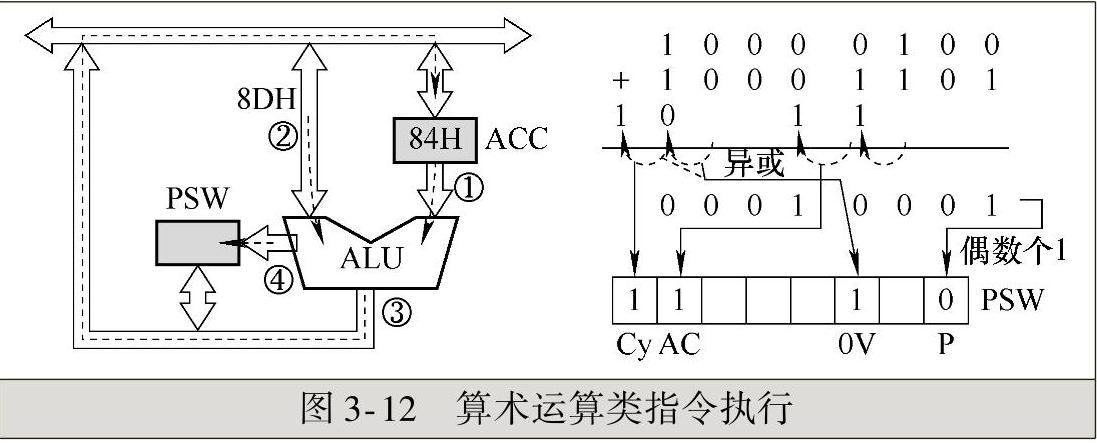

算术运算类指令主要是对8位无符号数进行算术操作。算术运算类指令有加、减、乘、除法指令,增1和减1指令,十进制调整指令,共24条。这类指令会影响PSW的有关位,对这类指令要特别注意正确地判断结果对标志位的影响,如图3-12所示。使用时应注意判断对哪些标志位(Cy、OV、AC、P)产生影响。

图3-12 算术运算类指令执行

这些指令分别将工作寄存器中的数、内部RAM单元中的数、以Ri内容为地址中的数或8位二进制立即数和累加器A中的数相加,并将和存放在A中。若相加时第3位或第7位有进位,则分别将AC、Cy标志位置1,否则为0。

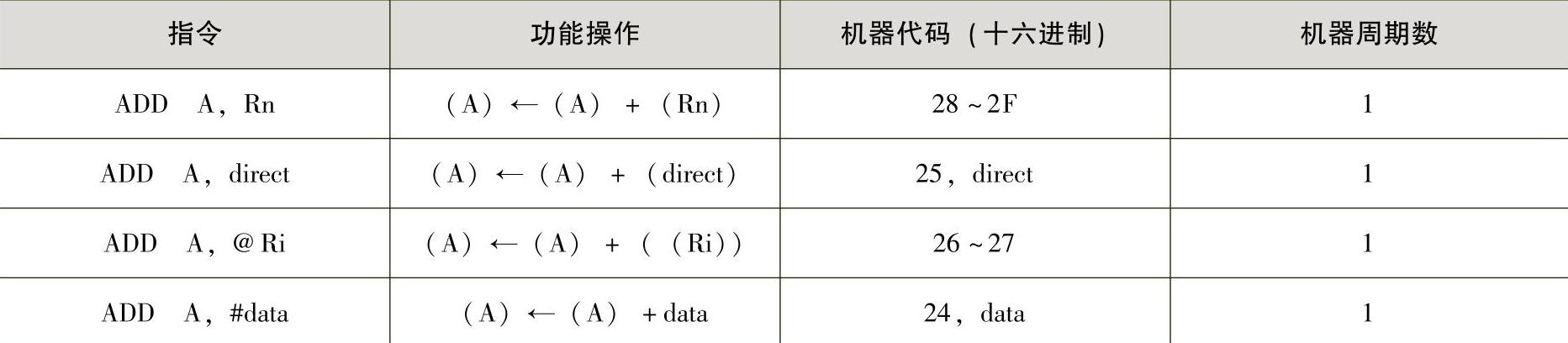

1 不带进位的加法指令(4条)

指令助记符为ADD,第一操作数都是A,第二操作数有4种寻址方式。

8位加法指令的一个加数总是来自累加器A,而另一个加数可由寄存器寻址、直接寻址、寄存器间接寻址和立即数寻址等不同的寻址方式得到。加的结果总是放在累加器A中。使用本指令时,要注意累加器A中的运算结果对各个标志位的影响:

1)如果位7有进位,则进位标志Cy置1,否则Cy清0。

2)如果位3有进位,辅助进位标志AC置1,否则AC(AC为PSW寄存器中的一位)清0。

3)如果位6有进位,而位7没有进位,或者位7有进位,而位6没有进位,则溢出标志位OV置1,否则OV清0。和的D7、D6位同时有进位或同时无进位时,OV=0;D7、D6位只有一个有进位时,OV=1。可表示为(OV)=(D7进位)+(D6进位)。

不带进位C的加法指令、功能操作、机器代码和执行机器周期数,见表3-7。

表3-7 不带进位C的加法指令、功能操作、机器代码和执行机器周期数

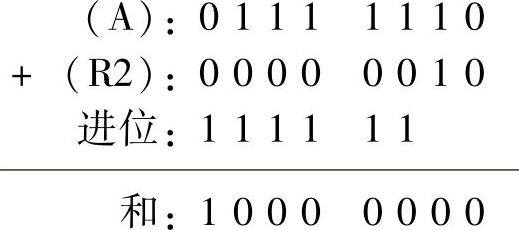

例3-14:假设(A)=7EH,(R2)=02H,执行指令ADD A,R2的运算过程如下所示。

运算结果为:(A)=80H,(Cy)=0,(AC)=1,(OV)=1(因为D7无进位、D6均有进位),(P)=1。当把两个操作数看作是无符号数时,虽然OV=1,但运算结果是正确的。

当把两个操作数看作是带符号数时,由于(OV)=1,表示结果产生溢出。因为当把两个操作数7EH、02H看作是带符号数时,对应的十进制数分别是+126和+2,相加结果应为+128,超出了8位二进制补码允许范围,所以产生溢出。结果为10000000B,按补码表示方法,这是一个负数,两个正数相加不可能变为负数,所以结果是错误的。

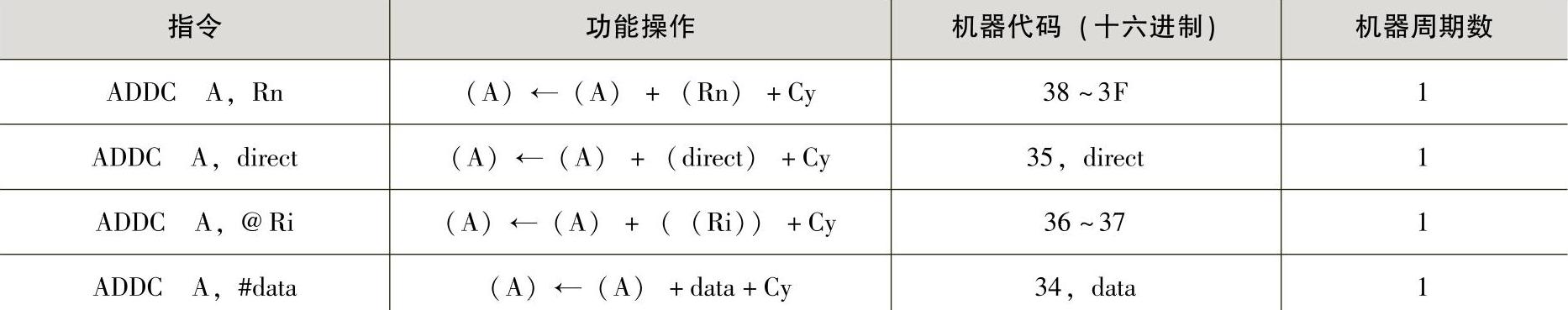

2 带进位的加法指令(4条)

指令助记符为ADDC,比ADD多了加Cy位的值(之前指令留下的Cy值),主要用于多字节的加法运算,结果也送A,影响AC、Cy、OV、P位。这些指令执行后,累加器A中内容为“和”。若相加时第3位或第7位有进位,则分别将AC、Cy标志位置1,否则为0。

指令的功能是把源操作数与累加器中的数据以及进位标志Cy的值相加并将相加结果送入累加器中。执行时,产生程序状态字PSW中标志位的情况与不带进位加法指令相同。值得注意的是,指令中所加的Cy值是在指令执行前形成的,而不是在指令执行过程中形成的。多字节相加:低字节用ADD指令,高字节用ADDC指令。

1)如果位7有进位,则进位标志Cy置1,否则Cy清0。

2)如果位3有进位,则辅助进位标志AC置1,否则AC清0。

3)如果位6有进位而位7没有进位,或者位7有进位而位6没有进位,则溢出标志OV置1,否则标志OV清0。

带进位C的加法指令、功能操作、机器代码和执行机器周期数见表3-8。

表3-8 带进位C的加法指令、功能操作、机器代码和执行机器周期数

例3-15:在片内RAM的31H、30H中存有双字节数(高在31H、低在30H中),编程把该双字节数与R2中单字节数相加,和存储在片内RAM的40H单元开始的空间中(低位在先)。

MOV R0,#30H;置被加数地址指针首址

MOV R1,#40H;置和地址指针首址

MOV A,@R0;取被加数低字节

ADD A,R2;低字节相加,并产生进位Cy

MOV @R1,A;存和的低字节

INC R0;地址指针增1,指向31H

INC R1;地址指针增1,指向41H

MOV A,@R0;取被加数的高字节

ADDC A,#0;高字节与进位Cy相加,产生新的进位

MOV @R1,A;存和中字节

INC R1;地址指针增1,指向42H

MOV A,#0;

ADDC A,#0;把高位的进位Cy转到A中

MOV @R1,A;存和的高字节,和可能为三字节数

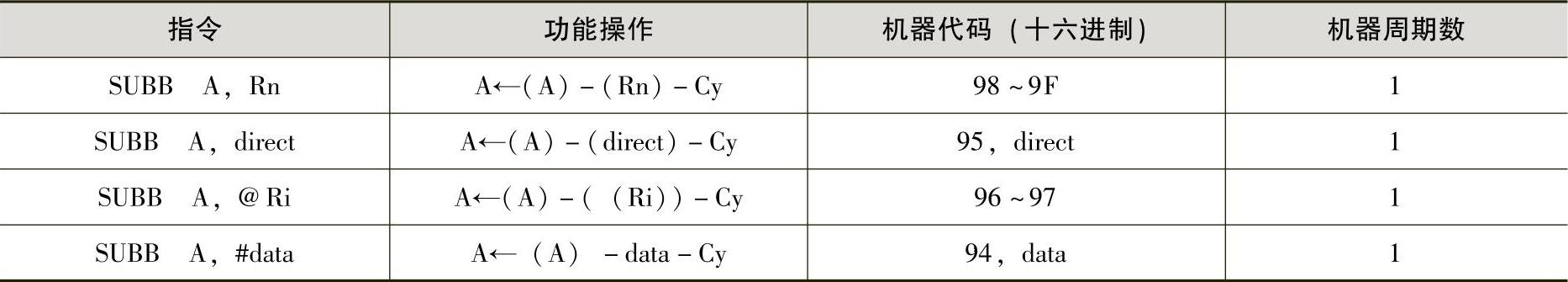

3 带借位减法指令(4条)

指令助记符为SUBB。指令的功能都是第一操作数A的内容减去第二操作数的内容,再减去上次的Cy值,然后把差存入A中,同时产生新的AC、Cy、OV、P位的值。减法操作会对PSW中标志位Cy、AC、OV产生影响。当减法有借位时,则Cy=1,否则Cy=0。若低4位向高4位有借位,则AC=1,否则AC=0;若减法时最高位与次高位不同时发生借位,则OV=1,否则OV=0。

带借位C减法指令、功能操作、机器代码和执行机器周期数如表3-9所示。

表3-9 带借位C减法指令、功能操作、机器代码和执行机器周期数

注意:无不带借位的减法指令。

A的内容减去指定变量和进位标志Cy的值,结果存在A中。

1)如果位7需借位,则Cy置1,否则Cy清0。

2)如果位3需借位,则AC置1,否则AC清0。

3)如果位6借位而位7不借位,或者位7借位而位6不借位,则溢出标志位OV置1,否则OV清0。

使用带借位减法指令需注意以下问题:

1)由于减法本身就属于带符号数运算,所以不宜将操作数看成是无符号数。单片机在进行减法时,实际上是在控制器的控制下,采用补码加法来实现的。

执行减法指令时,首先将减数变为原码,再取负(改变符号)并求补变为补码,然后再与以补码表示的被减数相加,将减法变加法。

2)在实际应用中,也可以通过手工减法运算判定减法的操作结果。只是这时PSW中的标志位改为按如下规则产生:

借位标志Cy:差的D7位有借位时,(Cy)=1;否则,(Cy)=0。

辅助借位标志AC:差的D3位有借位时,(AC)=1;否则,(AC)=0。

溢出标志OV:差的D7、D6位同时有借位或同时无借位时,(OV)=0;差的D7、D6位只有一个有借位时,(OV)=1。可表示为:(OV)=(D7借位)+(D6借位)。

当OV=1时,表示按补码运算法则得到的结果产生溢出,超出了8位二进制补码所允许的数值范围(-128~+127)。

奇偶标志P:当累加器ACC中1的个数为奇数时,(P)=1;为偶数时,(P)=0。

3)MCS-51指令系统中没有不带借位的减法指令,若需进行不带借位的减法,可通过在带借位减法指令前插入一条对Cy清0的指令CLR C来实现。

例3-16:已知(A)=98H,(30H)=85H,求(A)-(30H)。程序如下:

CLR C;将前次Cy清0(https://www.xing528.com)

SUBB A,30H

假设(A)=7EH,(R2)=FFH,(Cy)=0,执行指令

SUBB A,R2;A←(A)-(R2)-(Cy)

计算:7EH-FFH=7EH-FFH=01111110B-11111111B。

4 乘除法指令(2条)

(1)乘法指令

该指令的功能是将累加器A与寄存器B中的两个无符号8位整数相乘,执行后乘积为16位,并把16位乘积的高8位存入寄存器B中,低8位存入累加器A中。

该指令只影响PSW中的3个标志位:当乘积大于0FFH即255,溢出标志位(OV)=1,否则OV复位;奇偶标志P仍由累加器A中1的个数而定;进位标志Cy总是被清0。

例如,若(A)=A0H,(B)=40H,执行指令:MUL AB。

结果为:(B)=28H,(A)=00H,(OV)=1,(P)=0,(Cy)=0。

说明:当积大于255(0FFH)时,即积的高字节B不为0时,置OV=1,否则OV=0;Cy位总是0。

MUL指令实现8位无符号数的乘法操作,乘法指令是整个指令系统中执行时间最长的2条指令之一。它需要4个机器周期(48个振荡周期)完成一次操作,对于12MHz晶振频率的系统,其执行一次的时间为4μs。

(2)除法指令

该指令的功能是将累加器A中的8位无符号二进制数除以寄存器B中的8位无符号二进制数,所得的商存入累加器A中,余数存入寄存器B中。该指令也只影响PSW中的3个标志位,对Cy和P的影响与乘法指令相同。指令执行后,进位标志位Cy总是清0,当除数为0时,表示除数为0的除法无意义,结果A、B中的内容不定,此时OV标志位置位,说明除法溢出。累加器A的结果影响P标志。

例如,假设(A)=A0H,(B)=40H,执行指令:DIV AB。

结果为:(A)=02H,(B)=20H,(OV)=0,(P)=1,(Cy)=0。

算术运算指令都是针对8位二进制无符号数的。若要进行带符号或多字节二进制数运算,需编写具体的运算程序,通过执行程序实现。无符号数相除,当除数(B)=0时,结果为无意义,并置OV=1;Cy位总是0。

乘除法指令、功能操作、机器代码和执行机器周期数见表3-10。

表3-10 乘除法指令、功能操作、机器代码和执行机器周期数

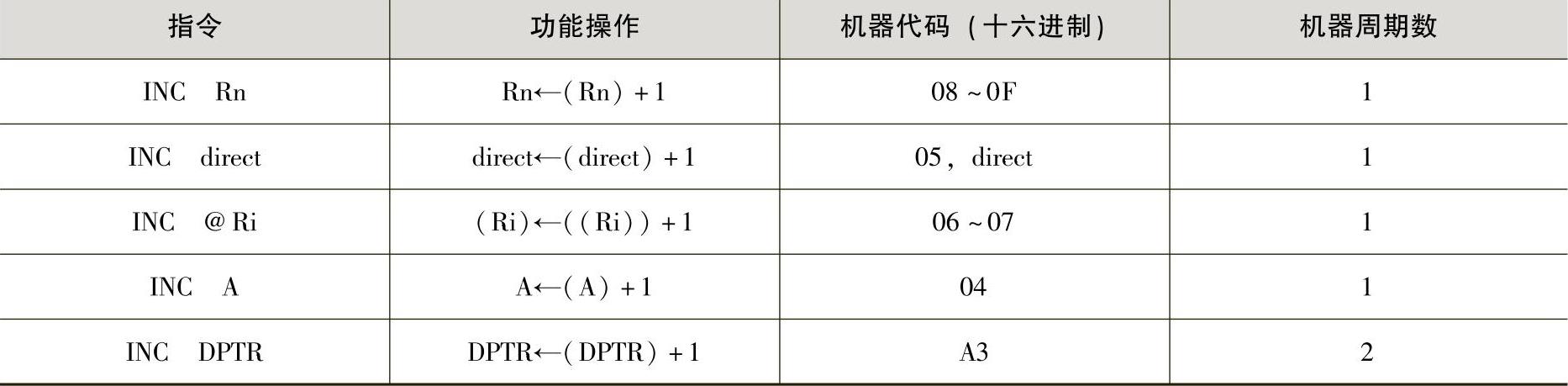

5 加1指令(5条)

增量指令:助记符为INC,指令的功能是将操作数中的内容加1。除对A操作影响P外不影响任何标志。加1指令、功能操作、机器代码和执行机器周期数如表3-11所示。

表3-11 加1指令、功能操作、机器代码和执行机器周期数

6 减1指令(4条)

这组指令的功能是将指令中指定单元的内容减1,结果再送回原单元。除了DEC A指令影响PSW中的P标志位,其余指令都不影响PSW中的标志位。功能是指定的变量减1。若原来为00H,减1后下溢为FFH,不影响标志位(P标志除外)。

减1指令、功能操作、机器代码和执行机器周期数见表3-12。

表3-12 减1指令、功能操作、机器代码和执行机器周期数

注意:没有对DPTR的减1操作指令。

虽然没有不带C的减法指令,但可在带C的减法指令前将C清0(清进位标志指令CLR C),其实际效果就是不带C的减法运算。

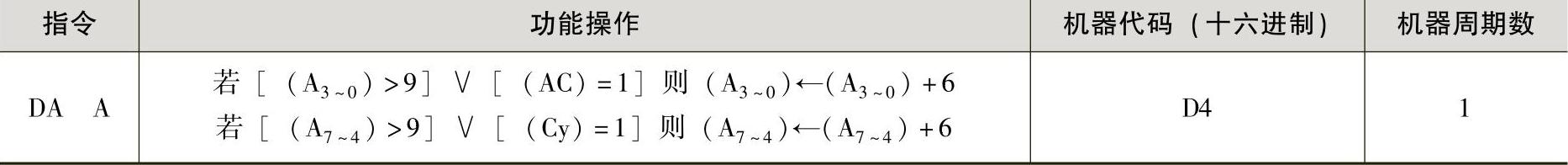

7 十进制调整指令(1条)

ADD、ADDC指令都是对8位二进制数进行加法运算,当两个BCD码数进行加法时,必须增加一条DA A指令(对其结果进行调整),否则结果就会出错。出错原因在于BCD码共有16个编码,但只用其中的10个,剩下6个没用到。这6个没用到的编码(1010,1011,1100,1101,1110,1111)为无效编码。在BCD码加运算中,凡结果进入或者跳过无效编码区时,结果出错。无论哪种错误,都是因为6个无效编码造成的。因此,只要出现上述两种情况之一,就必须调整。方法是把运算结果加6调整,即十进制调整修正。

十进制调整方法如下:

1)累加器低4位大于9或辅助进位位AC=1,则低4位加6修正。

2)累加器高4位大于9或进位位Cy=1,则高4位加6修正。

3)累加器高4位为9,低4位大于9,高4位和低4位分别加6修正。

上述调整修正是通过执行指令DA A来自动实现的。

该指令的功能是将累加器A中刚进行的两个压缩的BCD码(十进制数的二进制编码)加法结果进行十进制调整。这条指令通常要紧跟在加法指令之后使用。

十进制调整指令、功能操作、机器代码和执行机器周期数见表3-13。

表3-13 十进制调整指令、功能操作、机器代码和执行机器周期数

注意:①DA指令只能跟在加法指令后面使用;②调整前参与运算的两数是BCD码数;③DA指令不能与减法指令配对使用,但可以实现A中压缩BCD数进行减1操作;④执行十进制调整指令后,PSW中的Cy表示结果的百位值。

由于BCD码加法是逢十进一,但单片机实际上进行的是二进制加法,它在两个相邻BCD码之间实际上是逢十六进一,从而将10~15表示为AH~FH;16~18表示为10H~12H,出现非BCD码。所以两个压缩的BCD码按二进制相加后,必须经过调整才能得到正确地用BCD码形式表示的和。调整的方法是,当出现AH~FH、10H~12H时,通过加6修正,使之分别调整为10~15、16~18,符合BCD码逢十进一的原则。中间结果的修正是由ALU硬件中的十进制修正电路自动进行的。

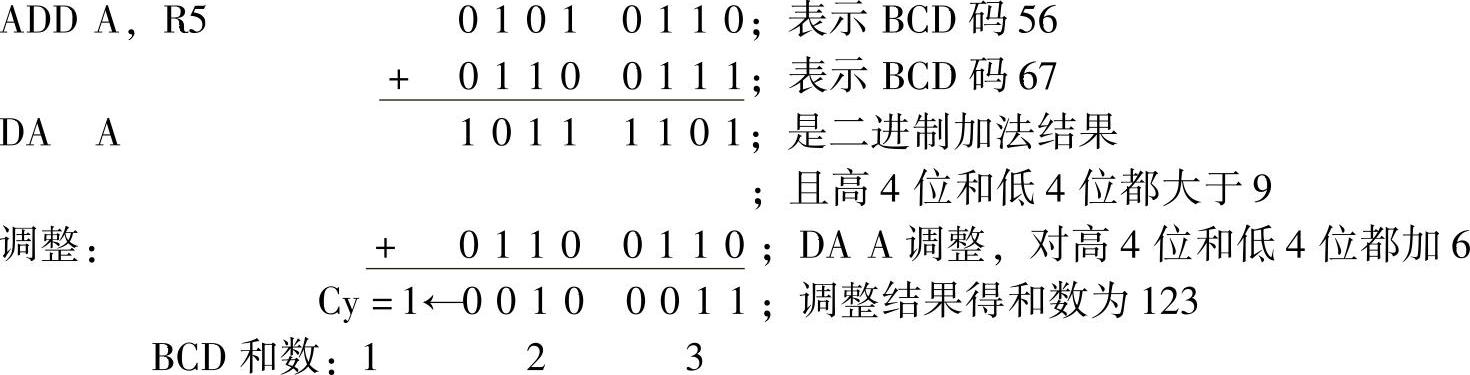

例3-17:(A)=56H,(R5)=67H,把它们看作两个压缩的BCD数,进行BCD加法。执行修正:

结果:(A)=23H,Cy=1,由此可见,56H+67H=123H,结果正确。

设计将两个BCD码相加的执行程序如下:

ORG 0000H

MOV A,#56H;将56H传送到A中,但表示的是BCD数56

MOV B,#67H;将67H传送到B中,但表示的是BCD数67

ADD A,B;Cy=0,(A)=BDH,但数BDH为二进制加法结果,

;要得出正确的BCD码的和数,必须对结果进行十进制调整

DA A;调整后Cy=1、(A)=23H、AV=1。Cy中内容和A中内容构成的数正是BCD

;和数,56H+67H=123H,可见Cy中内容表示BCD的和数的百位

SJMP $

END

当需要进行BCD码减法时,可通过求减数的补数,把被减数-减数变为被减数+减数的补数,即把减法变为加法,然后再用DA A指令进行调整,便可实现BCD码的减法运算。

设X表示一个BCD码,则对于长度为两位BCD码的X的补数为100-|X|。例如:

89-69=89+[69]补=89+(100-69)=89+31=120

在单片机中可用9AH代表上式中的100,实现上述运算。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。