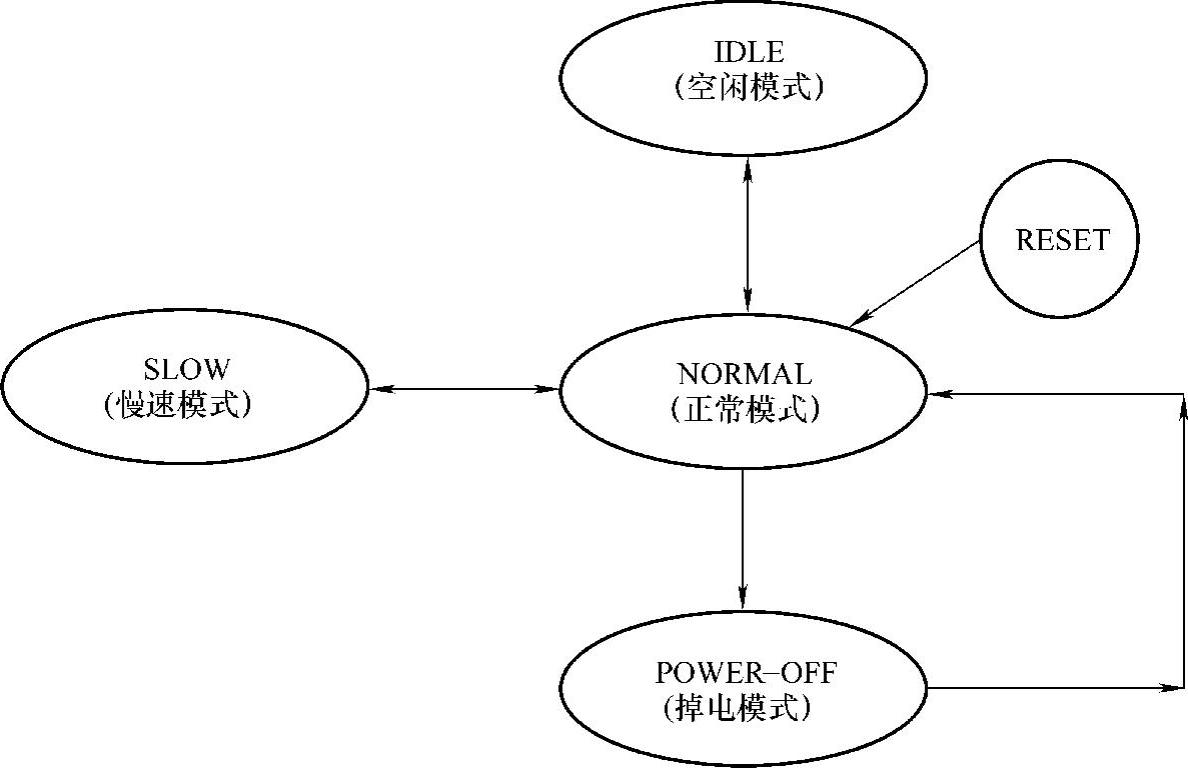

电源管理模块靠软件驱动来控制S3C2410A的系统时钟,目的是降低整体的功耗。这项功能是和锁相环(PLL)、时钟控制逻辑(FCLK、HCLK和PCLK)和唤醒信号相关的。S3C2410A有4种电源模式,分别是NORMAL(正常模式)、IDLE(空闲模式)、SLOW(慢速模式)和POWER_OFF(掉电模式)。这4种电源模式之间是不可以随意进行转换的,图6-8给出了4种模式之间的转换图。

图6-8 4种模式之间的转换图

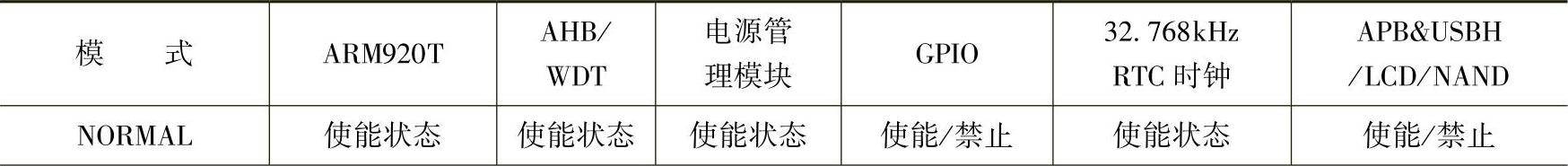

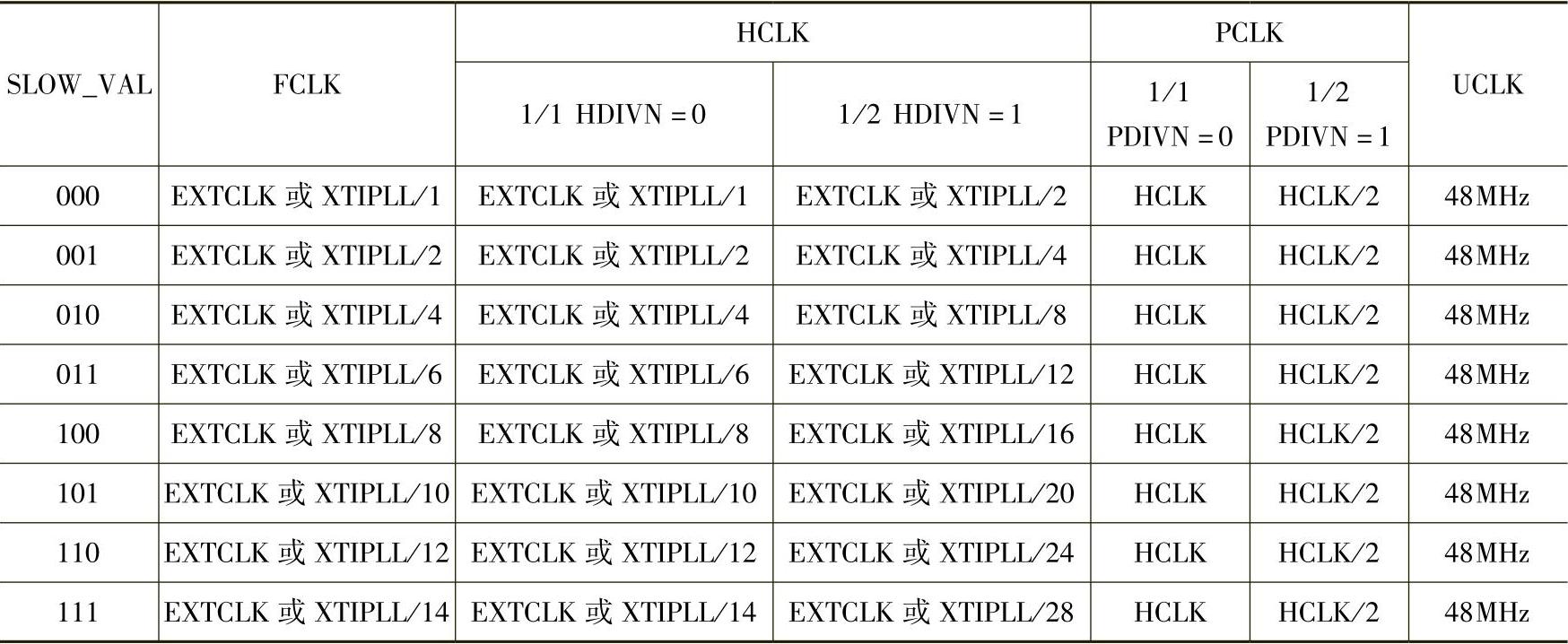

表6-4给出了在每种模式下电源和时钟的情况列表。

表6- 4在每种模式下电源和时钟的情况列表

(续)

1.NORMAL模式

在NORMAL模式下,所有的外设和包括电源管理模块在内的基础模块、CPU核、总线控制器、存储器控制器、中断控制器和DMA都是正常工作的。除基础模块外,每个外设的时钟都可以在软件的控制下被关闭以降低系统功耗。

2.IDLE模式

在IDLE模式下,连接CPU核的时钟被禁止。只要触发外部中断、RTC告警中断或其他类型中断就可以退出IDLE模式。

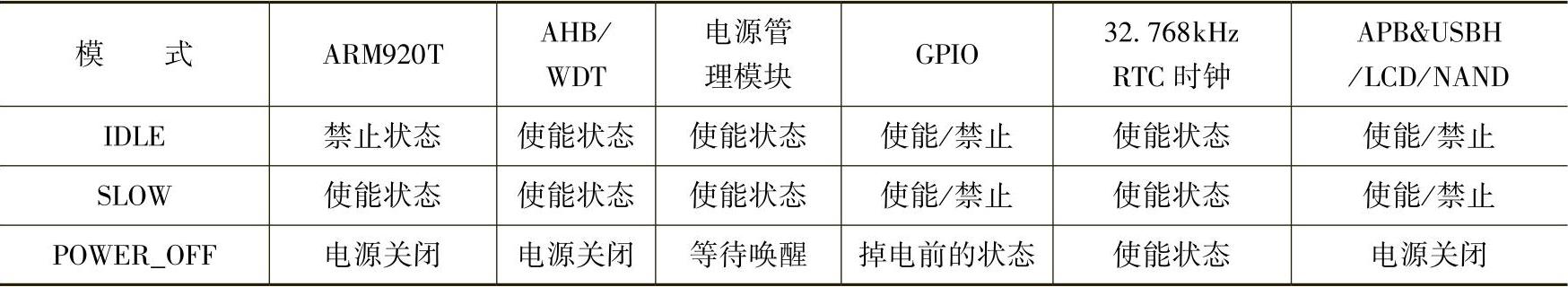

3.SLOW模式(非锁相环模式)

在SLOW模式下,系统时钟由外部时钟设备供给而不采用内部锁相环生成的时钟,这样系统的功耗完全取决于外部供给的时钟频率。在SLOW模式下,FCLK是由外部晶体时钟源或外部时钟电路产生的时钟信号分频而来。分频的比例由CLKSLOW控制寄存器中的SLOW_VAL和CLKDIVN控制寄存器来确定,表6-5给出了慢速时钟设置表。

表6-5 慢速时钟设置表

表中EXTCLK为外部时钟源电路产生的时钟信号,XTIPLL为外部晶体和S3C2410A内部的振荡器产生的时钟信号。

在SLOW模式下,为了降低系统功耗而将锁相环关闭。在锁相环被关闭的SLOW模式中,用户可以将模式改变为NORMAL模式,此处锁相环需要锁定时间。在锁相环被打开后,其稳定时间为150μs。

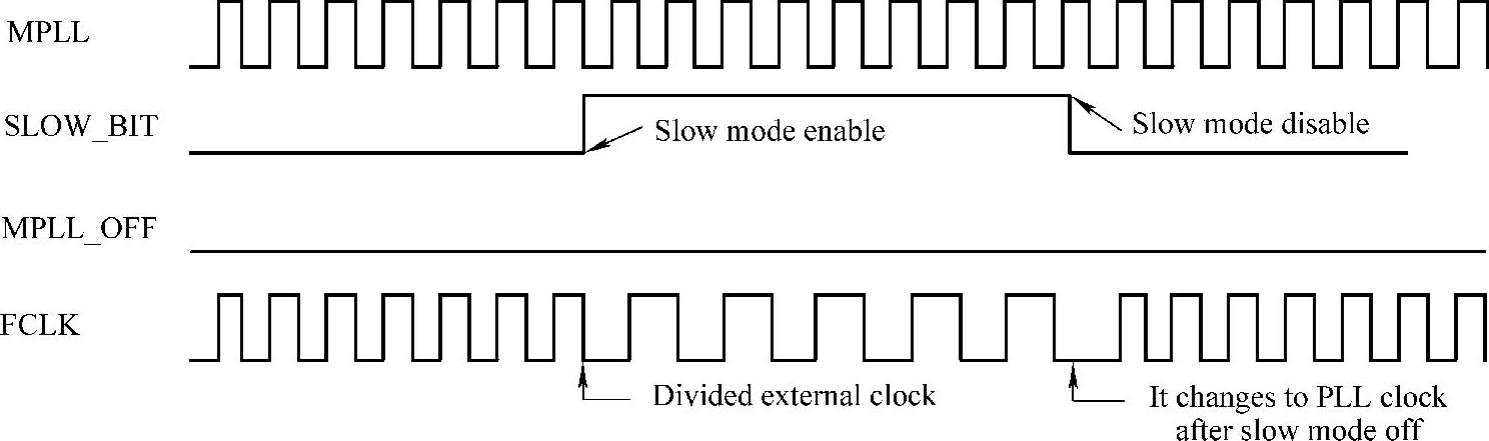

用户可以在锁相环开启状态下通过使能寄存器CLKSLOW中的SLOW模式位来改变系统的时钟频率,在SLOW模式下产生SLOW时钟。图6-9给出了在锁相环开启状态下通过SLOW_BIT进入和退出SLOW模式的过程。

图6-9 在锁相环开启状态下通过SLOW_BIT进入和退出SLOW模式的过程

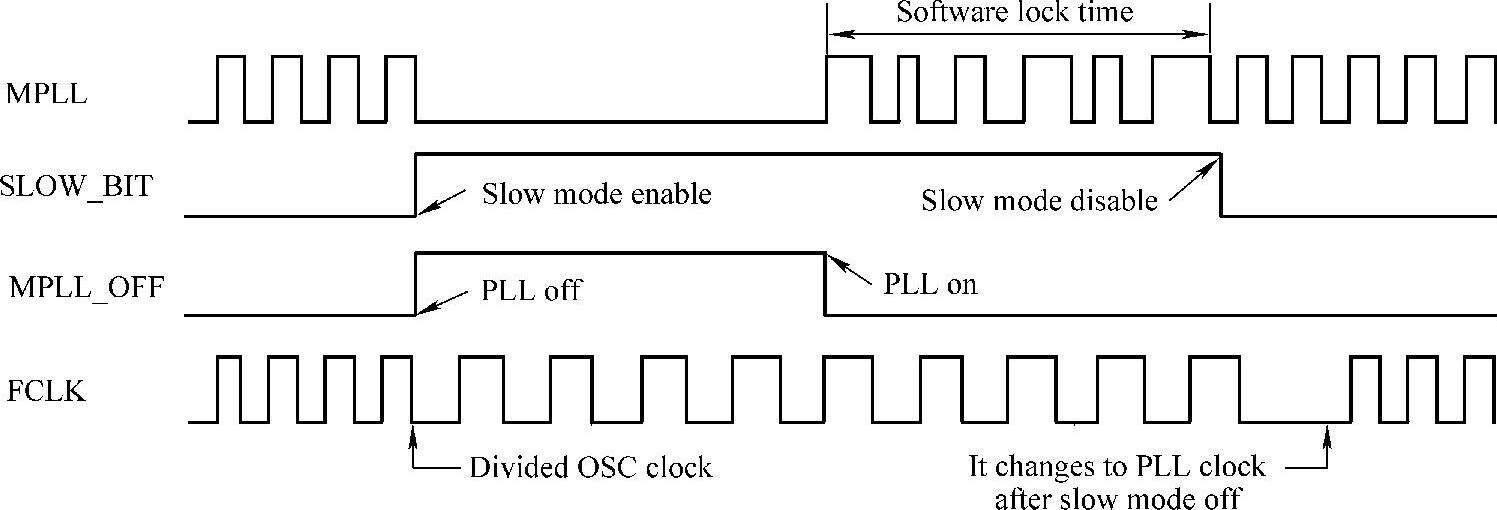

如果用户在锁相环锁定后要靠寄存器CLKSLOW中的SLOW_BIT将模式从SLOW切换至NORMAL,系统时钟在SLOW模式被禁止后才发生改变。图6-10给出了在锁相环锁定后退出SLOW模式的过程。

图6-10 在锁相环锁定后退出SLOW模式的过程

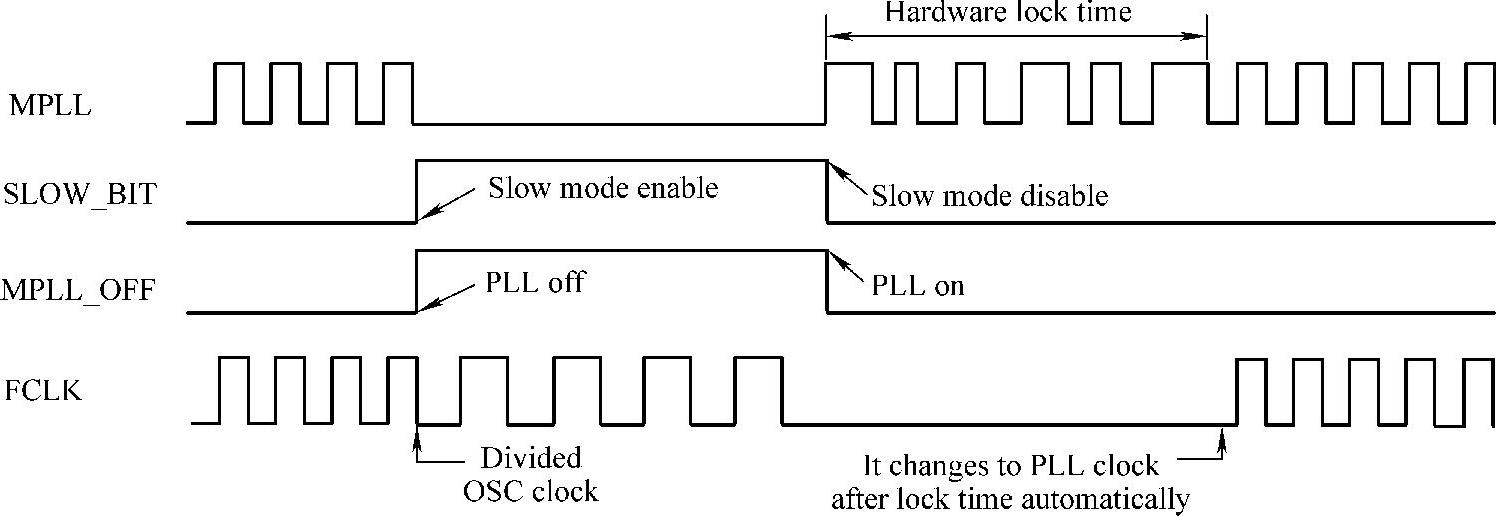

如果用户要靠禁止寄存器CLKSLOW中SLOW_BIT和MPLL_OFF来将模式从SLOW转换到NORMAL,系统频率将会在锁相环锁定后改变。图6-11给出了退出SLOW模式的同时打开MPLL锁相环的过程。

图6-11 退出SLOW模式的同时打开MPLL锁相环的过程

4.POWER_OFF模式

POWER_OFF模式的功能是断开内部电源。当内部电源断开时,除去唤醒逻辑电路外,CPU和内部逻辑电路均无功耗。激活POWER_OFF模式需要两个电源。一个电源负责给唤醒逻辑供电,另一个电源负责给其他内部逻辑电路和CPU供电,并且该电源是可控的。在POWER_OFF模式下,为CPU和内部逻辑电路供电的电源被关闭。通过外部中断EINT[15∶0]和RTC告警中断可以退出POWER_OFF模式。

(1)进入POWER_OFF模式的过程

1)配置GPIO配置寄存器。

2)在INTMSK寄存器中禁止所有中断。正确地配置包括RTC告警在内的唤醒源。为了让寄存器SRCPND和EINTPEND中相应的bit位置位,在寄存器EINTMSK中与唤醒源相关的bit位不能被屏蔽。

3)将USB端口配置为挂起状态。(MISCCR[13∶12]=11b)

4)在寄存器GSTATUS3和GSTATUS4中存储一些有特殊含义的值,这些寄存器在POWER_OFF模式中会保持不变。

5)配置MISCCR[1∶0]使数据总线D[31∶0]上有上拉电阻功能。如果数据总线上存在类似74LVCH162245的总线保持器件,那么上拉电阻功能可以被关闭。(https://www.xing528.com)

6)清零LCDCON1.ENVID比特位停止LCD。

7)为了填充TLB而读取寄存器rREFRESH和rCLKCON。

8)将REFRESH[22]设置为“1”,使SDRAM进入自刷新模式。

9)等待SDRAM自刷新功能有效。

10)使MISCCR[19∶17]=111b,而使SDRAM信号(SCLK0、S CLK1和SCKE)在POWER_OFF模式中被保护起来。

11)在寄存器CLKCON中置位POWER_OFF模式比特位。

(2)从POWER_OFF模式唤醒的过程

1)如果一个唤醒源有效,S3C2410A将进入内部复位状态。复位周期由内部16bit计数逻辑所决定,复位时间靠公式tRST=(65536/外部晶体频率)。

2)为了确定上电过程是否是由POWER_OFF模式唤醒而来的,需要检查GSTATUS2[2]的值。

3)使MISCCR[19∶17]=000b,释放S DRAM被保护的信号。

4)配置SDRAM存储器控制器。

5)等待SDRAM自刷新被释放,所有的SDRAM行一般都需要刷新过程。

6)因为在POWER_OFF模式中寄存器GSTATUS3和GSTATUS4的值保持不变,所以这两个寄存器的值可用于用户自己的目的。

7)对于EINT[3∶0],检查寄存器SRCPND。对于EINT[15∶4],检查寄存器EINT- PEND。对于告警唤醒,检查RTC时间。因为SRCPND中的RTC比特在告警唤醒时不会被置位。如果在POWER_OFF模式中处于nBATT_FLT过程中,SRCPND中的相应比特位会被置位。

(3)VDDi和VDDiarm的电源控制

在POWER_OFF模式中,VDDi和VDDiarm会被关闭,这两个电源是由PWREN引脚控制的。

如果PWREN信号有效(高电平),VDDi和VDDiarm将由一个外部电源负责供电。如果PWREN信号无效(低电平),VDDi和VDDiarm被关闭。需要注意的是,尽管VDDi、VDDiarm、VDDi_MPLL和VDDi_UPLL会被关闭,其他电源引脚仍有供电。

(4)外部中断EINT[15∶0]唤醒信号

仅当下列条件满足时,S3C2410A可从POWER_OFF模式中被唤醒。

1)在EINTn输入引脚上产生高低电平或信号的上升或下降沿。

2)在GPIO控制寄存器中EINTn引脚需要被配置为外部中断EINT。

3)引脚nBATT_FLT应该为高电平。

在唤醒之后,相应的EINTn引脚就不会再用做唤醒了,即EINTn就是普通的外部中断引脚。

(5)POWER_OFF模式下输出端口的状态

在POWER_OFF模式下,输出端口应该有一个合适的输出电平,这样是为了保证使电流的消耗最小。如果输出端口没有接负载,那么应该保持高电平合适。如果输出为低电平,那么电流会消耗在内部寄生电阻上。

(6)电池错误信号(nBATT_FLT)

电池错误信号有以下两个功能。

1)当CPU处于POWER_OFF模式中,nBATT_FLT引脚会触发中断,触发中断的电平为低电平。

2)当CPU处于POWER_OFF模式中,nBATT_FLT信号会禁止CPU退出掉电模式。如果nBATT_FLT信号有效,那么为了保护由于电池电量低而产生故障的系统,任何唤醒源都会被屏蔽。

(7)ADC掉电

在寄存器ADCCON中,ADC有一个额外的掉电比特位。如果S3C2410A进入POWER_OFF模式,ADC就会进入其自身的掉电模式。

(8)S/W Work-Around

如果靠RTC告警使CPU从POWER_OFF模式中退出,那么在寄存器SRCPND中的RTC源挂起比特位不会被置位。所以在从POWER_OFF模式退出后必须去检查告警数据。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。