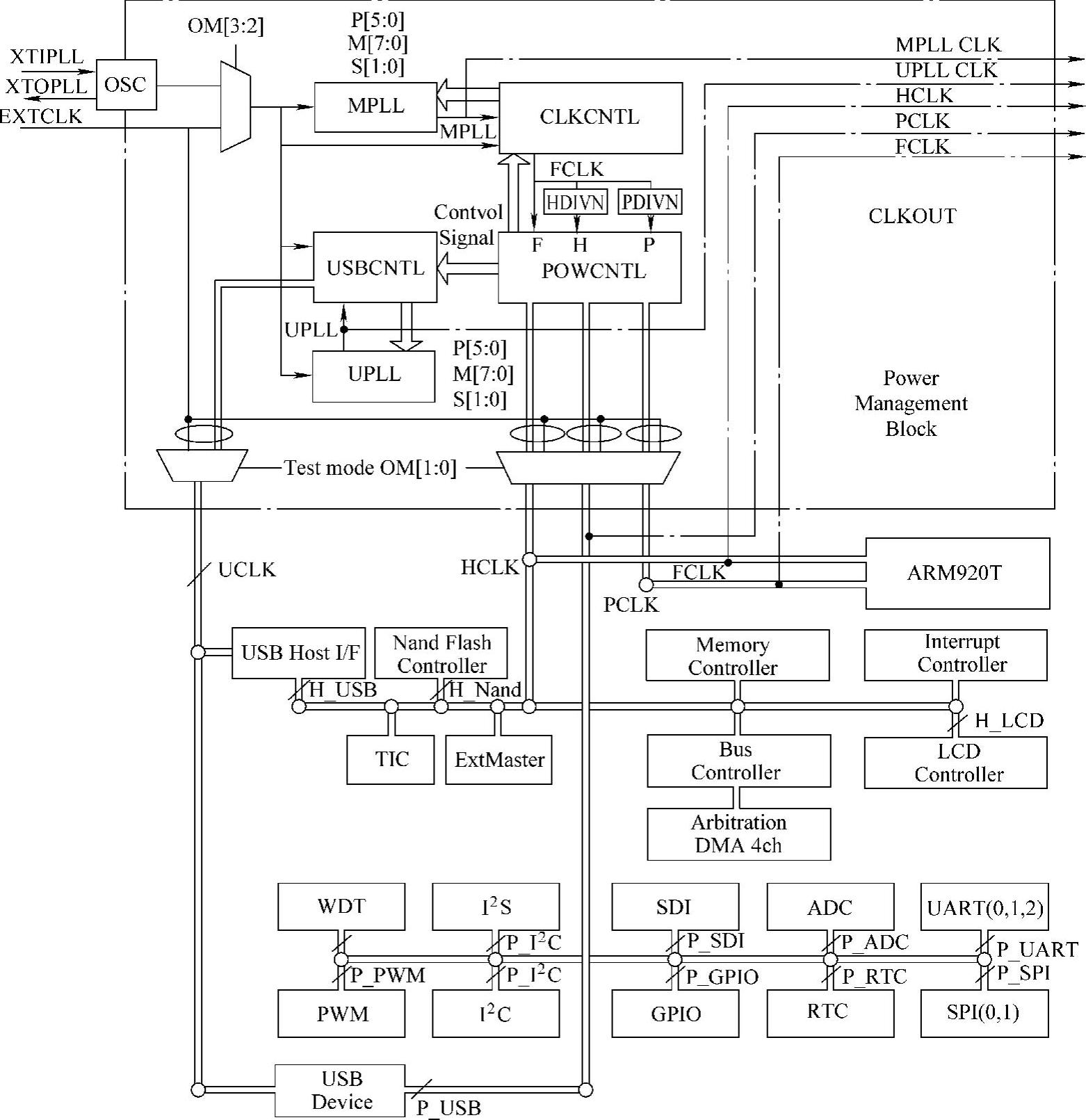

S3C2410A的时钟和电源管理模块由3部分组成,分别是时钟控制模块、USB控制模块和电源控制模块。

S3C2410A的时钟控制逻辑可以产生CPU所用的FCLK时钟信号、AHB总线所用的HCLK时钟信号和APB总线所用的PCLK时钟信号。S3C2410A有两个锁相环(PLL),其中一个锁相环用于产生FCLK、HCLK和PCLK信号;另一个锁相环产生USB模块所用的48MHz信号。时钟控制逻辑可以产生频率较低的时钟信号而不采用锁相环。为了降低电源功耗,时钟控制逻辑用软件控制时钟信号与外设模块连接或断开。

(1)时钟模块结构

图6-2为S3C2410A的时钟模块结构图。主时钟是来自外部晶体(XTIpll)或外部的时钟源(EXTCLK)。时钟发生器包括一个振荡器,这个振荡器与一个外部晶体相连接;时钟发生器还包括两个锁相环(MPLL和UPLL),这两个锁相环负责产生S3C2410A所需要的高频时钟信号。

图6-2 S3C2410A的时钟模块结构图

(2)时钟源选择

表6-1为启动时时钟源的选择,说明了模式控制引脚(OM3和OM2)和S3C2410A时钟源选择之间的关系。在nRESET信号的上升沿处,OM3和OM2引脚的状态被内部锁存器锁存。

表6-1 启动时时钟源的选择

这里需要注意的是,尽管S3C2410A上电复位后锁相环MPLL即开始工作,但直到用户为寄存器MPLLCON写入可用的数值后MPLL的输出才能作为芯片的系统时钟使用。在可用设置生效之前,来自外部晶体的时钟或外部时钟源的时钟将直接被用做系统时钟。即使用户不想更改寄存器MPLLCON的默认值,也要求用户向寄存器MPLLCON写入与默认值相同的数值。

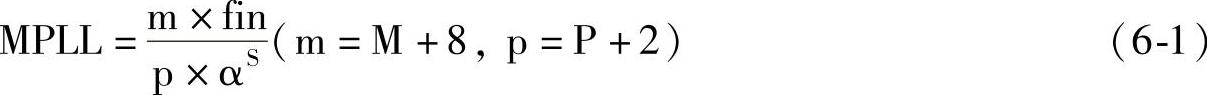

(3)锁相环(MPLL)

有关锁相环的具体知识与本书内容关系度不高,这里就不再赘述了,这里只给出锁相环MPLL(是S3C2410A芯片内部的一种锁相环)的输入频率和输出频率的关系公式,利用这个公式就可以计算出不同配置下,S3C2410A的系统时钟频率了。

公式6-1中的M、P和S的值在寄存器PLLCON中都有定义。

S3C2410A中锁相环的功能框图如图6-3所示。

图6-3 S3C2410A中锁相环的功能框图

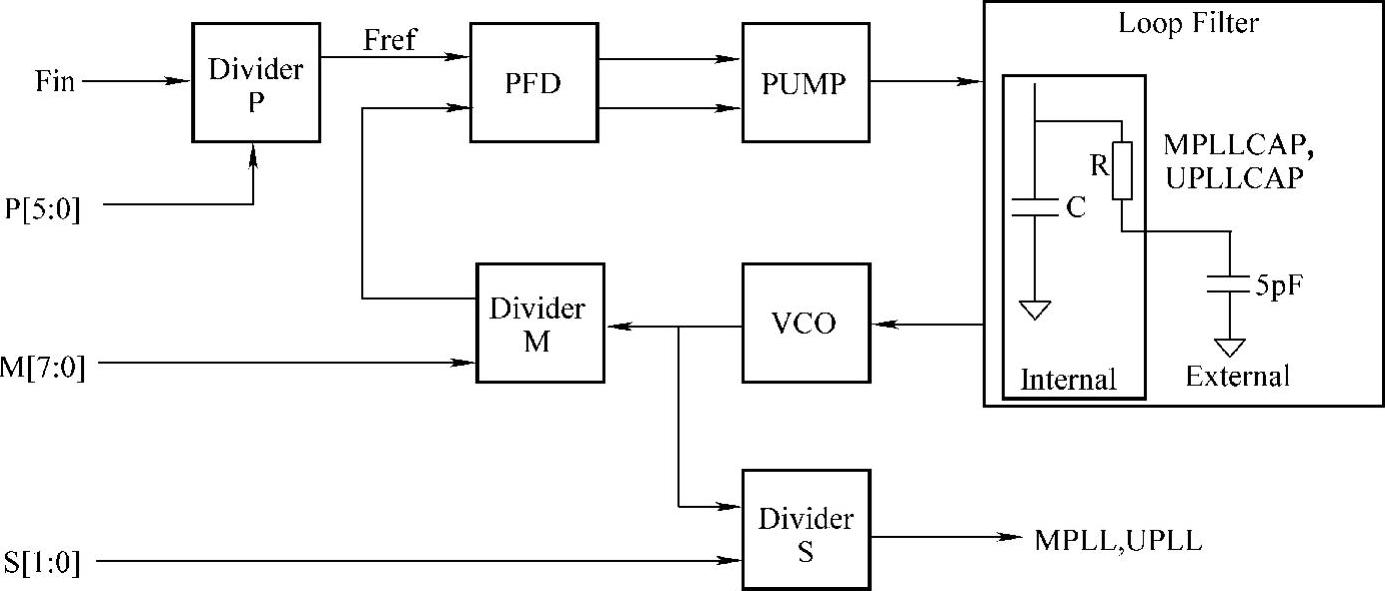

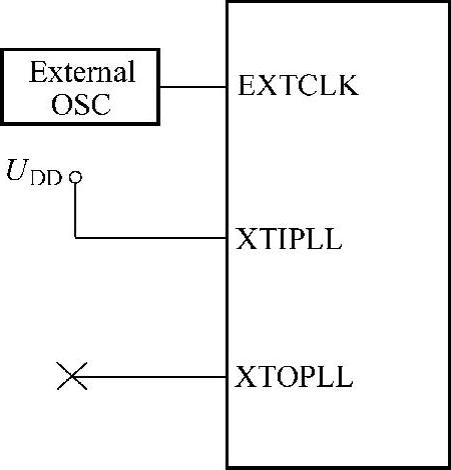

图6-4为外部晶体供给系统时钟时的电路,图6-5为外部时钟源供给系统时钟时的电路。当OM[3∶2]=00时,使用外部晶体作为时钟源的主时钟电路;当OM[3∶2]=11时,使用外部时钟电路作为时钟源的主时钟电路。

锁相环电路和时钟发生器电路通常的应用条件为:锁相环环路滤波电容(Loop filter ca- pacitance)为5pF,外部晶体频率或外部时钟源的频率应为10~20MHz,且时钟信号FCLK的频率要至少大于外部晶体频率或外部时钟源的频率3倍或3倍以上,外接晶体作为时钟源时,振荡电路的电容为15~22pF。

图6-4 外部晶体供给系统时钟时的电路

(https://www.xing528.com)

(https://www.xing528.com)

图6-5 外部时钟源供给系统时钟时的电路

(4)时钟控制逻辑

时钟控制逻辑决定了系统所使用的时钟源究竟是来自锁相环产生的时钟还是来自外部时钟源的时钟。当让锁相环产生新的频率时,时钟控制逻辑会在锁相环输出稳定之前禁止FCLK输出。时钟控制逻辑在上电复位后和从掉电模式下恢复后都会被激活。

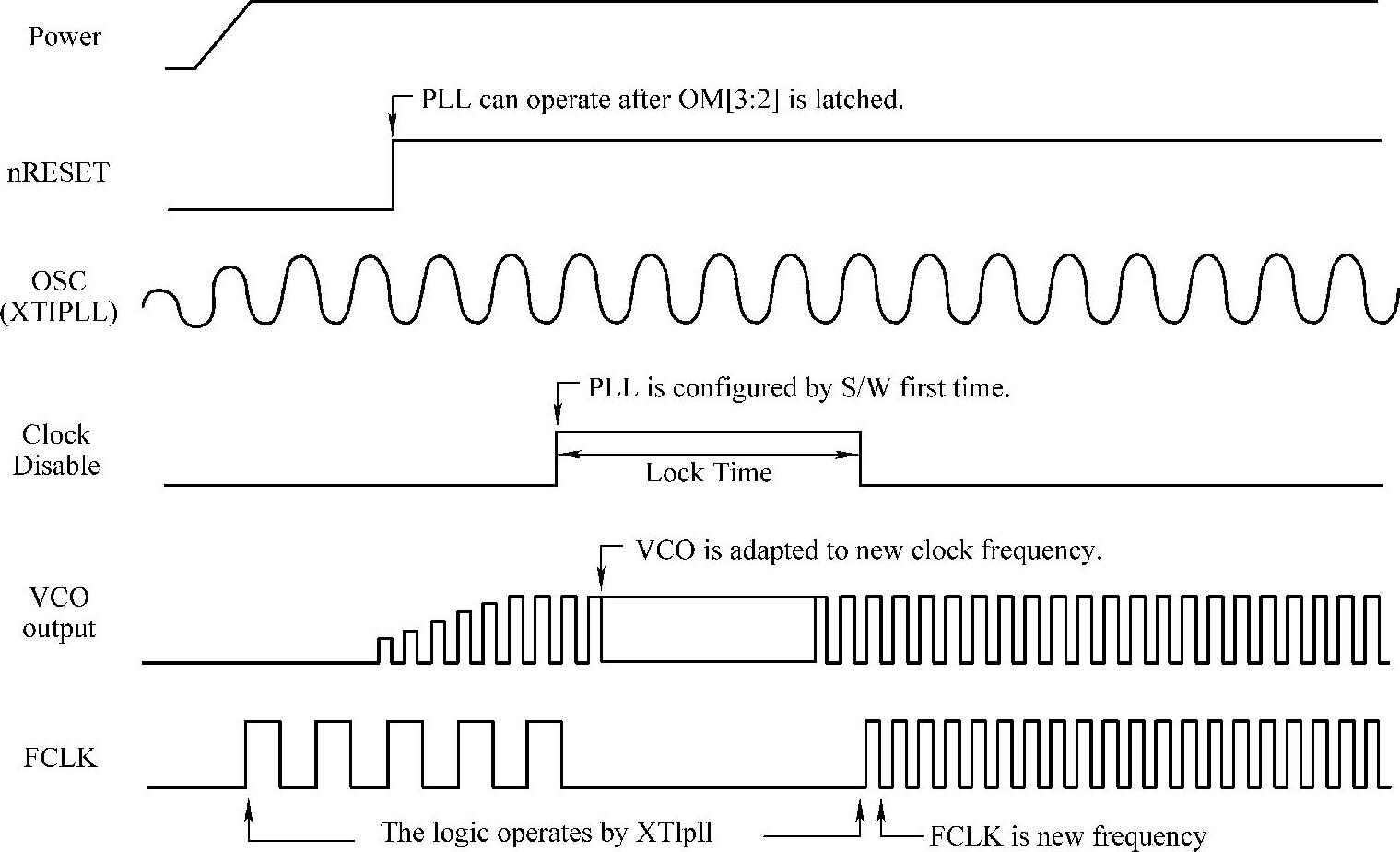

图6-6给出了在上电复位过程中时钟信号的行为。上电后在几毫秒内晶体振荡器开始起振。在振荡器电路稳定后,复位信号nRESET被释放,锁相环根据默认的配置值开始工作。锁相环在上电复位后不能立刻达到稳定状态,所以在用户对寄存器PLLCON进行新的配置之前fin信号作为FCLK信号使用而不是MPLL输出的信号。如果用户在复位后不打算修改寄存器PLLCON的值而采用默认设置,那么也需要在软件中用默认值去配置寄存器PLLCON。如果用户在软件中为锁相环配置了新的输出频率,那么锁相环为了达到新的输出频率会重启锁定过程。在锁相环锁定后,FCLK时钟立即就等于MPLL的输出时钟。

图6-6 上电复位过程中时钟信号的行为(外部时钟源为晶体)

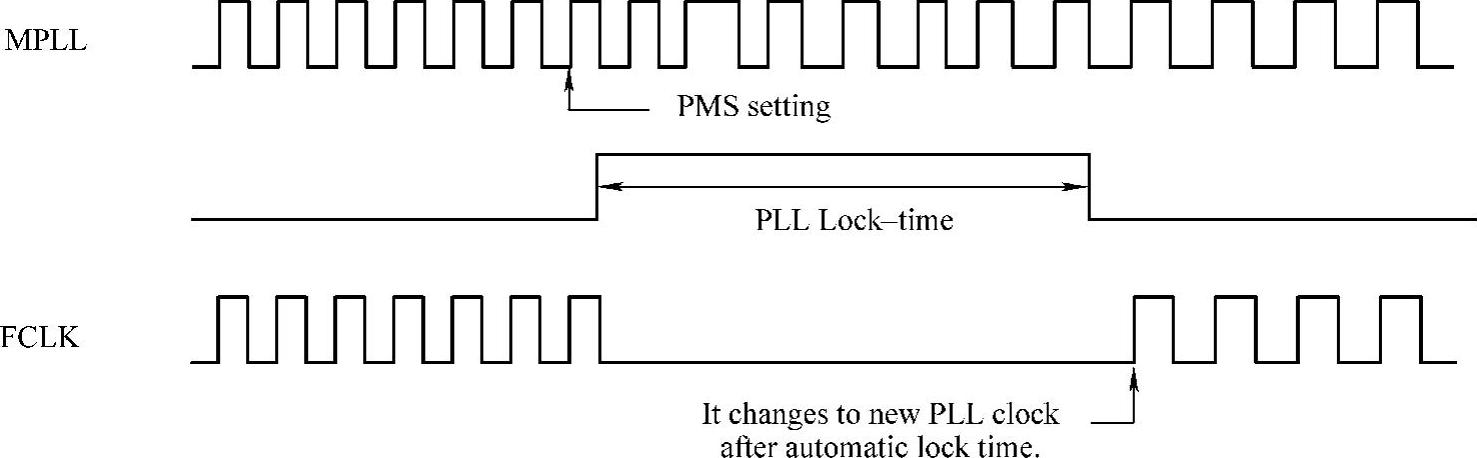

在S3C2410A工作于NORMAL模式下时,用户可以采用写PMS值的方式改变锁相环输出频率,写PMS值后锁相环会自动插入锁定过程。在锁定过程中,锁相环输出不会给S3C2410A的内部模块提供时钟。图6-7给出了写PMS值改变锁相环输出的时序图。

图6-7 写PMS值改变锁相环输出的时序图

(5)USB时钟控制

S3C2410A中的USB主机接口和USB设备接口工作时需要48MHz时钟。在S3C2410A中,锁相环UPLL负责产生USB所用的48MHz信号(UCLK)。在UPLL被配置之前,UCLK信号无效。表6-2给出了UCLK和UPLL的状态列表,说明了UCLK和UPLL不同条件下的不同状态。

表6-2 UCLK和UPLL的状态列表

(6)FCLK、HCLK和PCLK

FCLK、HCLK和PCLK是S3C2410A工作时使用的时钟信号。FCLK是CPU内核ARM920T所用的时钟信号。HCLK是AHB总线所用时钟信号,AHB总线上连接了存储器控制器、中断控制器、LCD控制器、DMA控制器和USB主机模块。PCLK是APB总线所用时钟信号,APB总线上连接了诸如WDT(看门狗定时器)、IIS、I2 C、PWM定时器、MMC接口、ADC、UART、GPIO、RTC和SPI这些外设接口。

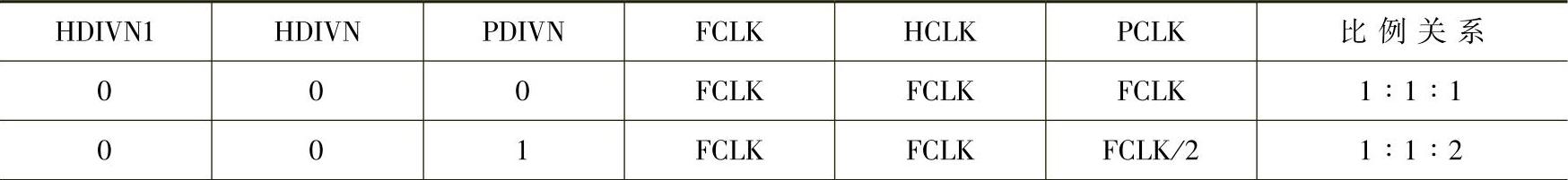

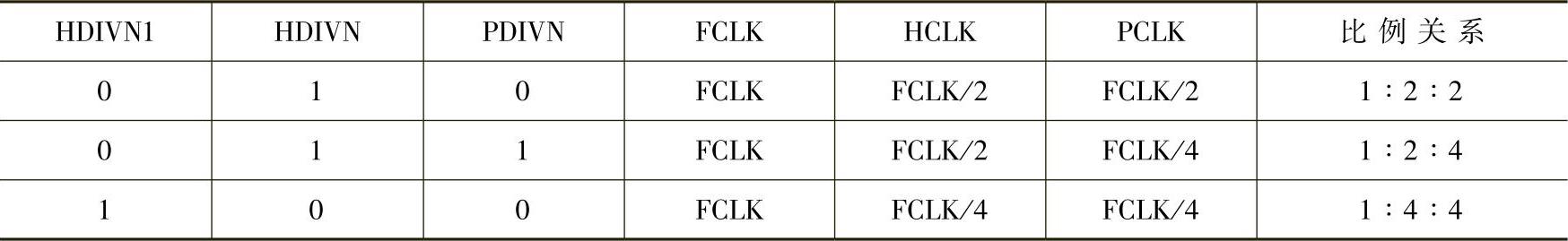

S3C2410A支持用户选择FCLK、HCLK和PCLK之间的比例,这个比例由寄存器CLKDI- VN中的HDIVN和PDIVN来确定。表6-3给出了由HDIVN1、HDIVN和PDIVN所确定的FCLK、HCLK和PCLK之间的分频比例列表。

表6-3 分频比例列表

(续)

在设置PMS值之后,紧跟着就需要设置寄存器CLKDIVN。在锁相环稳定之后才能对寄存器CLKDIVN进行设置。需要注意的是,设置CLKDIVN时不要超过HCLK和PCLK的限制。如果将HDIVN设置为“1”,那么CPU的总线模式将变为快速总线模式,CPU将由HCLK信号来驱动。这个特点可以用来在不影响HCLK和PCLK的情况下将CPU的频率减半。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。