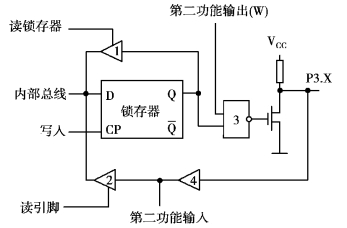

P3口是一个多功能端口,其某一位的结构如图4.4所示。对比P1口的结构图不难看出,P3口与P1口相比,多了与非门③和缓冲器④,正是这两个部分,使得P3口除了具有P1口的准双向I/O功能之外,还可以使用各引脚所具有的第二功能。与非门③的作用实际上是一个开关,可决定输出锁存器上的数据或第二功能(W)的信号。当W=1时,可输出Q端信号;当Q=1可输出W线信号。

图4.4 P3口某位结构

编程时,可不必事先由软件设置P3口为第一功能(通用I/O口)还是第二功能。当CPU对P3口进行SFR寻址(位或字节)访问时,由内部硬件自动将第二功能输出线W置1,P3口为通用I/O口;当CPU不把P3口作为SFR寻址(位或字节)访问时,即用作第二功能输出/输出线时,由内部硬件使锁存器Q=1。

1)P3口作为通用I/O口使用

P3口工作原理与P1口工作原理类似。当把P3口作为通用I/O口进行SFR寻址时,“第二输出功能端”W保持高电平,打开与非门③,所以D锁存器输出端Q的状态可通过与非门③送至FET场效应管输出,这是作通用I/O输出的情况。

当P3口作为输入使用(即CPU读引脚状态)时,同P0~P2口一样,应由软件向口锁存器写“1”,即使D锁存器Q端保护为1,与非门输出为0,FET场效应管截止,引脚端可作为高阻输入。当CPU发出读命令时,缓冲器②上的“读引脚”信号有效,三态缓冲器②开通,于是引脚的状态经缓冲器④(常开的)、缓冲器②送到CPU内部总线。(https://www.xing528.com)

2)P3口用作第二功能使用

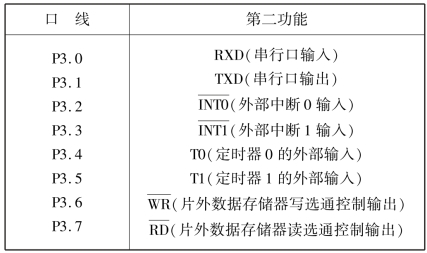

当端口用于第二功能时,8个引脚可按位独立定义见表4.1。当某位被用作第二功能时,该位的D锁存器Q应被内部硬件自动置1,使与非门③对“第二输出功能端”W是畅通的。“第二输出功能端”W可为表4.1中的TXD、![]() 三个第二输出功能引脚。例如RD功能,W线上的

三个第二输出功能引脚。例如RD功能,W线上的![]() 控制信经与非门③控制FET输出到引脚端。

控制信经与非门③控制FET输出到引脚端。

表4.1 P3各口线的第二功能表

由于D锁存器Q端已被置1,W线不作第二功能输出时也保持为1,FET截止,该位引脚为高阻输入,此时,第二输入功能为:RXD、![]() 、T0和T1。由于端口不作为通用I/O口(不执行MOV A,P3),“读引脚”信号无效,三态缓冲器②不导通,某位引脚的第二输入功能信号(如RXD)经缓冲器④送入第二输入功能端。

、T0和T1。由于端口不作为通用I/O口(不执行MOV A,P3),“读引脚”信号无效,三态缓冲器②不导通,某位引脚的第二输入功能信号(如RXD)经缓冲器④送入第二输入功能端。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。