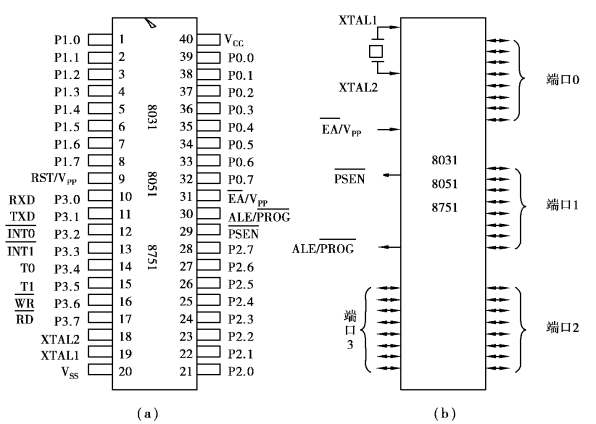

MCS-51系列中各种芯片的引脚是互相兼容的,如8051和8031均采用40引脚双列直插封装(DIP)方式。不同芯片之间引脚功能也略有差异。8051单片机是高性能单片机,因为受到引脚数目的限制,不少引脚具有第二功能,其中有些功能是8051芯片所专有的,如图2.4所示。

图2.4 8051单片机的引脚

各引脚功能简要说明如下:

1)电源引脚VCC和VSS

VCC(40脚):电源端,接+5 V。

VSS(20脚):接地端。

2)时钟电路引脚XTAL1和XTAL2

XTAL2(18脚)接外部晶体和微调电容的一端,XTAL1(19脚)接外部晶体的另一端。使用方法详见2.4节。

(1)控制信号引脚RST、ALE、![]() 和

和![]()

①RST/VPD(9脚)

RST是复位信号输入端,高电平有效。当此输入端保持两个机器周期(24个时钟振荡周期)的高电平时,就可以完成复位操作。RST引脚的第二功能是VPD,即备用电源的输入端。当主电源VCC发生故障,降低到低电平规定值时,将+5 V电源自动接入RST端,为RAM提供备用电源,以保证存储在RAM中的信息不丢失,复电后能继续正常运行。CHMOS型单片机的备用电源是由VCC端提供的。

②ALE/![]() (ADDRESS LATCH ENABLE/PROGRAMMING,30脚)

(ADDRESS LATCH ENABLE/PROGRAMMING,30脚)

地址锁存允许信号端。当8051上电正常工作后,ALE引脚不断向外输出正脉冲信号,此频率为振荡器频率fosc的1/6。CPU访问片外存储器时,ALE输出信号作为锁存低8位地址的控制信号。在CPU访问片外数据存储器时,每取指一次(一个机器周期)会丢失一个脉冲。

平时不访问片外存储器时,ALE端也以1/6的振荡频率固定输出正脉冲,因此ALE信号可以用作对外输出时钟或定时信号。如果要查看8051/8031芯片是否损坏,可用示波器查看ALE端是否有脉冲信号输出,如ALE端有脉冲信号输出,则表明8051/8031芯片正常无损。

ALE端的负载驱动能为8个LS型TTL(低功耗甚高速TTL)。此引脚的第二功能![]() 是对片内带有4 K EPROM的8751编程写入(固化程序)时,作为编程脉冲输入端。

是对片内带有4 K EPROM的8751编程写入(固化程序)时,作为编程脉冲输入端。

③![]() (PROGRAM STORE ENABLE,29脚)

(PROGRAM STORE ENABLE,29脚)

程序存储允许输出信号端。在访问片外程序存储器时,此端定时输出负脉冲作为读片外存储器的选通信号。此引脚接EPROM的![]() 端,

端,![]() 端有效,即允许读出EPROM/ROM中的指令码,CPU在从外部EPROM/ROM取指期间,

端有效,即允许读出EPROM/ROM中的指令码,CPU在从外部EPROM/ROM取指期间,![]() 信号在每个机器周期(12个时钟周期)中两次有效。不过,在访问片外RAM时,至少产生两次

信号在每个机器周期(12个时钟周期)中两次有效。不过,在访问片外RAM时,至少产生两次![]() 负脉冲信号。

负脉冲信号。

![]() 端同样可驱动8个LS型TTL。如果要检查一个8051/8031小系统上电后CPU能否正常到EPROM/ROM中读取指令码,可用示波器查看

端同样可驱动8个LS型TTL。如果要检查一个8051/8031小系统上电后CPU能否正常到EPROM/ROM中读取指令码,可用示波器查看![]() 端有无脉冲输出,如有脉冲输出,表明该CPU工作正常。

端有无脉冲输出,如有脉冲输出,表明该CPU工作正常。

④![]() /VPP(ENABLE ADDRESS/VOLTAGE PULSE OF PROGRAMMING,31脚)(https://www.xing528.com)

/VPP(ENABLE ADDRESS/VOLTAGE PULSE OF PROGRAMMING,31脚)(https://www.xing528.com)

外部程序存储器地址允许输入端/固化编程电压输入端。当![]() 引脚接高电平时,CPU只访问片内EPROM/ROM并执行内部程序存储器中的指令,但在PC(程序计数器)的值超过0FFFH(对8751/8051为4 K时),将自动转向执行片外程序存储器内的程序。

引脚接高电平时,CPU只访问片内EPROM/ROM并执行内部程序存储器中的指令,但在PC(程序计数器)的值超过0FFFH(对8751/8051为4 K时),将自动转向执行片外程序存储器内的程序。

当输入信号![]() 引脚接低电平(接地)时,CPU只访问外部EPROM/ROM并执行外部程序存储器的指令,而不管是否有片内程序存储器。对无片内ROM的8031或8032,须外扩EPROM,此时必须将

引脚接低电平(接地)时,CPU只访问外部EPROM/ROM并执行外部程序存储器的指令,而不管是否有片内程序存储器。对无片内ROM的8031或8032,须外扩EPROM,此时必须将![]() 引脚接地。如使用有片内ROM的8051,外扩EPROM也是可以的,但也要使

引脚接地。如使用有片内ROM的8051,外扩EPROM也是可以的,但也要使![]() 接地。

接地。

此脚的第二功能VPP是对8751片内EPROM固化编程时,作为施加较高编程电压(一般21 V)输入端。

(2)I/O(输入/输出)端口(Port)P0、P1、P2和P3

①P0口(P0.0~P0.7,39~32脚)

P0口是一个漏极开路的8位双向I/O端口。作为漏极开路的输出端口,每位能驱动8个LS型TTL负载。当P0口作为输入口使用时,应先向口锁存器(地址80H)写入全1,此时P0口的全部引脚浮空,可作为高阻抗输入。作输入口使用时要先写1,这就是准双向的含义。

在CPU访问片外存储器(8031)片外EPROM或RAM时,P0是分时提供低8位地址和8位数据的复用总线。在此期间P0口内部上拉电阻有效。

对于8751单片机,因不需外扩EPROM,所以P0口可作为一个数据输入/输出口。

②P1口(P1.0~P1.7,1~8脚)

P1口是一个带内部上拉电阻的8位准双向I/O端口。P1口的每位能驱动(吸收或输出电流)4个LS型TTL负载。

在P1口用为输入口使用时,应先向P1口锁存器(地址90H)写入全1,此时,P1口引脚由内部上拉电阻拉成高电平。

③P2口(P2.0~P2.7,21~28脚)

P2口是一个带内部上拉电阻的8位准双向I/O端口。P2口的每一位能驱动(吸收或输出电流)4个LS型TTL负载。

在访问片外EPROM/ROM时,它可输出高8位地址。

④P3口(P3.0~P3.7,10~17脚)

P3口是一个带内部上拉电阻的8位准双向I/O端口。P3口的各位能驱动(吸收或输出电流)4个LS型TTL负载。

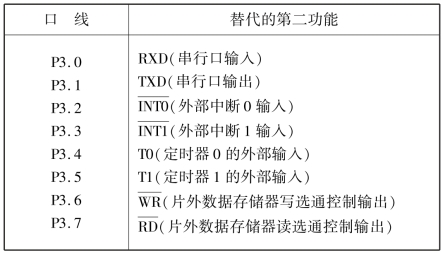

P3口与其他I/O端口有很大区别。它除可作为一般准双向I/O端口外,每个引脚还具有专门的功能,见表2.3。

表2.3 P3各口线与第二功能表

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。