设备管理的主要任务之一是控制I/O设备与内存或CPU之间的数据传送。随着计算机技术的发展,控制方式也在不断发展,经历了程序直接控制、中断驱动、DMA控制和通道控制四种方式。在早期的计算机系统中采用的是程序直接控制方式,CPU与外设只能串行工作,利用率低;为了减少CPU的等待时间以及提高系统的并行性,系统中引入了中断机制,数据传输方式发展为中断驱动方式;此后,随着DMA控制器的出现,可用来代替CPU控制内存和设备之间进行成批的数据交换,使数据传输单位从以字节为单位扩大到以数据块为单位进行,大大提高了块设备的数据传输速度;而通道的引入,实现了设备和内存直接进行交换数据,无需CPU的干预。

选择和衡量控制方式的原则如下:

(1)数据传输速度足够高,能满足用户的需要但又不能丢失数据。

(2)系统开销小,所需的处理控制程序少。

(3)能充分发挥硬件资源的能力,使得I/O设备尽量忙,而CPU的等待时间少。

(4)尽最减少主机对I/O控制的干预,而更多地去完成数据处理任务。

6.2.1 程序直接控制

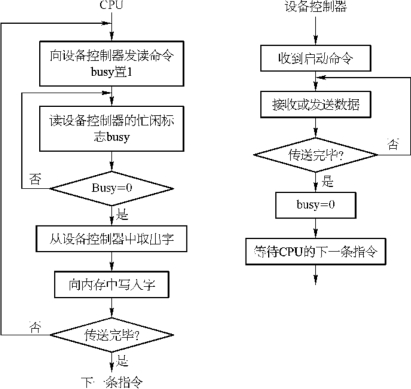

程序直接控制(programmed direct control)方式是由用户进程直接控制内存或CPU与I/O设备之间的数据传送,也称为忙-等待方式。CPU首先向设备或控制器的控制寄存器发出一条I/O指令启动I/O设备进行数据传输,同时硬件把状态寄存器中的忙闲标志busy置为1,表示该设备尚未输入完一个字(符),然后CPU便不断地重复读取busy进行测试,此时CPU不能执行其他进程,直到busy=0,表示该设备已将输入数据送入到控制器的数据寄存器中,于是CPU将数据寄存器中的数据取出,送入内存指定单元中,这样便完成了一个字(符)的I/O,接着再去启动读下一个数据,并置busy=1。程序直接I/O控制方式的读数据处理过程如图6-5所示。

程序直接I/O方式管理简单,不需要硬件支持,但程序直接I/O方式存在以下缺点:

(1)CPU和I/O设备只能串行工作。由于CPU的高速性和I/O设备的低速性,致使CPU的大量时间都处于等待设备完成数据传输的循环测试中,CPU的利用率大大降低。

(2)CPU在一段时间内只能与一台I/O设备交换数据,不能实现设备之间的并行工作。

图6-5 程序直接I/O控制方式的处理过程

(3)程序直接I/O方式中CPU无中断机构,靠不断测试设备状态寄存器的标志位来控制数据的传输,I/O设备无法向CPU报告它已完成了一个字符的输入操作,也无法报告设备或其他硬件的错误信息。

因此程序直接I/O方式只适用于那些CPU执行速度慢而且外围设备少的系统。

6.2.2 中断方式

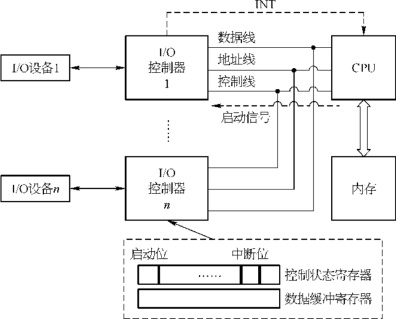

为了减少程序直接I/O方式中的CPU等待时间以及提高系统的并行性,中断驱动(interrupt driven)方式被用来控制I/O设备与内存和CPU之间的数据传送。中断驱动方式要求CPU与设备控制器之间有中断请求线INT,而且在设备控制器的状态寄存器有相应的中断允许位。中断驱动I/O控制方式的传送结构如图6-6所示。

图6 6 中断驱动I/O控制方式的传送结构

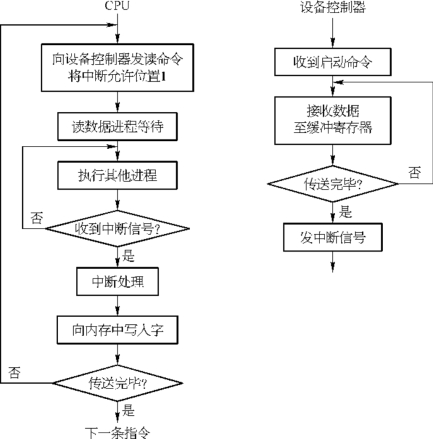

当某进程需要数据时,由CPU向相应的设备控制器发出一条I/O指令启动设备准备数据,该指令同时将状态寄存器中的中断允许位打开,以便控制器在准备好数据并向CPU发出中断请求时,中断程序可以被调用执行。然后该进程放弃CPU,等待数据处理完成,进程调度程序调度其他进程让CPU进行处理。此时,CPU与I/O设备处于并行工作状态。对设备控制器来说,当收到CPU发来的读命令后,便准备接收输入设备送来的数据,当数据输入控制器的数据缓冲寄存器后,设备控制器通过中断请求线INT向CPU发出中断信号,CPU收到信号后调用中断处理程序进行数据出错检查,若无错,则将数据读入内存,等待提出请求的进程取出进行处理,并向控制器发送取走数据的信号。中断驱动I/O控制方式的读数据处理过程如图6-7所示。

图6-7 中断驱动方式的处理过程

因此中断驱动方式在I/O设备输入数据的过程中,无须CPU干预,可以使CPU与I/O设备并行工作。仅当输完一个数据时,才需CPU花费极短的时间去进行中断处理,从而大大地提高了整个系统的资源利用率及吞吐量,特别是CPU的利用率。

例如,从终端设备输入一个字符的时间约为100 ms,而CPU将字符送入终端缓冲区的时间小于0.1 ms,若采用程序直接I/O方式,CPU约有99.9 ms的时间处于忙-等待循环查询过程中。但采用中断驱动方式后,CPU仅需要用0.1 ms的时间来处理由控制器发来的中断请求,而利用99.9 ms的时间去执行其他进程或发送启动其他设备的命令,做到设备与设备的并行操作,以及设备和CPU的并行操作。

尽管中断驱动方式比程序直接I/O方式更有效,大大提高了CPU的利用率,并且可支持CPU与设备、设备与设备的并行操作,但仍存在以下问题:

(1)每次在控制器的数据缓冲寄存器装满之后将发生中断,而数据缓冲寄存器通常较小,以字(节)为单位进行数据的I/O。当完成一个字(节)的I/O时,控制器便要向CPU请求一次中断,因此在一次数据传送过程中发生中断的次数较多,将这种方式用于块设备的I/O,效率非常低。

(2)现代计算机系统通常配置有各种类型的I/O设备,如果都通过中断方式并行操作,则中断次数急剧增加,从而造成CPU无法及时响应中断现象。

(3)若系统中I/O设备的速度非常高,则可能出现数据缓冲寄存器中的数据由于CPU来不及取走而丢失的现象。

DMA方式和通道方式则不会产生上述问题。

6.2.3 DMA方式

1.DMA(direct memory access)控制方式特点

DMA方式又称直接存取方式,是一种完全由硬件执行I/O数据交换的工作方式,它需要使用一个专门的DMA控制器,在这种方式中,DMA控制器采用盗窃总线控制权的方法从CPU接管对总线的控制,成批的数据交换不经过CPU而直接在内存和I/O设备之间进行,进一步减少了CPU对I/O的干预,该方式的特点是:

(1)数据传输的基本单位是数据块,即在CPU与I/O设备之间每次传送至少一个数据块。

(2)所传送的数据是从设备直接送入内存的,或者从内存直接输出到设备。

(3)仅在传送一个或多个数据块的开始和结束时才需要CPU干预,整块数据的传送是在控制器的控制下完成的。(https://www.xing528.com)

因此DMA方式较之中断驱动方式,又成百倍地减少了CPU对I/O的干预,进一步提高了CPU与I/O设备的并行操作程度。

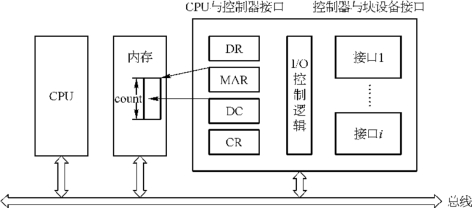

2.DMA控制器的组成

DMA控制器由主机与DMA控制器的接口、DMA控制器与块设备的接口、I/O控制逻辑三部分组成。DMA控制器中设置有控制/状态寄存器CR、传送字节数计数器DC、内存地址寄存器MAR和数据缓冲寄存器DR四类寄存器。DMA控制器的组成如图6-8所示。

图6-8 DMA控制器的组成

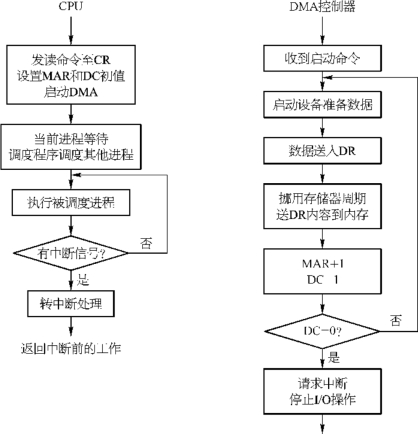

3.DMA方式下数据传送过程

以从设备读入数据为例,DMA方式下的数据传送过程可分为三个阶段:

(1)预处理阶段。当进程要求从设备读入数据块时,CPU向DMA控制器发送一条读命令到控制寄存器CR,并把准备存放输入数据的内存起始地址以及要传送的字节数count分别送入DMA控制中的内存地址寄存器MAR和传送字节数计数器DC,再将设备的源地址直接送至DMA控制器的I/O控制逻辑中。另外,还把状态寄存器CR中的中断允许位和启动位置成1,从而启动设备,开始进行数据输入,此后的数据传送过程便由DMA控制器进行控制。发出数据传输要求的进程进入等待状态,CPU被进程调度程序调度处理其他任务。

(2)数据传送阶段。DMA控制从设备中读入一个字(节)的数据并送入数据寄存器DR后,再挪用一个存储器周期,将该字(节)传送到MAR所指定的内存单元中,接着便将MAR内容加1进行内存地址修改,将DC内容减1对传送字的个数计数,重复上述过程执行数据传送的操作,直到DC为0,表示传送完成,由DMA控制器发出中断请求。

(3)后处理阶段。CPU在收到中断信号后,转入中断处理程序进行后续处理。中断处理结束后,CPU返回到被中断的进程中或切换到新的进程中继续执行。DMA方式下读数据处理过程如图6-9所示。

图6-9 DMA方式的处理过程

6.2.4 通道控制方式

1.I/O通道控制方式的引入

DMA方式起到代理CPU的功能,较之中断驱动方式,大大减少了CPU进行中断处理的次数,显著减少了对I/O控制的干预,进一步提高了CPU与I/O设备的并行操作程度,但在外部设备太多时,CPU的负担依然较重。

I/O通道控制方式是一种以内存为中心,实现设备与内存直接交换数据的控制方式。通道通过执行通道程序,并与设备管理器一起共同实现对I/O设备的控制。I/O通道方式是DMA方式的发展,它可进一步减少CPU的干预,把对一个数据块的读/写为单位的干预减少为对一组数据块的读/写及有关的控制和管理为单位的干预。同时又可实现CPU、通道和I/O设备三者的并行操作,从而更有效地提高整个系统的资源利用率。例如,当CPU要完成一组相关的读/写操作及有关控制时,只需向I/O通道发送一条I/O指令,以给出其所要执行的通进程序的首址和要访问的I/O设备,通道接到该指令后,通过执行通道程序便可完成CPU指定的I/O任务。

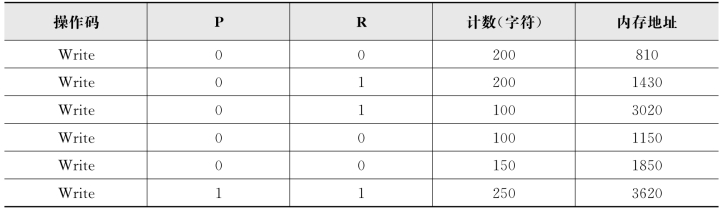

2.通道程序

通道同CPU一样,有运算和控制逻辑,有累加器、寄存器,有自己的指令系统,在程序控制下工作。通道程序是由一系列通进指令(或称为通道命令)所构成。通道指令与一般的机器指令不同,在它的每条指令中都包含下列信息:

(1)操作码。操作码规定了指令所执行的操作,如读、写、控制等操作。

(2)通道程序结束位P。P=0表示通道程序未结束;P=1表示本条指令是通道程序的最后一条指令。

(3)记录结束标志R。R=0表示本条指令与下一条指令所处理的数据属于同一个记录;R=1表示本条指令是处理某记录的最后一条指令。

(4)计数段。计数段信息表示本条指令所要读/写数据的字节数。

(5)内存地址。内存地址标明了字符读/写等操作时的内存首地址。

下面是一个由六条通道指令所构成的简单的通道程序(表6-1),程序的功能是:将内存中不同地址的数据写成三个记录。其中,前两条指令是将一个记录的400个字符分别写入从内存地址810开始的200个单元和从内存地址1430开始的200个单元中,第三条指令是将一个记录的100个字符写入从内存地址3020开始的100个单元中,后三条指令是将一个记录的500个字符分别写入从内存地址1150开始的100个单元、从内存地址1850开始的150个单元中和从内存地址3620开始的250个单元中。

表6-1 简单通道程序

3.数据传送过程

通道控制方式的数据传送过程以输入过程为例,传送过程如下:

(1)当进程要求从设备读入数据时,CPU发送一条通道启动指令,指明I/O操作、设备号和对应通道。

(2)相应通道接收到CPU发来的通道启动指令后,把存放在通道或内存中的通道指令读出,对相应设备的I/O控制器中的控制状态寄存器进行设置。

(3)I/O设备根据通道指令把数据送往内存中指定的地址中。

(4)数据传送结束,I/O控制器向CPU发出中断请求。

(5)CPU在收到中断请求后,转入中断处理程序进行后续处理。中断处理结束后,CPU返回到被中断的进程中或切换到新的进程中继续执行。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。