实验目的

(1)理解单片机串行接口的基本结构。

(2)了解单片机串行通信C语言程序的设计和调试方法。

(3)掌握串行口通信使用方法。

实验仪器

单片机开发板、稳压电源、计算机。

实验原理

1.51单片机串口工作原理

51单片机串口为一个全双工串行接口,既可接收又可发送数据。串行通信是指数据一位一位地按顺序传送的通信方式,其突出优点是只需一根传输线,可大大降低硬件成本,适合远距离通信;其缺点是传输速度较低。

SBUF寄存器:两个在物理上独立的接收、发送缓冲器,可同时发送、接收数据,可通过指令对SBUF的读写来区别是对接收缓冲器的操作还是对发送缓冲器的操作。从而控制外部两条独立的收发信号线RXD(P3.0)、TXD(P3.1),同时发送、接收数据,实现全双工。

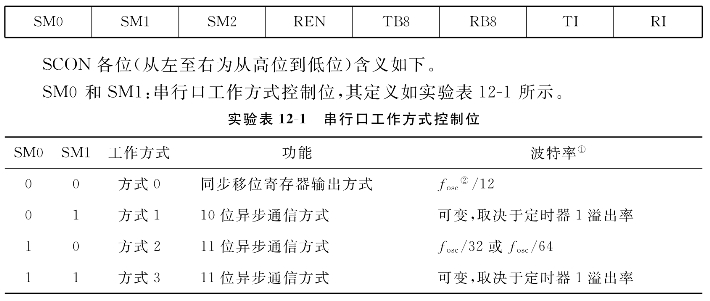

串行口控制寄存器SCON各位:

注:①波特率指串行口每秒钟发送(或接收)的位数;②fosc为单片机的时钟频率。

SM2:多机通信控制位。该位仅用于方式2和方式3的多机通信。其中发送机SM2=1(需要程序控制设置)。接收机的串行口工作于方式2或3,SM2=1时,只有当接收到第9位数据(RB8)为1,才会将接收到的前8位数据送入SBUF,且置位RI发出中断申请引发串行接收中断,否则会将接收到的数据放弃。当SM2=0时,就不管第9位数据是0还是1,都将数据送入SBUF,并置位RI发出中断申请。工作于方式0时,SM2必须为0。

REN:串行接收允许位。REN=0时,禁止接收;REN=1时,允许接收。

TB8:在方式2、3中,TB8是发送机要发送的第9位数据。在多机通信中它代表传输的地址或数据,TB8=0为数据,TB8=1时为地址。

RB8:在方式2、3中,RB8是接收机接收到的第9位数据,该数据正好来自发送机的TB8,从而识别接收到的数据特征。

TI:串行口发送中断请求标志。当CPU发送完一串行数据后,此时SBUF寄存器为空,硬件使TI置1,请求中断。CPU响应中断后,由软件对TI清零。

RI:串行口接收中断请求标志。当串行口接收完一帧串行数据时,此时SBUF寄存器为满,硬件使RI置1,请求中断。CPU响应中断后,用软件对RI清零。

电源控制寄存器PCON各位:

![]()

PCON各位(从左至右为从高位到低位)含义如下。

SMOD:波特率加倍位。SMOD=1,当串行口工作于方式1、2、3时,波特率加倍。SMOD=0,波特率不变。

GF1、GF0:通用标志位。

PD(PCON.1):掉电方式位。当PD=1时,进入掉电方式。

IDL(PCON.0):待机方式位。当IDL=1时,进入待机方式。

另外与串行口相关的寄存器有定时器寄存器和中断寄存器。定时器寄存器用来设定波特率。中断允许寄存器IE中的ES位也用来作为串行I/O中断允许位。当ES=1,允许串行I/O中断;当ES=0,禁止串行I/O中断。中断优先级寄存器IP的PS位则用作串行I/O中断优先级控制位。当PS=1,设定为高优先级;当PS=0,设定为低优先级。

波特率计算:在了解了串行口相关的寄存器之后,可得出其通信波特率的一些结论。

①方式0和方式2的波特率是固定的。(https://www.xing528.com)

在方式0中,波特率为时钟频率的1/12,即fosc/12,固定不变。

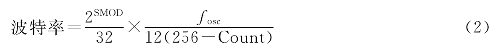

在方式2中,波特率取决于PCON中的SMOD值,即

波特率=2SMOD×fosc/64

当SMOD=0时,波特率为fosc/64;当SMOD=1时,波特率为fosc/32。

②方式1和方式3的波特率可变,由定时器1的溢出率决定。

波特率=2SMOD×(T1的溢出率)/32

当定时器T1用作波特率发生器时,通常选用定时初值自动重装的工作方式2(注意:不要把定时器的工作方式与串行口的工作方式搞混淆了)。其计数结构为8位,假定T1初值为Count,单片机的机器周期为T,则定时时间为(256-Count)×T。因此,在1 s内发生溢出的次数(即溢出率)为

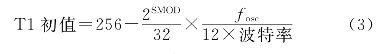

波特率的计算公式为

在实际应用时,通常是先确定波特率,后根据波特率求T1的定时初值,因此公式(2)又可写为

2.74 HC164工作原理与管脚

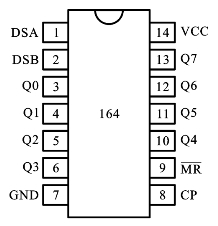

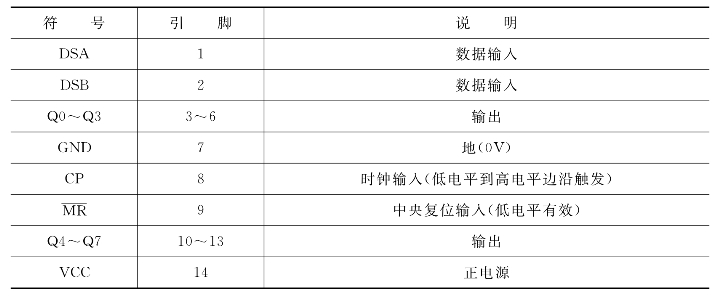

74HC164是8位边沿触发式移位寄存器,串行输入数据,然后并行输出。74 HC164管脚图如实验图12-1所示,各管脚功能见实验表12-2。数据通过两个输入端(DSA或DSB)之一串行输入;任一输入端可以用作高电平使能端,控制另一输入端的数据输入。两个输入端或者连接在一起,或者把不用的输入端接高电平,一定不要悬空。

实验图12-1 74HC164管脚图

实验表12-2 74HC164各管脚功能

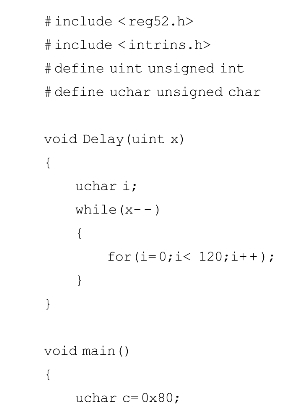

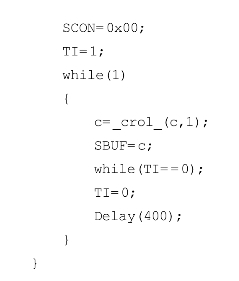

实验源程序

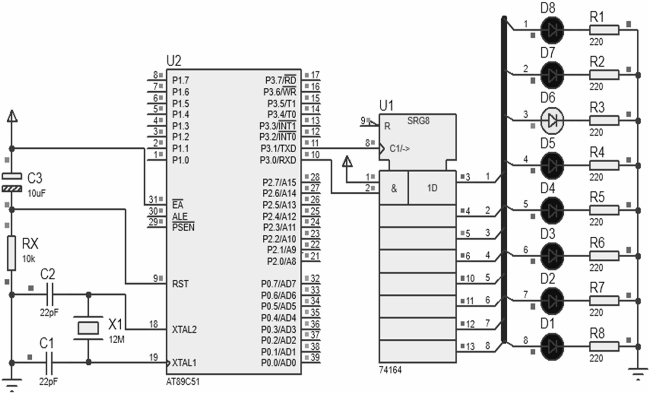

实验仿真电路(实验图12-2)

实验图12-2 串行数据变并行数据实验仿真图

思考题

1.51单片机串行变并行的芯片有哪些?

2.串行接口变并行接口的工程意义是什么?

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。