在PC系统中经常要用到不同频率的定时/计数功能,为此Intel提供了8253和8254芯片用于早期PC中的定时和计数。随着PC的不断演变,8253和8254的功能逐渐被集成到了南桥芯片之中,但是其操作方式依然保持与分立的8253/8254相同的操作方式,以保证软件的兼容性。

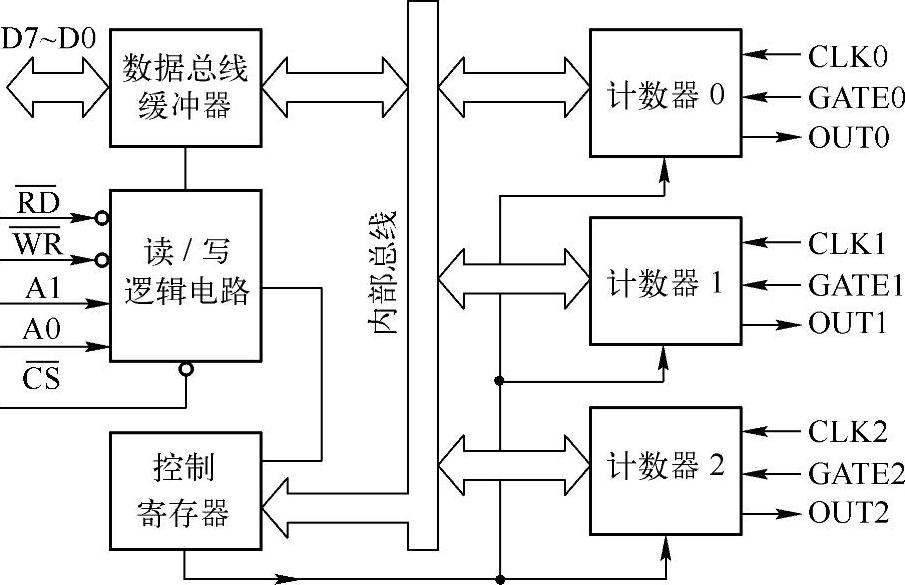

8253和8254芯片的功能、结构和引脚排列基本相同,其主要差别在于8254的最高计数频率为10MHz,而8253只有2MHz。结构上,8253和8254都由数据总线缓冲、读写逻辑、控制字寄存器和三个计数器组成(见图8-22)。

图8-22 8253/8254的内部结构

其中,数据总线缓冲器和读写控制电路负责8253/8254与处理器之间的连接,RD和WR分别负责接收来自CPU的I/O读写命令, 为片选信号,一般由高位地址解码产生。在

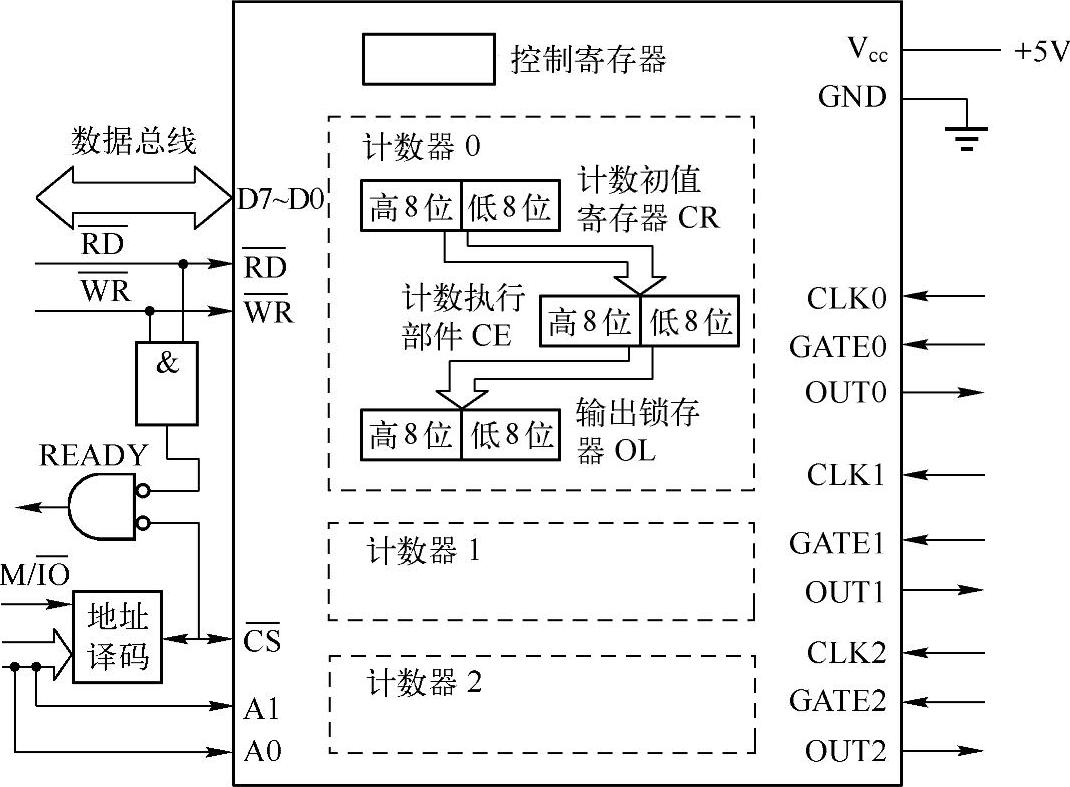

为片选信号,一般由高位地址解码产生。在 为0的情况下,A1A0用于选择对不同的计数器或控制字寄存器进行操作,当A1A0=00时,选中0号计数器,A1A0=01时,选中1号计数器,A1A0=10时,选中操作2号计数器,A1 A0=11时,选中控制字寄存器。控制字寄存器负责寄存初始化时CPU写入的命令字,再通过内部译码确定各计数器的工作方式和计数方式等。8253/8254的三个计数器互相独立地工作,其内部结构如图8-23所示。

为0的情况下,A1A0用于选择对不同的计数器或控制字寄存器进行操作,当A1A0=00时,选中0号计数器,A1A0=01时,选中1号计数器,A1A0=10时,选中操作2号计数器,A1 A0=11时,选中控制字寄存器。控制字寄存器负责寄存初始化时CPU写入的命令字,再通过内部译码确定各计数器的工作方式和计数方式等。8253/8254的三个计数器互相独立地工作,其内部结构如图8-23所示。

图8-23 8253/8254的内部结构

每个计数器有一个输入时钟CLKi、一个控制门脉冲GATEi和一个输出信号OUTi。初始化后,计数初值写入计数初值寄存器,并随后写入计数部件,在接收到合适的GATEi信号后,计数器开始在每个CLKi信号的下降沿将计数器减一。当计数达到规定值时,OUTi端出现输出信号。由于在每个计数周期(即计数器从计数初值减小到0的时间)中OUTi信号出现一次,所以输出信号的频率与输入信号频率、计数初值之间存在如下关系:

N=fCLKi/fOUTi

8253/8254提供6种不同的工作方式,其三个计数器可以互相独立地工作于不同的工作方式。这6种不同的工作方式在启动方式、自动重装等方面各不相同,从而输出不同的波形。在启动方式(或称触发方式)上,8253/8254支持软件启动和硬件启动两种不同的启动方式。其中软件启动方式下计数器初值被写入后,当GATE信号为高电平时计数器即开始工作。而硬件启动则是在计数初值被写入后,只有当GATE信号出现从0到1的跳变后计数器才开始工作。

在8253/8254提供的6种工作方式中,只有方式2和方式3具有初值自动重装的能力,即在这两种工作方式中计数结束的时候,存放在初值寄存器中的技术初值会被自动重装到计数执行部件中,从而使其输出成为一个周期性变化的连续波形。

下面是对这6种工作方式的简要介绍:

1.方式0——事件计数器

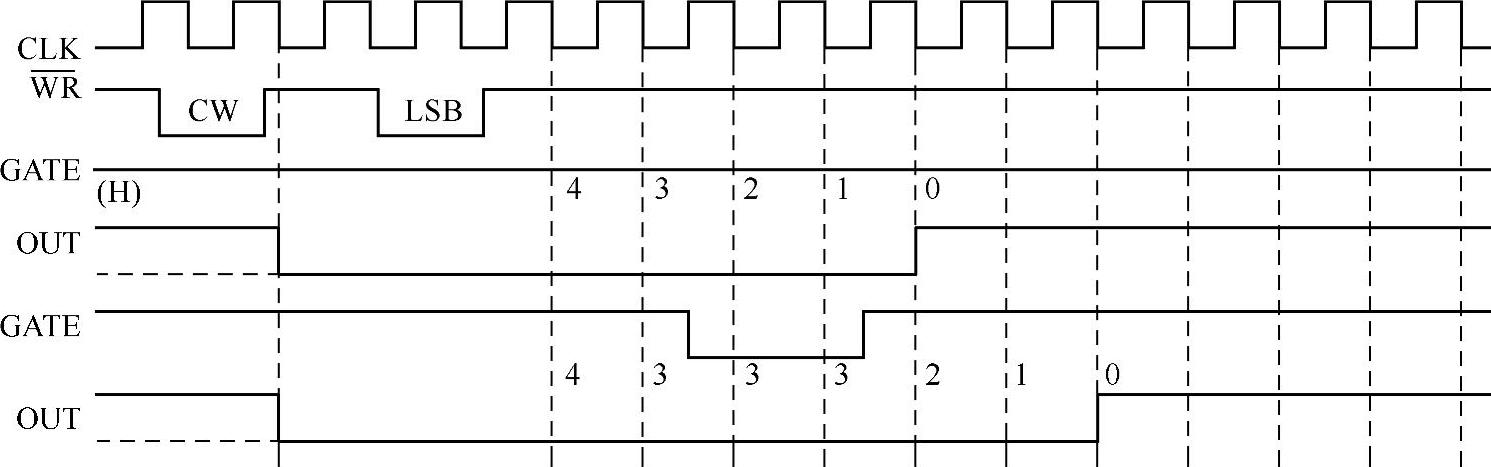

方式0的特点是计数到终点输出变为高电平。当将某计数器设置成方式0后,其输出OUT变低电平,装入初值后,仍保持低电平。门控为高电平开始计数。每来一个计数脉冲CLK,计数器的值减1,当计数到达终点即计数器的值变成0时,OUT变为高电平。在计数期间可用门控信号暂停计数(即门控为低电平时,计数暂停)。

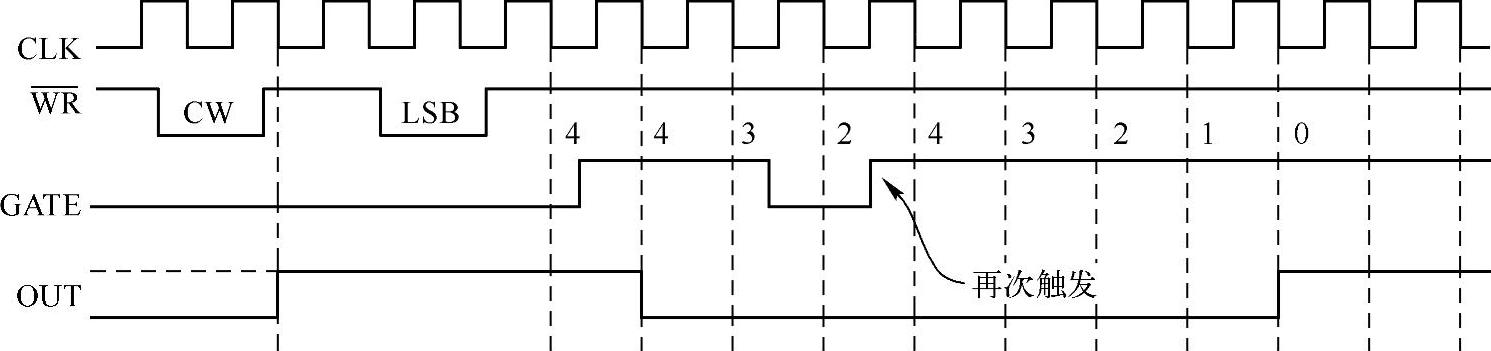

图8-24是方式0的波形示意图。其中/WR是表示初始化时执行输出指令所发的写信号,CW表示写控制字,LSB表示写计数初值(一般情况下,写初值应有两个负脉冲,第一个送低8位,第二个送高8位。这里是为了波形简洁,只画了一个,见图8-24)。

图8-24 方式0波形图

输出端OUT由低变高可以用来作为中断请求信号(正是由于这种作用,许多书中称方式0为完成计数时中断),也可作为查询信号,也可直接去控制某个操作。

2.方式1——硬件启动的单脉冲发生器

方式1通常被用作模拟单稳电路,所以又被称作可编程单稳。所谓单稳,是指这样的电路,它有两种状态,但只能稳定在一种状态。在一定的外界作用下,它能从这一种状态进入到另一种状态,但经过一定时间后,又自动恢复到原来的状态。这个时间参数一般是由外加电阻、电容的值决定的。8253的方式1就是模拟单稳电路,其处于非稳定状态的时间可通过程序进行设置。

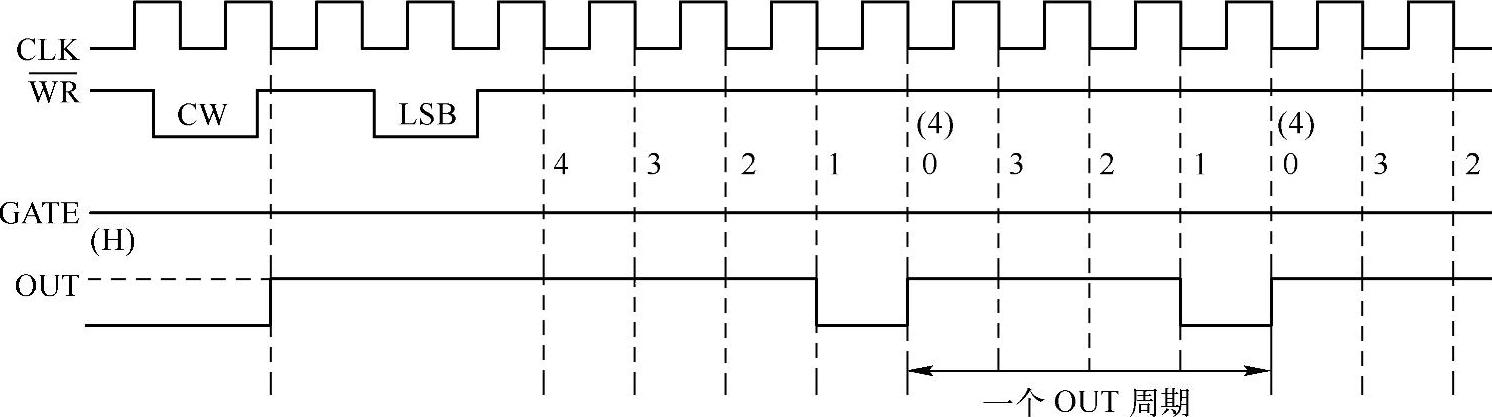

一旦8253的某计数器被设置成方式1后,其OUT变高电平,装入初值后,仍保持高电平,等待门控上升沿到来。门控为高电平后的第一个CLK下降沿时OUT变低电平,初值又被重新装入一次,并开始计数,每来一个计数脉冲,计数器的值减1。当减到0时OUT变高电平。此后门控的上升沿可再次启动此过程。方式1的波形如图8-25所示。

图8-25 方式1波形图

从图8-25可看出,门控上升沿的到来使得OUT开始输出负脉冲(称作触发),其宽度为CLK的周期乘以预置值。如果在负脉冲期间,即计数未到达终点,GATE再来一个上升沿,则再次赋初值,重新开始计数。这样做可加宽负脉冲的宽度,如图8-26所示。这种现象叫单稳的再触发。

图8-26 方式1下的单稳再触发

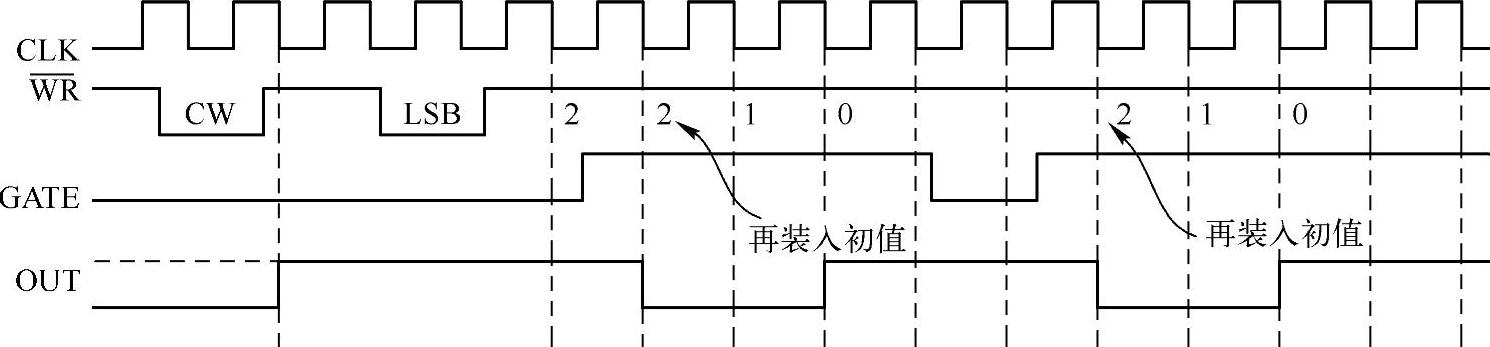

3.方式2——分频脉冲发生器(分频器)

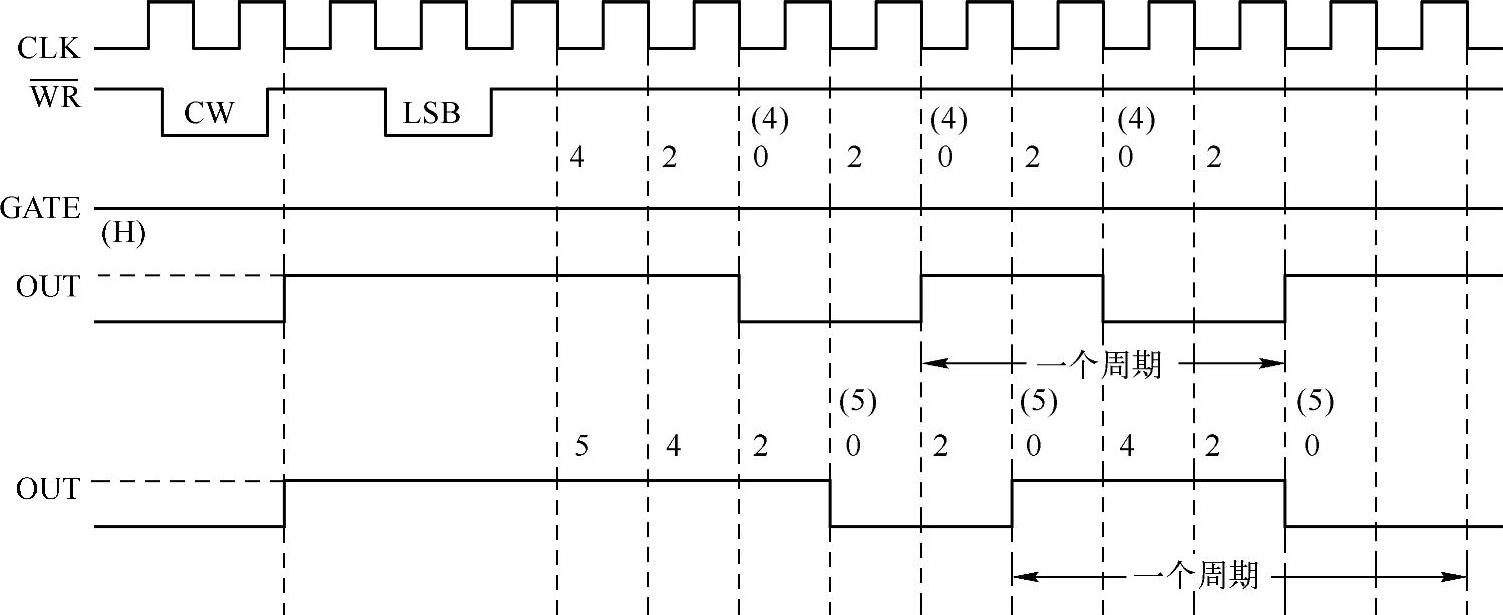

方式2用来对输入脉冲(即计数脉冲CLK)N分频(N为预置的初值),在输出信号周期中低电平的时间为一个CLK周期。

设置此方式后,OUT变高电平,装入初值后便自动开始计数,减到1时OUT变低电平。经过一个CLK周期,OUT恢复高电平,且计数器又自动装入初值,重新开始计数,并如此循环下去。如图8-27所示是工作在方式2的示意图。在上述过程中GATE应一直保持高电平。若GATE变低电平将禁止计数,并使输出为高电平。在GATE再次变高电平时,计数器将重新装入预置的初值,并开始计数。(https://www.xing528.com)

图8-27 方式2波形图

4.方式3——方波发生器

方式3类似于方式2,输出是周期性的,不同的是方式3输出方波。如果预置的初值N为偶数,则输出周期中高电平和低电平的宽度相等。如果N为奇数,则输出周期中高电平比低电平多一个CLK周期的时间,当N相当大时,也可认为是方波。当然,一般采用方式3时,置初值为偶数。

设置成方式3后,OUT变高电平,装入初值后便自动开始计数。如初值为偶数,每个CLK使计数器减2,计数到终点改变电平。如初值为奇数,则输出为高电平时第一个CLK使计数器减1,随后每个CLK使计数器减2。输出为低电平时第一个CLK使计数器减3,随后每个CLK使计数器减2。每当计数到终点都会改变电平,初值又被重新装入,并开始计数。如此循环下去,如图8-28所示。和方式2一样,GATE变低可暂停计数。

图8-28 方式3波形图

5.方式4——软件触发的单脉冲发生器

设置成方式4后,OUT变高电平,写入计数值后自动开始计数(所以称为软件触发),计数到终点输出一个CLK周期的低电平脉冲。GATE变低可暂停计数,用GATE的上升沿可重新赋初值,并开始计数。

6.方式5——硬件触发的单脉冲发生器

设置成该方式后,OUT变高电平,写入计数值后需等待GATE上升沿的到来才开始计数(所以称为硬件触发)。计数到终点也输出一个CLK周期的低电平脉冲。计数过程中不受GATE电平的影响。此后,用GATE的上升沿可重新赋初值,并开始计数。

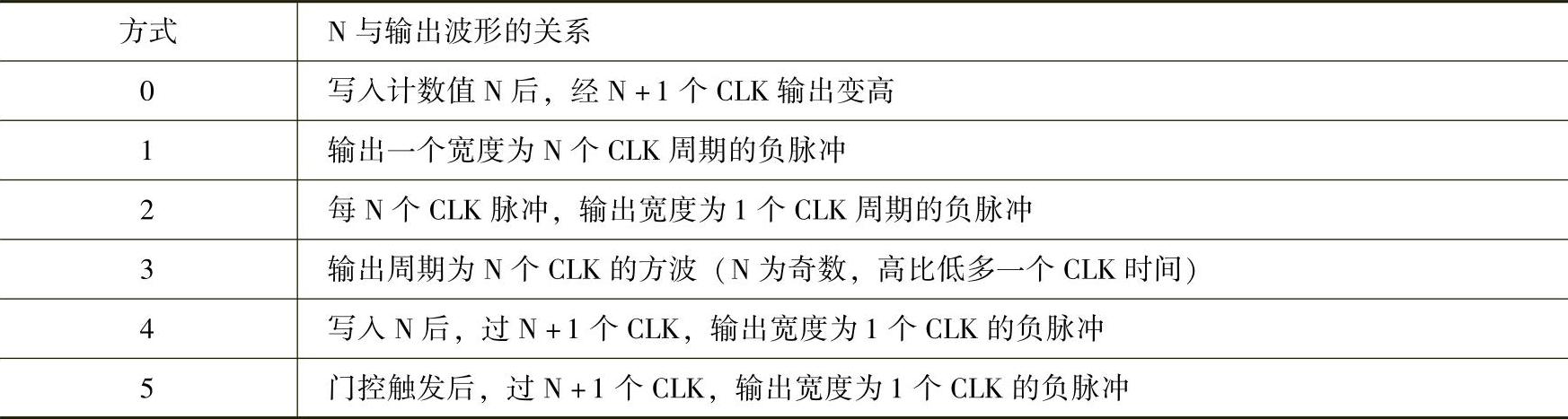

下面对8253/8254的6种工作方式做简单比较,找出它们的共性和个性。

1)在六种工作方式中,只有方式0在写入控制字后OUT变为低电平,其他5种方式都在写入控制字后OUT输出高电平。

2)预置值N与输出波形的关系见表8-3。表中几处“N+l”里的加1是考虑到预置的初值需要一个计数脉冲才能装入。当然,对其他方式初值的装入也都需要一个CLK脉冲,只是这一个CLK在输出中不必加以考虑,因为方式1要考虑的是单稳负脉冲的宽度,而方式2、3初值的装入只影响第一个周期。

3)方式2、4、5有相同之处,即计数到终点,都输出宽度为1个CLK周期的低电平脉冲。其主要不同点为:方式2是自动启动,重复进行计数及输出低电平脉冲的过程;方式4也是自动启动,但仅输出一个低电平脉冲;方式5需等待GATE上升沿的到来才开始计数,也只输出一个低电平脉冲。

表8-3 预置值N与输出波形的关系

4)方式2和方式3也有相同之处,即都输出周期性信号,每当计数到终点,初始化时预置的初值都会被自动重装。两者的不同之处在于输出的周期性信号具有不同的占空比。

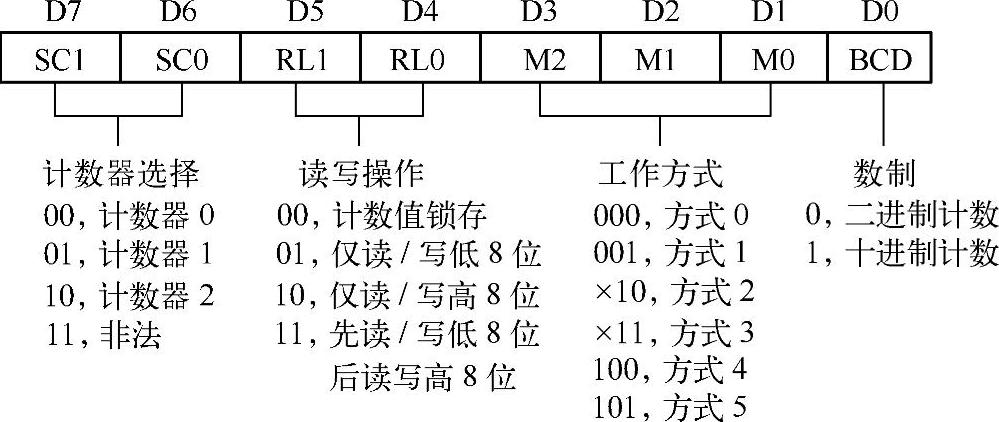

8253/8254只有一个控制字,用于控制三个计数器的工作方式和计数方式,其格式和含义如图8-29所示。最高两位用来选择计数器,接着的两位用来规定读/写格式,其后的3位用来选择工作方式,最低位用来规定是二进制计数还是十进制计数(BCD数制)。

图8-29 8253/8254控制字

由于8253对外的数据线只有8根,对16位计数器进行写(预置)或读(读取当前计数值)需要分两次进行。当CPU需要读取某计数器的当前值时,一般是先读低8位,再读高8位。由于两次读之间存在时间间隔,这期间可能恰好有计数脉冲,所以读出的值带有随机性。为了使CPU能获得计数器某一时刻准确的值,8253/8254设置了锁存操作。当控制字的D5、D4位(RLl、RL0)为00时,表示锁存,即将指定计数器的当前值锁存到内部的16位存储寄存器中。此后,CPU可分两次取走。注意,锁存不影响计数,在锁存操作时计数器仍然继续计数,CPU读取的是被锁存在存储寄存器中的计数值。

使用8253,要先通过程序对其进行初始化。在初始化时主要掌握以下三点:

1)对各个计数器分别进行初始化,顺序无要求。

2)对某个计数器进行初始化,先写控制字,再送计数初值。如送16位初值,则需先送低8位,再送高8位。

3)预置的初值需经过一个输入脉冲(CLK)的上升沿和下降沿之后才可装入计数器。

4)根据需要选择计数数制,如果计数初值大于10000,则只能使用二进制计数(16 bit的BCD技术最大值只有9999)。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。