从功能上来讲,微型计算机的外围设备接口(有时简称为外设接口或接口)是连接微机和外围设备之间的桥梁。由于微型计算机可以连接的外设种类非常繁多,其功能、结构上的差别非常大,处理数据的种类和速度也相差甚多。例如,在处理数据的种类上,外设可能会面对语音、图像、视频、压力、速度等模拟量,也可能会面对各种不同类型的数字信号,来自鼠标、调制解调器的串行数字信号、送往行式打印机的并行数字信号等。在处理数据的速度上,可能低到键盘、针式打印机的每秒钟几个到几十个字符,也可能高到一些高速通信设备和大容量存储设备的每秒几十、几百M字节甚至更高的传输速率。面对这些差别,外设接口必须将它们统一起来,并提供外设与微处理机之间的数据通路和控制能力。这就必须解决三个主要的问题。一是接口与微处理器或系统总线之间的连接,从而允许微处理器访问外设接口;二是接口与设备之间的连接和控制,从而使得微处理器能够通过接口访问和控制外设;三是外设与微处理器之间的信号/代码转换,即在外设所提供或能够使用的不同种类的信号(包括模拟信号、数字信号、串行信号、并行信号等)和微处理器能够识别和提供的二进制数字代码之间提供一座互相转换的桥梁。

为了提供相应的功能来解决这三个问题,外设接口一般由三个部分组成:系统总线接口电路、设备接口电路、信号转换与匹配电路。系统总线接口电路由一系列与系统总线或微处理器相连接的部件和信号组成,其结构和功能比较一致。对于绝大多数的设备接口,系统总线接口电路部分通常包括一组锁存器、缓冲器和寄存器,以及用于通过I/O命令访问这些寄存器的信号,如片选信号、读/写信号、低位地址信号(用于选择读/写哪些寄存器)等。对于某些使用到中断、DMA等功能的设备接口还要提供中断请求信号、DMA请求信号及其控制电路。相比起来设备接口电路和信号匹配电路就要复杂得多了,不同种类和不同功能的设备对接口电路所提供的信号和控制规程上的需求大相径庭,所以不同的设备接口在这两个部分上的差别也非常大。除此之外,外设接口还经常需要一个内部数据总线来提供内部的数据通路,以及一组用来控制整个接口正常工作的控制逻辑。它们和上面所提到的系统总线接口电路、设备接口电路、信号转换与匹配电路一起,组成了外设接口。

由于外设处理速度的巨大差别,微处理器和外围设备之间很难同步工作,所以微型计算机中的外围设备通常使用与微处理器异步的工作方式。为了实现这种异步的工作方式,外设接口就必须负责提供用于控制异步工作的各种信号和寄存器,并在这些信号和寄存器之间实现合理的逻辑关系。例如,外围设备一般要提供一个用于反映接口工作状态的寄存器,该寄存器的内容应当与外设当前是否可以与微处理器进行数据交换的“设备准备好”信号相关联,通过读取该寄存器的内容,微处理器就可以判断当前外设是否已经准备好,以决定是否可以进行数据传输。例如,对于输出设备,当设备已经准备好接收下一组数据时,微处理器可以通过读取该信号得知设备当前是否空闲,从而将下一组要输出的数据传送给设备;对于输入设备,当设备已经将要传递给微处理器的数据准备好时,也可以通过该信号通知CPU,要求CPU读取设备准备好的数据。由于这个寄存器反映的是设备当前的状态,所以经常被称作“状态寄存器”。

在提供状态寄存器的同时,输入/输出接口还必须提供一组寄存器来实现数据的实际输入/输出,这些寄存器一般被称作数据寄存器。由于输入/输出设备和微处理器之间的速度差距,数据寄存器经常需要对输入/输出的数据进行锁存或缓冲,从而避免总线上的数据变化和外设中的数据变化之间的互相干扰。除此之外,设备接口还要提供一些用于控制设备及设备接口动作的寄存器,这些寄存器通常情况下与设备接口的控制电路相连,被称作控制寄存器。无论状态寄存器、数据寄存器还是控制寄存器通常都占用I/O地址空间,被微处理器通过I/O命令访问。在某些特定的设备中,状态寄存器对应的状态信号有时也被作为中断请求或DMA请求信号使用,从而使得设备可以以中断或DMA方式进行数据传输和控制。

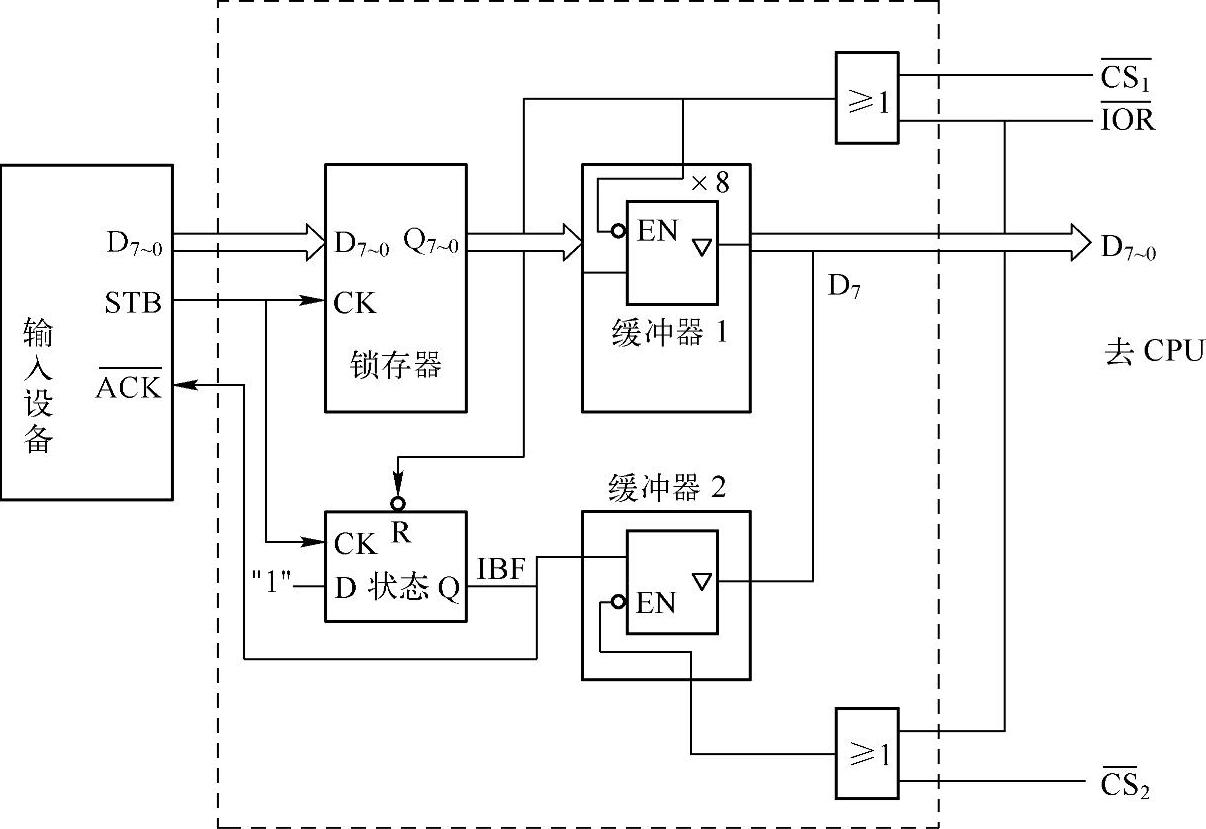

图8-1给出了一个异步输入接口的原理性实现(虚线框内)。在该实现中,由于输入设备提供的输入数据和微处理器需要的数据格式相同,所以接口电路没有提供信号转换功能。该接口的核心由一个用于锁存输入数据的锁存器、一个用于表示输入缓冲器当前状态的D触发器和两个用于与微处理器交换数据的三态缓冲器,并通过两个或门来实现对这些缓冲器的读出控制。

图8-1 输入接口的原理

在输入设备完成了一组数据的输入时,这些数据将被放置在其D7~0引脚上,同时数据选通信号STB由低电平变为高电平,从而触发锁存器的锁存动作,将设备放置在D7~0引脚上的数据锁存。同时,STB由低电平向高电平的跳变也会引起D触发器的状态变化,将加在其D引脚上的“1”信号设置到触发器中。经过这一系列动作,当STB由低电平跳变为高电平后,锁存器的Q7~0为输入设备给出的数据,D触发器的输出Q为1,表示输入数据已就绪,可以被读出(用信号IBF——“输入缓冲区满”表示)。

从处理器的角度来看,这个输入接口包括两个片选信号 和C

和C ,这两个信号分别与IOR信号相“或”之后控制两个数据缓冲器,代表了对两个不同地址的I/O读操作。其中

,这两个信号分别与IOR信号相“或”之后控制两个数据缓冲器,代表了对两个不同地址的I/O读操作。其中 用于控制缓冲器1,处理器对该端口的读操作将引起缓冲器1将锁存器锁存的数据送到总线上,从而读到输入的数据;

用于控制缓冲器1,处理器对该端口的读操作将引起缓冲器1将锁存器锁存的数据送到总线上,从而读到输入的数据; 用于控制缓冲器2,处理器对该端口的读操作将引起缓冲器2将D触发器的输出送到数据总线的D7位上,通过对该位的判断就可以知道输入接口中是否有数据可读。一般来讲,

用于控制缓冲器2,处理器对该端口的读操作将引起缓冲器2将D触发器的输出送到数据总线的D7位上,通过对该位的判断就可以知道输入接口中是否有数据可读。一般来讲, 所对应的I/O地址所访问的通常被称作数据寄存器,而

所对应的I/O地址所访问的通常被称作数据寄存器,而 所对应的I/O地址所访问的则被称作状态寄存器。(https://www.xing528.com)

所对应的I/O地址所访问的则被称作状态寄存器。(https://www.xing528.com)

由于这个输入接口没有连接中断请求和DMA请求,它只能以程序查询的方式进行数据传输与控制。具体的过程如下:微处理器反复读取 对应的I/O端口,并判断读入数据的D7位是否为1。如果该位为1,则代表输入端口中已经有一组数据可读,这时微处理器从CS1对应的I/O端口读入被锁存器锁存的输入数据,同时

对应的I/O端口,并判断读入数据的D7位是否为1。如果该位为1,则代表输入端口中已经有一组数据可读,这时微处理器从CS1对应的I/O端口读入被锁存器锁存的输入数据,同时 和IOR相“或”之后得到的负脉冲还会被送到D触发器的清零端,将D触发器中的内容清零,等待输入设备完成下一组数据的输入。与此同时,D触发器的零输出被送到输入设备的ACK端,通知输入设备可以准备下一组数据了。

和IOR相“或”之后得到的负脉冲还会被送到D触发器的清零端,将D触发器中的内容清零,等待输入设备完成下一组数据的输入。与此同时,D触发器的零输出被送到输入设备的ACK端,通知输入设备可以准备下一组数据了。

在这个输入端口中,并没有设计中断请求和DMA请求,其状态只能由CPU主动读取而不能通过中断将状态变化通知CPU,这就使得这个接口只能通过轮询的方式来控制。如果我们需要提供以中断方式控制外设接口的能力,则在接口电路中必须包括与中断请求相关的逻辑。

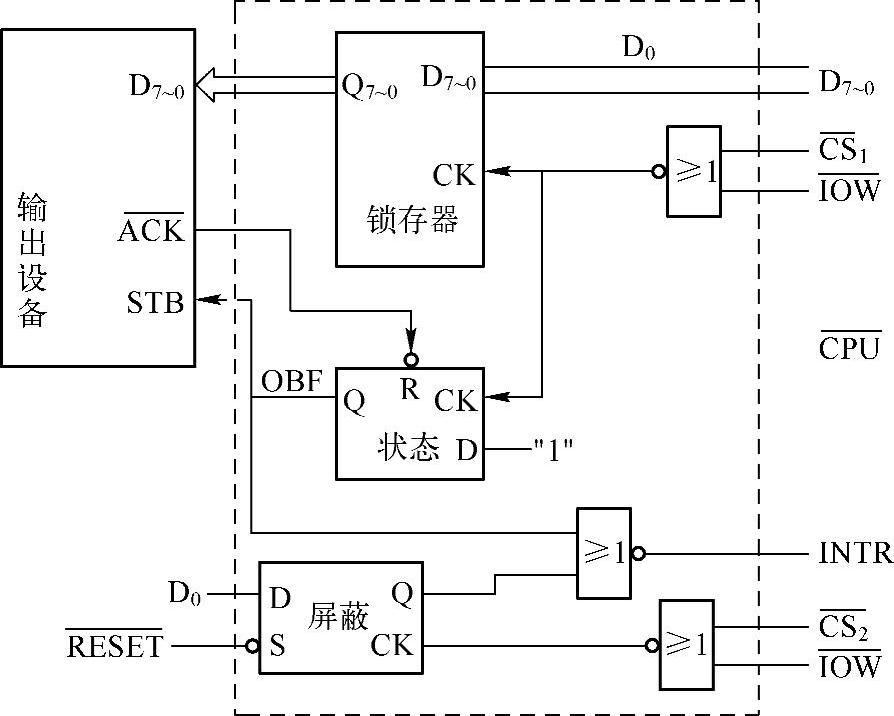

图8-2所示输出接口示例中就增加了中断请求电路。首先我们把注意力集中在数据输出的部分,微处理器将要输出的数据送到总线D7~0上,并通过 和

和 或操作产生的锁存器时钟信号,将数据锁存到锁存器中。与此同时,

或操作产生的锁存器时钟信号,将数据锁存到锁存器中。与此同时, 和

和 或操作产生的锁存器时钟信号也被送到状态D触发器中,将“1”设置到状态D触发器,从而使状态D触发器的输出(即OBF——输出缓冲区满)成为有效。这个OBF信号作为输出设备的选通信号STB交给输出设备,从而驱动输出设备将锁存器Q7~0引脚上的内容输出出去。当输出结束后,输出设备的ACK信号有效,状态D触发器被重置,OBF恢复为0。

或操作产生的锁存器时钟信号也被送到状态D触发器中,将“1”设置到状态D触发器,从而使状态D触发器的输出(即OBF——输出缓冲区满)成为有效。这个OBF信号作为输出设备的选通信号STB交给输出设备,从而驱动输出设备将锁存器Q7~0引脚上的内容输出出去。当输出结束后,输出设备的ACK信号有效,状态D触发器被重置,OBF恢复为0。

和图8-1不同的是,图8-2所示输出接口没有设置状态寄存器,那么CPU是根据什么来判断当前输出设备已经准备好,可以将数据输出给输出设备了呢?从图8-2中可以看到,状态D触发器输出的OBF信号不仅仅被作为输出设备的选通信号驱动输出设备,同时还通过一个与非门生成了INTR中断请求信号。也就是说,当OBF信号为0时,中断请求信号INTR将有可能有效,从而引起一次中断请求,向CPU报告“输出设备可用”的消息。这也是图8-2所示输出接口电路中不提供状态寄存器的原因。

在图8-2中,OBF信号不是直接作为INTR信号连接到中断请求线上的,其目的在于提供一种机制,使得程序可以通过I/O命令来允许或禁止该输出设备产生中断请求。由于IN-TR信号是由OBF和屏蔽D触发器的输出经过与非运算产生的,屏蔽D触发器的输出就可以起到一个开关的作用,允许或禁止输出设备通过OBF产生中断请求。另一方面,屏蔽D触发器的输入端连接到了D0,其时钟连接由 和

和 控制,程序就可以通过向

控制,程序就可以通过向 对应的I/O端口的最低位写入0或者1,来控制允许或禁止设备产生中断请求。这时,

对应的I/O端口的最低位写入0或者1,来控制允许或禁止设备产生中断请求。这时, 对应的I/O地址起到的是控制外设接口的作用,属于外设接口的控制寄存器。

对应的I/O地址起到的是控制外设接口的作用,属于外设接口的控制寄存器。

图8-2 带中断请求电路的输出接口

图8-1和图8-2中的接口电路仅仅是用于演示外设接口原理的两个例子,其功能和结构都比较简单。实际使用的外设接口提供的功能要远远多于这两个例子,其结构也要复杂得多。例如串行接口必须实现串行数据和并行数据之间的转换,数/模和模/数接口则必须实现数字信号和模拟信号之间的转换工作,相应地在接口电路中也必须设计能实现这些功能的电路。以下几节将介绍几种微机中常见的外设接口芯片的结构、功能与使用方法。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。