中断处理是处理器的重要能力,微处理器都要组成中断系统以实现对中断的处理。8086/8088处理器具有处理256种中断的能力。根据中断来源的不同,这256种中断被分成硬件中断和软件中断两大类。对于每一种中断,微处理器为其分配一个取值在0~255之间的类型码,常用INT n表示。

1.硬件中断和软件中断

中断被分成硬件中断和软件中断两大类,其中,硬件中断就是通过外部硬件电路产生的中断,因此又常被称为外部中断。硬件中断又可以分为可屏蔽中断和非屏蔽中断两类。

在8086/8088微处理器中,可屏蔽中断请求经INTR引脚输入,通知处理器一个外部事件需要被处理。但是处理器是否响应INTR引脚上的中断请求依赖于处理器状态寄存器中IF位的状态。如果IF=1,则中断请求被响应,这时称为“开中断”状态;如果IF=0,INTR引脚上的中断请求被屏蔽,处理器不对其响应,被称作“关中断”或“中断屏蔽”状态。INTR引脚一般连接到可编程中断控制器8259A的中断请求输出端,接收8259A提供的中断请求信号。

8086/8088的非屏蔽中断请求来自NMI引脚,不受IF状态位的限制。也就是说,只要NMI上出现了中断请求,处理器就一定响应并转向一个处理过程,系统不能屏蔽这个中断请求。非屏蔽中断一般用于电源掉电等紧急事件的处理。

除了来自处理器外部的硬件中断,程序执行过程中出现异常情况、处理器状态标志寄存器的特殊设置或执行某些特殊指令也将引起处理器的中断,这种中断称软件中断。软件中断又分为异常和陷入两种,程序执行过程中的异常情况称异常(Exception),而另外两种情况称陷入(Trap)。比如,当处理器运行过程中遇到除法指令中除数为0的时候,一个“除数为0”的异常就会产生;当标志寄存器TF位置位的时候,每条指令执行结束都会产生一个“单步中断”陷入,以用于程序的调试,等。

除了这些情况之外,微处理器还会在执行一条INT n的指令的时候发生软件中断,或者确切地说是“陷入”。这种陷入一般被用于对系统功能的调用。在8086/8088微处理器中,INT n指令中的n可以是0~255中的任何一个,当处理器执行到一条INT n指令的时候,一个n型中断就会自动被触发,从而使处理器自动转向n型中断的中断处理程序。类似的指令还有单字节断点中断INT3、溢出中断INTO等。软件中断的产生与处理不受中断允许标志位IF的限制。

2.中断向量与中断向量表

中断发生后,微处理器需要转移到一个特定的中断处理程序对中断进行处理,对应于不同的中断其处理程序也不同。微处理器需要一种机制来存储这些中断处理程序,在8086/8088微处理器中用于存储中断处理程序入口地址的机制就是中断向量表。

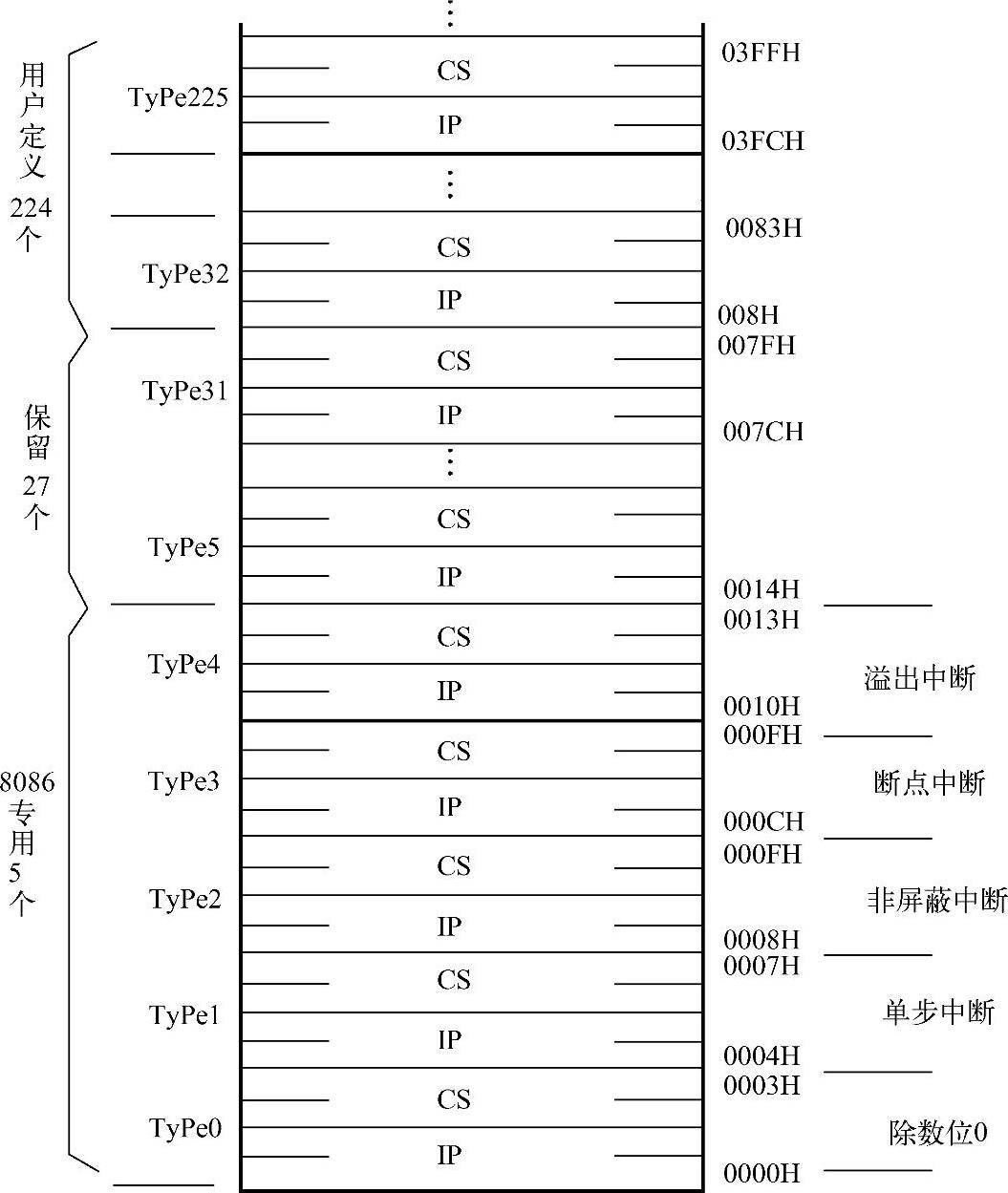

8086/8088微处理器把所有256种中断对应的中断处理程序的入口地址集中存放在存储器的起始区域,这个区域就称为中断处理程序入口地址表。中断处理程序的入口地址一般被称作“中断向量”,因而这个中断处理程序入口地址表也被称作“中断向量表”。按照8086/8088的存储器分段管理方法,每个中断向量需要用连续的4字节存储单元来存储,其中2个字节存储段地址,另2个字节存储段内偏移地址。其次序是:低地址的两个字节存储段内偏移地址,在中断发生需要处理时该地址被送到8086/8088的IP寄存器;高地址的两个字节存储段地址,在中断发生需要处理时该地址被送到8086/8088的CS段寄存器。这样,256个中断向量占据的内存单元为1024个字节,即1 KB(0:0~0:03FFH)。在这1024个字节中,每4个字节存放一个中断的中断向量,把一个中断的中断类型码(0~256)乘以4,就可以得到这个中断对应的中断向量在中断向量表中的首地址。例如,对于21H号中断,其中断向量存储于中断向量表中0:84H~0:87H这4个字节的存储单元中。图2-17给出中断向量表的示例。

在8086/8088的256种中断中,其前5种已经被8086/8088定义为专用中断,其他中断不能再使用这5个中断号。类型0中断为除数为0的异常;类型1中断称单步中断(陷入),即当标志寄存器中的TF=1时,处理器在执行每一条指令后即触发单步中断,执行类型1的中断处理过程,用于程序的调试过程。类型2中断被硬件的非屏蔽中断NMI所占据。类型3为断点中断,也被用于程序的调试过程。类型4为溢出中断,即当程序中遇到一条溢出中断指令INTO并且OF=1的时候触发该中断。类型5~类型31的中断被保留,中断32~255可以供用户使用。

(https://www.xing528.com)

(https://www.xing528.com)

图2-17 8086/8088中断向量表

3.8086/8088中断响应周期

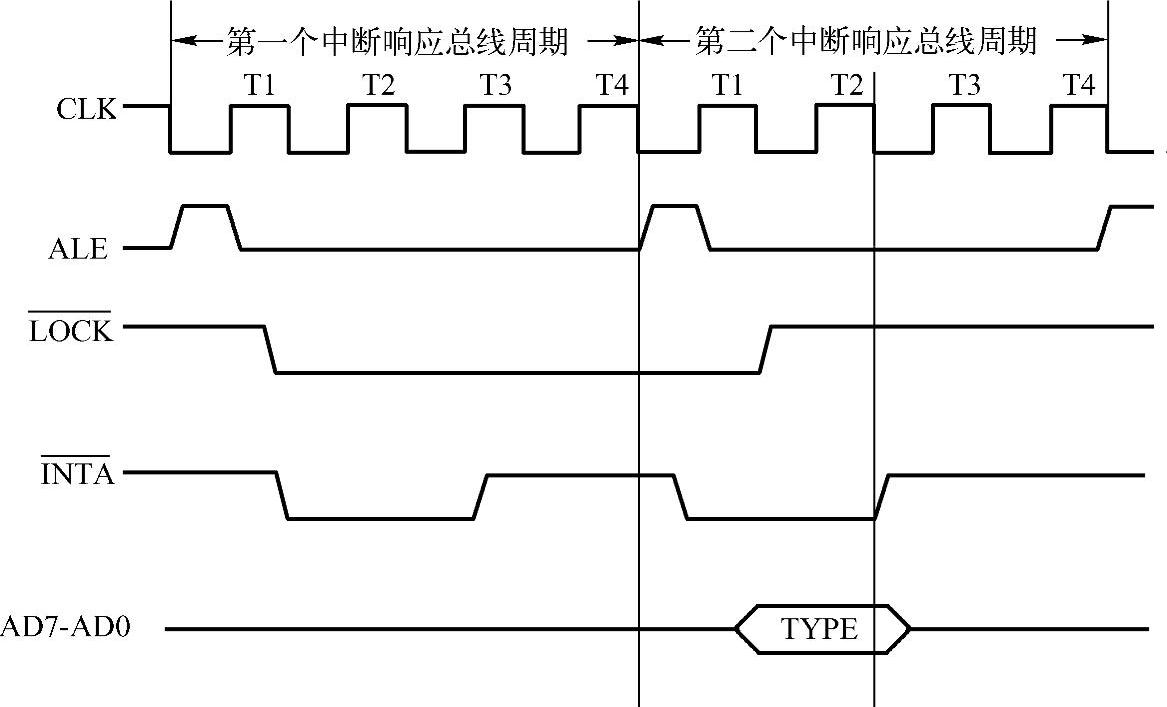

当处理器的INTR引脚上出现一个高电平时,说明外部有一个可屏蔽的中断请求需要8086/8088响应,如果此时处理器的中断允许标志位IF=1,在执行完当前指令的时候,处理器就开始响应外部的中断请求,进入中断响应周期(见图2-18)。具体步骤如下。

1)处理器的 引脚在两个总线周期内分别发出一个负脉冲(T2~T4),用于表示中断请求已经被响应。在第一个总线周期,处理器将地址/总线引脚置为高阻态(浮动),等待在第二个总线周期的

引脚在两个总线周期内分别发出一个负脉冲(T2~T4),用于表示中断请求已经被响应。在第一个总线周期,处理器将地址/总线引脚置为高阻态(浮动),等待在第二个总线周期的 信号使外部中断源(一般是中断控制器)将一个字节的中断类型码送到地址/数据复用总线上。这个中断类型码将被处理器读取,放入内部暂存器。

信号使外部中断源(一般是中断控制器)将一个字节的中断类型码送到地址/数据复用总线上。这个中断类型码将被处理器读取,放入内部暂存器。

2)处理器进入中断处理操作。首先保存处理器现场,将标志寄存器内容推入堆栈,清除IF和TF标志位以禁止对可能发生的单步中断和可屏蔽中断的响应;将下一条要执行的指令地址(当前的CS:IP)推入堆栈,以便中断处理结束后回到当前正在执行的指令继续执行。

3)处理器根据读入的中断类型码计算出中断向量的地址,并将中断向量地址装入CS:IP,进入中断响应服务程序。中断响应服务程序将以一条IRET指令结束,恢复处理器现场,继续执行中断发生时正在执行的程序。

图2-18 中断响应周期时序

在中断响应周期里面,8086/8088对于总线请求是不予响应的,以保证中断响应过程的正确性。具体来讲,在最小模式下,整个中断响应周期中8086/8088都不会响应总线请求。而在最大模式下,处理器从第一个中断响应周期的T2到第二个中断响应周期的T2之间使 信号输出有效电平,以通知外部逻辑该期间总线不允许被其他总线主设备使用。

信号输出有效电平,以通知外部逻辑该期间总线不允许被其他总线主设备使用。

需要注意的是,以上中断响应周期的描述仅对于外源性的硬件中断有效,对于内源性的软件中断,包括异常和陷入,由于处理器已经从执行的指令或标志位的状态中显式或隐式地得到了中断的类型码,处理器不再需要在总线上实施中断响应周期,而直接进入上述描述的步骤2)。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。