采用并行三总线扩展存储器、I/O端口或其他并行器件时,数据线、地址线从低位开始一一对应连接,片选线一般从最高位地址线开始依次连接到各个芯片上。如果扩展的是数据存储器(SRAM),则其器件的读、写信号(OE、WE引脚)应分别与单片机的RD、WR信号连接。而扩展的程序存储器(EPROM)要求只能读、不能随意写,其芯片的OE与单片机的RD信号连接,芯片的PGM引脚平时悬空,只有在编程时才连接单片机的PROG编程信号。

在对器件的地址空间分配时,按连接在器件芯片上的地址线和片选译码线来计算地址空间,编址方法如下:

1)基本地址计算:把连接到芯片地址端上的地址线从小到大计算出基本地址范围。计算地址时按二进制数从0开始编址,一直编到最大(即全1)。若芯片地址线有n根,则最大编址数为2n个地址,编址范围为(0~2n-1)。

2)加权地址计算:把连接到器件片选端上的片选译码地址线作为加权地址,其值根据引脚功能固定为0或1(存储器的片选控制信号一般为0有效)。

3)空地址线处理:未使用的地址线悬空,其值可以任意(全为0或1),即成为浮变随意地址。

4)将加权地址+浮变地址,再叠加到基本地址的高位上,得出器件的地址范围。

有了这些规则后,就很容易计算出外部扩展器件的地址空间。(https://www.xing528.com)

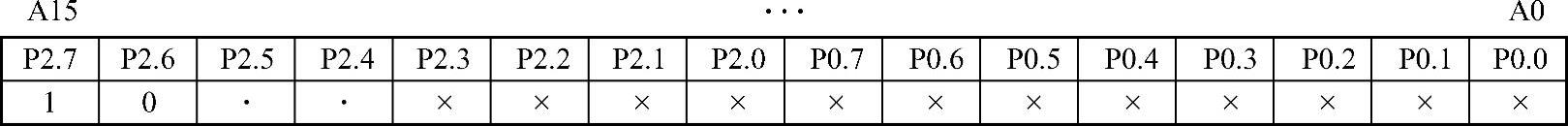

【例12-1】 假定一个系统扩展了两个芯片(IC1、IC2),其地址线连接关系如图12-3所示,其中“·”表示未用地址线,“×”表示连接了芯片的基本地址线,最高两位的值固定,是芯片的片选译码信号。设IC1片选端连接P2.7,IC2的片选端连接P2.6,片选线的有效值分别为1和0。要求计算这两个芯片的地址范围。

图12-3 扩展存储器地址连接图

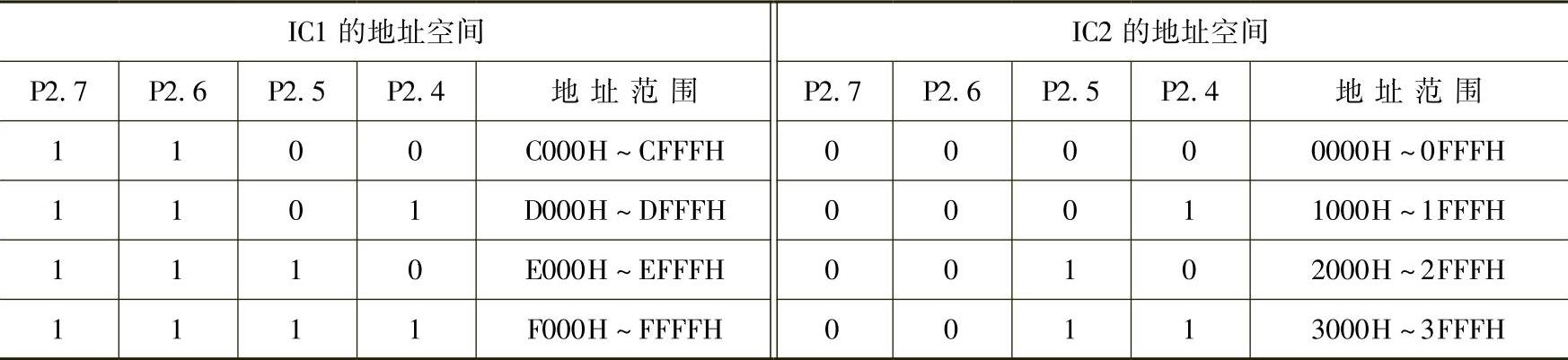

要计算此地址的范围,需要了解的是单片机一次只能访问一个芯片。因此,当IC1有效时(P2.7=1),IC2应无效(P2.6=1);当IC2有效时(P2.6=0),IC1应无效(P2.7=0)。同时,P2.5、P2.4是未用悬空地址线,可以作为0或1计算;基本地址线12根,则基本地址为0000~0FFFH,加权地址线4根(在高4位),只要把加权的片选译码地址叠加到基本地址上就能够计算出芯片地址。分配给IC1、IC2的地址空间见表12-1。

表12-1 IC1和IC2的地址空间

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。