SPI通信时,主机控制从机的SS=0,主机给SPDAT寄存器写入数据并从主机的MOSI信号线移出、送到从机的MOSI信号线;同时,写入从机SPDAT寄存器的数据从MISO信号线移出、送到主机的MISO信号线引脚,相当于数据在主机与从机之间交换。一个字节传输完后,SPI时钟发生器停止,置SPIF=1,产生SPI中断请求。

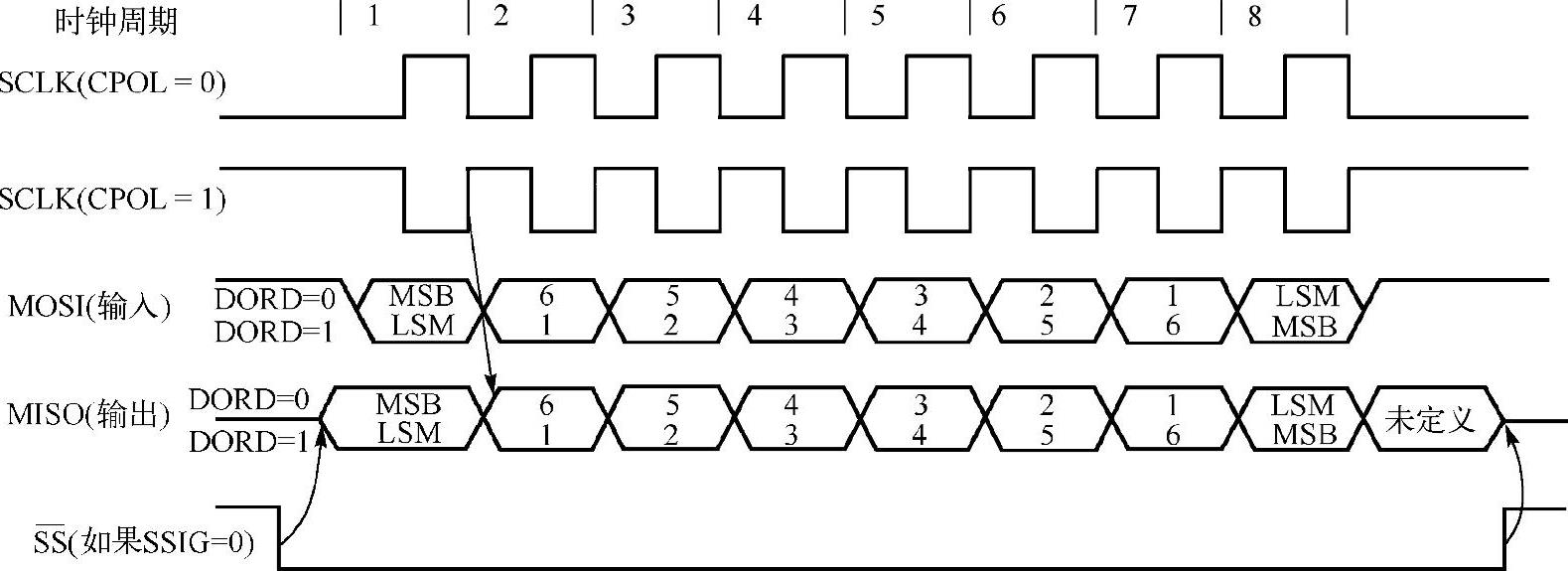

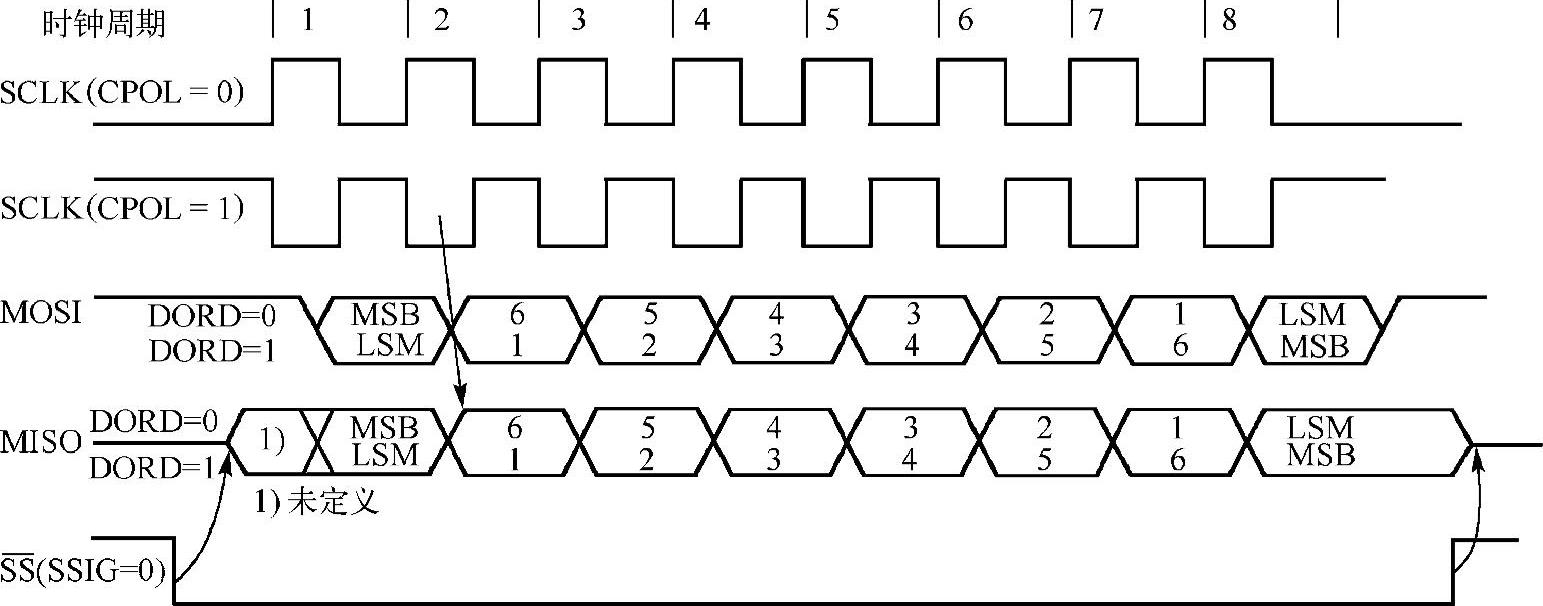

1.SPI从机传输模式

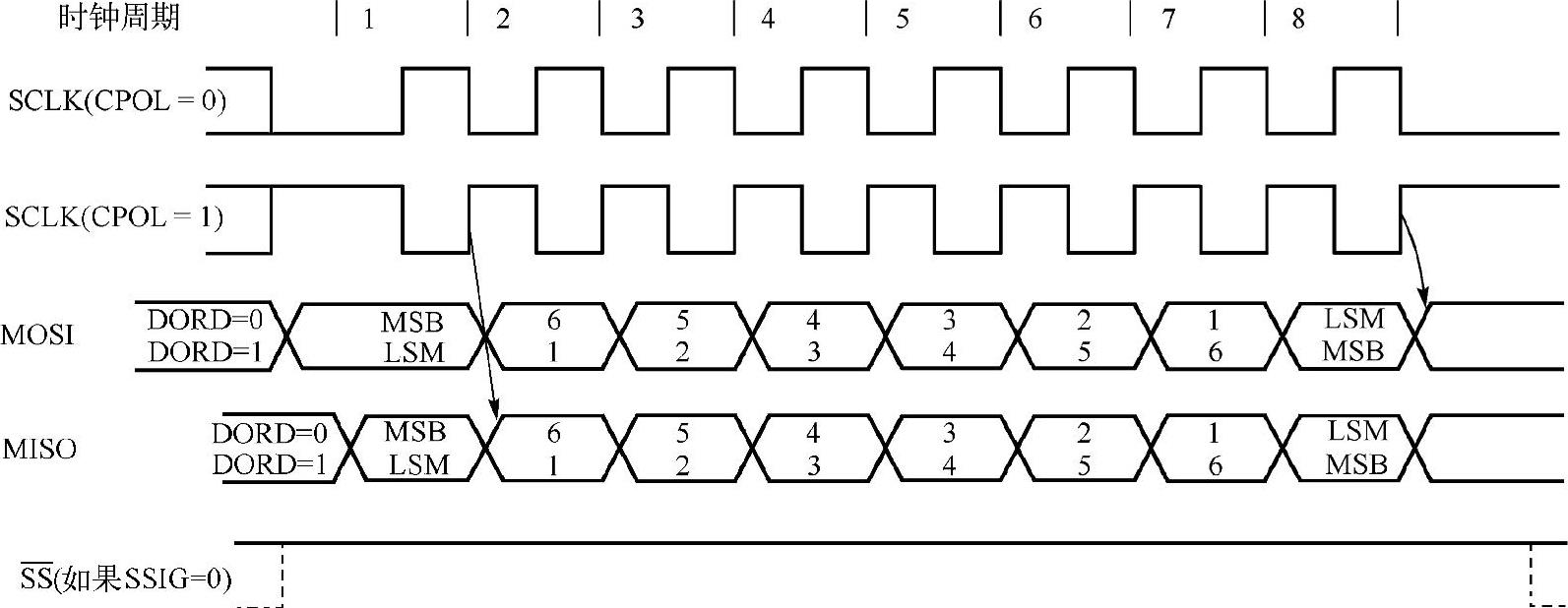

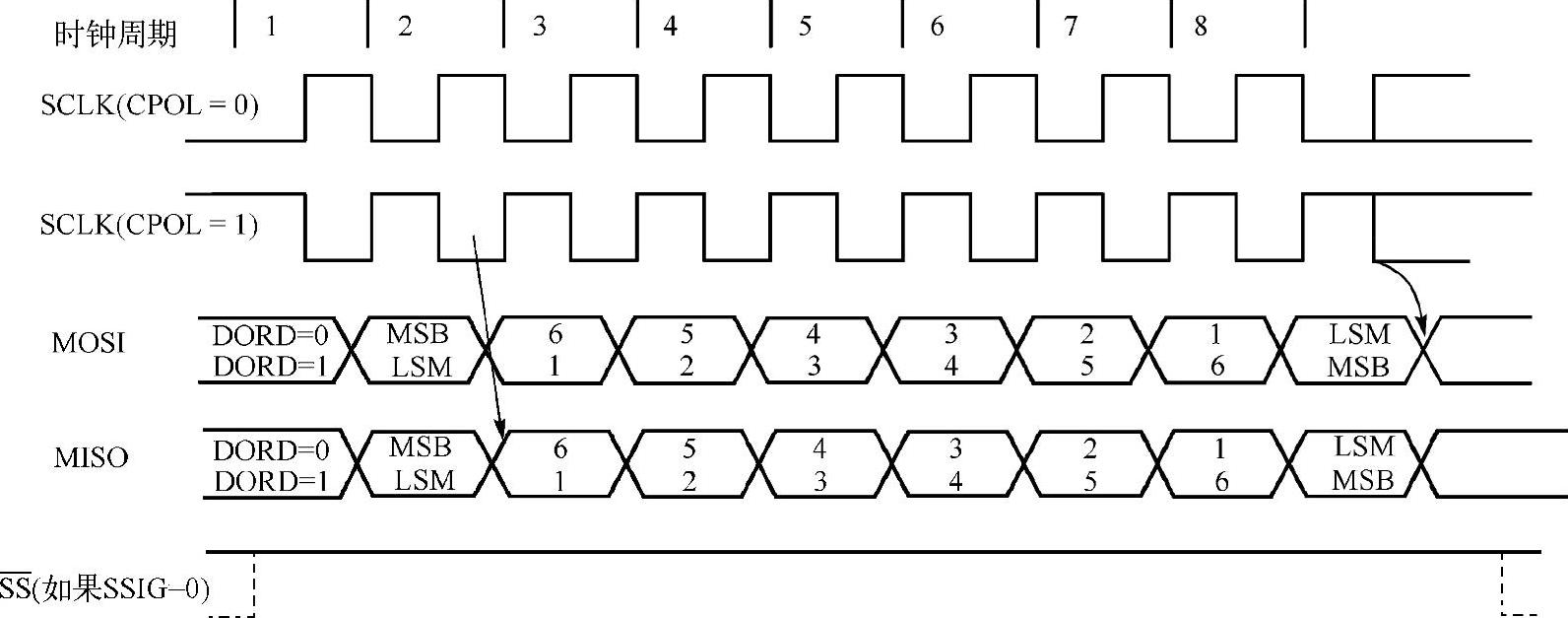

SPI在发送时为单缓冲,在接收时为双缓冲。这样在前一次发送未完成之前,不能将新的数据写入SPDAT。在接收数据时,数据将自动移入缓冲器,必须在后一个数据接收移入之前取出前一个数据,否则,前一个数据将被丢失。SPI数据通信时序如图9-5~图9-8所示。

图9-5 SPI从机传输模式(CPHA=0)

图9-6 SPI从机传输模式(CPHA=1)

图9-7 SPI主机传输模式(CPHA=0)

在使用SPI进行数据传输时,SCLK传输同步时钟:若CPOL=0,数据高电平开始发送,下降沿发送完毕;若CPOL=1,数据低电平开始发送,上升沿发送完毕。

MOSI、MISO是数据传输线:若DORD=0,从高位(MSB)开始传输数据,每个时钟传送1位,直到最低位(LSB);若DORD=1,从低位(LSB)开始传输数据,每个时钟传送1位,直到最高位(MSB),一帧传输完毕;(https://www.xing528.com)

图9-8 SPI主机传输模式(CPHA=1)

2.SPI主机传输模式

SPI接口的时钟信号线SCLK有Idle和Active两个状态:Idle指在不进行数据传输时或数据传输完成后SCLK所处的状态;Active与Idle是相对的一种状态。

时钟相位(CPHA)允许用户设置采样和改变数据的时钟边沿;时钟极性位(CPOL)允许用户设置时钟极性:

如果CPOL=0,则Idle=0,Active=1。

如果CPOL=1,则Idle=1,Active=0。

从Idle状态转变到Active状态,称为SCLK的前沿,从Active状态转变到Idle状态,称为SCLK的后沿。一个SCLK前沿和后沿构成一个时钟周期,一个SCLK时钟周期传输1位数据。

主机总是在SCLK=Idle状态时把要发送的数据送入到MOSI数据线上。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。