一般的时序信号产生器由时钟源、环形脉冲发生器、节拍脉冲和读写时序译码逻辑、启停控制逻辑等部分组成。

1.时钟源

时钟源用来为环形脉冲发生器提供频率稳定且电平匹配的时钟脉冲信号。它通常由石英晶体振荡器和与非门组成的正反馈振荡电路组成,其输出送至环形脉冲发生器。

2.环形脉冲发生器

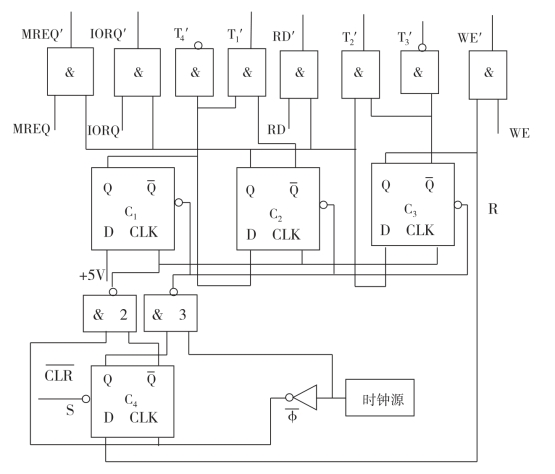

环形脉冲发生器的作用是产生一组有序的间隔相等或不等的脉冲序列,以便通过译码电路来产生最后所需的节拍脉冲。环形脉冲发生器通常采用循环移位寄存器形式,如图5-17所示。

图5-17中,我们假定时钟源输出5MHz(脉冲宽度200ns)的时钟信号。当CPU发出总清信号![]() 使触发器C4置1时,门3打开,第一个正脉冲φ通过门3使触发器C1、C2、C3清0。经过半个主脉冲周期(100ns)的延迟,触发器C4由1状态翻到0状态,再经过半个主脉冲周期的延迟后,第二个正脉冲的上升沿(即第一个

使触发器C4置1时,门3打开,第一个正脉冲φ通过门3使触发器C1、C2、C3清0。经过半个主脉冲周期(100ns)的延迟,触发器C4由1状态翻到0状态,再经过半个主脉冲周期的延迟后,第二个正脉冲的上升沿(即第一个 的后沿)作移位信号,使触发器C1、C2、C3变为“100”状态。此第二个

的后沿)作移位信号,使触发器C1、C2、C3变为“100”状态。此第二个 、第三个

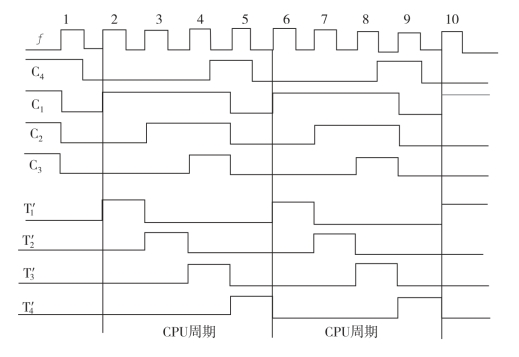

、第三个 连续通过门2形成移位信号,使C1、C2、C3相继变为“110”“111”状态。其过程如图5-18所示。当C3变为“1”状态时(对应第4个正脉冲),其状态便反映到触发器C4的D端,因而在第4个正脉冲的下降沿时又将C4置“1”,门3再次打开,第5个正脉冲便通过门3形成清“0”脉冲,将触发器C1、C2、C3清零。于是下一个循环再度开始。图5-18中的C1、C2、C3、C4被称为环形脉冲信号。

连续通过门2形成移位信号,使C1、C2、C3相继变为“110”“111”状态。其过程如图5-18所示。当C3变为“1”状态时(对应第4个正脉冲),其状态便反映到触发器C4的D端,因而在第4个正脉冲的下降沿时又将C4置“1”,门3再次打开,第5个正脉冲便通过门3形成清“0”脉冲,将触发器C1、C2、C3清零。于是下一个循环再度开始。图5-18中的C1、C2、C3、C4被称为环形脉冲信号。

图5-17 环形脉冲发生器

图5-18 环形脉冲发生器与译码逻辑

3.节拍脉冲和读/写时序的译码

如图5-17所示,图中的上半部示出了节拍脉冲和读/写时序的译码逻辑。假定在一个CPU周期中产生4个等间隔的节拍脉冲,那么其译码逻辑可表示为

(https://www.xing528.com)

(https://www.xing528.com)

其中,∧表示逻辑与运算。如图5-18所示,节拍脉冲T1′~T4′的脉冲宽度均为200ns,因此一个CPU周期便是800ns,在下一个CPU周期中,它们按固定的时间关系,重复T1′~T4′的先后次序,以供给机器工作所需的原始节拍脉冲。

读写时序信号的译码逻辑表达式为

RD′=C2∧RD WE′=C3∧WE

MREQ′=C2∧MREQ IORQ′=C2∧IORQ

其中,RD′、WE′和MREQ′信号配合在一起进行内存的读/写操作,而RD′、WE′和IORQ′信号配合在一起进行外围设备的读/写操作。而RD、WE、MREQ的IORQ是来自CPU的操作控制器的控制信号,它们都是持续时间为一个CPU周期的节拍电位信号。这就是说,读写时序信号RD′、WE′、MREQ′、IORQ′是受到控制的,它们只有在RD、WE、MREQ、IORQ信号有效后才能产生,而不像节拍脉冲T1′~T4′那样,一旦加上电源后就会自动产生。

4.启停控制逻辑

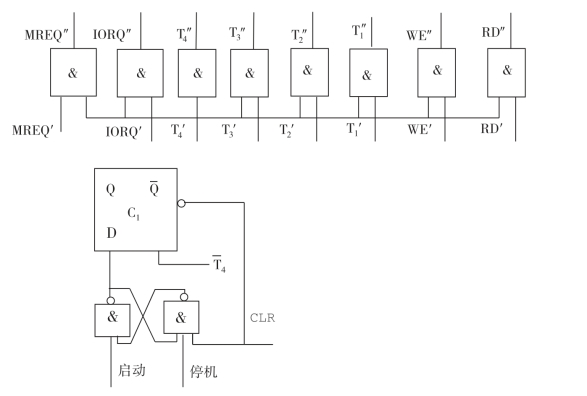

机器一旦接通电源,就会自动产生原始的节拍脉冲信号T1′~T4′。然而,只有在启动机器运行的情况下,才允许时序产生器发出CPU工作所需的节拍脉冲T1′~T4′。为此需要由启停控制逻辑来控制T1′~T4′的发送。同样对读写时序信号也要由启停逻辑加以控制。由于启动计算机是随机的,停机也是随机的,为此必须要求:当计算机启动时,一定要从第一个节拍脉冲前沿开始工作,而在停机时一定要在第四个节拍脉冲结束后关闭时序产生器。只有这样,才能使发送出去的脉冲都是完整的脉冲。一个简单的启停电路如图5-19所示。

图5-19 一个简单的启停控制电路

启停控制电路的核心是一个运行标志触发器Cr,当运行触发器为1时,原始节拍脉冲和读写时序信号T4′、T3′、T2′、T1′、WE′、RD′、MREQ′、IORQ′通过门电路发送出去,变成CPU真正需要的节拍脉冲信号T4′、T3′、T2′、T1′、WE′、RD′、MREQ′、IORQ′,反之,当运行触发器为0时,就关闭时序产生器。

在触发器Cr下面加上一个RS触发器,由启动和停机信号控制触发器Cr的D端,用![]() 作触发器Cr的时钟控制端,那么就能保证在T1′的前沿开启时序产生器,而在T4′的后沿关闭时序产生器。

作触发器Cr的时钟控制端,那么就能保证在T1′的前沿开启时序产生器,而在T4′的后沿关闭时序产生器。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。